- •Цель работы

- •Постановка задачи

- •1.1 Асинхронный счетчик

- •1.1 Таблица функционирования

- •2.1 Таблица функционирования

- •2.2 Функциональная схема синхронного счетчика

- •2.3 Моделирование синхронного счетчика

- •3.4 Код на vhdl, делитель частоты

- •3.5 Схема из rtl viewer

- •3.6 Моделирование кода

- •4.4 Код на vhdl

- •4.5 Схема из rtl viewer

- •4.6 Моделирование кода на vhdl

- •5. Заключение

2.2 Функциональная схема синхронного счетчика

На рисунке 8 представлена функциональная схема синхронного вычитающего счетчика.

Рисунок 8 – Функциональная схема синхронного, вычитающего счетчика

2.3 Моделирование синхронного счетчика

Моделирование представлено на рисунках 9, 10 в разных режимах работы.

Рисунок 9 – Моделирование, режим Timing

Рисунок 10 – Моделирование, режим Functional

Результаты моделирования полностью соответствуют значениям, представленным в таблице функционирования.

2.4 КОД НА HDL

Код, написанный на языке VHDL для синхронного, вычитающего счетчика представлен на рисунке 11.

Рисунок 11 – Код VHDL для синхронного счетчика

2.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисункt 12 представлена схема, собранная программой используя написанный код на VHDL.

Рисунок 12 – Схема из RTL VIEWER

2.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА ОПИСАННОГО НА HDL КОДЕ

На рисунках 13, 14 представлены результаты моделирования.

Рисунок 13 – Моделирование кода синхронного счетчика, Timing

Рисунок 14 – Моделирование кода синхронного счетчика, Functional

3. ДЕЛИТЕЛЬ ЧАСТОТЫ

3.1 РАСЧЕТЫ

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

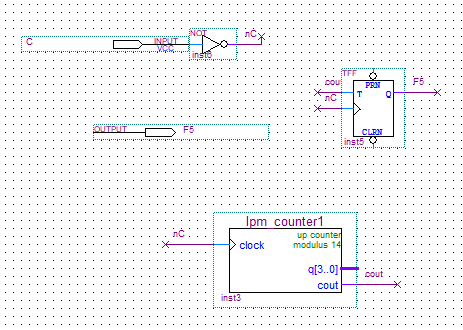

На рисунке 15 представлена функциональная схема делителя частоты.

Рисунок 15 – Делитель частоты, функциональная схема

3.3 МОДЕЛИРОВАНИЕ

Результаты моделирования устройства в режиме Timing представлены на рисунках 16, 17, 18, 19.

Рисунок 16 – Результаты моделирования, режим Timing, часть 1

Рисунок 17 – Результаты моделирования, режим Timing, часть 2

Рисунок 18 – Результаты моделирования, режим Timing, часть 3

Рисунок 19 – Результаты моделирования, режим Timing, часть 4

На рисунках 20, 21, 22, 23 представлены результаты моделирования в режиме Functional.

Рисунок 20 – Результаты моделирования, режим Functional, часть 1

Рисунок 21 – Результаты моделирования, режим Functional, часть 2

Рисунок 22 – Результаты моделирования, режим Functional, часть 3

Рисунок 23 – Результаты моделирования, режим Functional, часть 4

Результаты моделирования в Functional и Timing аналогичны и соответствуют ожидаемым – значит схема собрана правильно.

3.4 Код на vhdl, делитель частоты

Код для делителя представлен на рисунке 24.

Рисунок 24 – Код на VHDL, делитель частоты

3.5 Схема из rtl viewer

Схема из RTL VIEWER указана на рисунке 25

Рисунок 25 – Схема из RTL VIEWER, делитель частоты

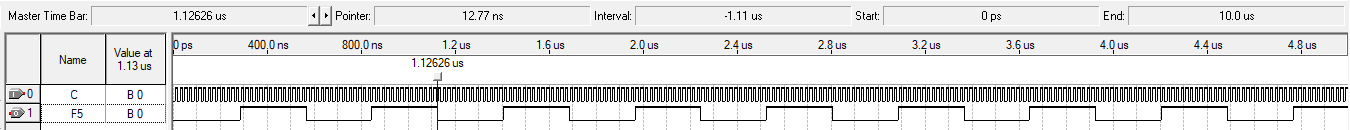

3.6 Моделирование кода

На рисунках 26, 27, 28, 29 представлены результаты моделирования схемы в режиме Timing.

Рисунок 26 – Моделирование кода для делителя частоты, Timing, часть 1

Рисунок 27 – Моделирование кода для делителя частоты, Timing, часть 2

Рисунок 28 – Моделирование кода для делителя частоты, Timing, часть 3

Рисунок 29 – Моделирование кода для делителя частоты, Timing, часть 4

На рисунках 30, 31, 32, 33 представлены результаты моделирования в режиме Functional.

Рисунок 30 – Моделирование кода для делителя частоты, Functional, часть 1

Рисунок 31 – Моделирование кода для делителя частоты, Functional, часть 2

Рисунок 32 – Моделирование кода для делителя частоты, Functional, часть 3

Рисунок 33 – Моделирование кода для делителя частоты, Functional, часть 4

Результаты моделирования в Functional и Timing аналогичны и соответствуют ожидаемым – значит схема собрана правильно.

4. СХЕМА ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ С ЗАДЕРЖКОЙ

4.1 РАСЧЕТЫ

4.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

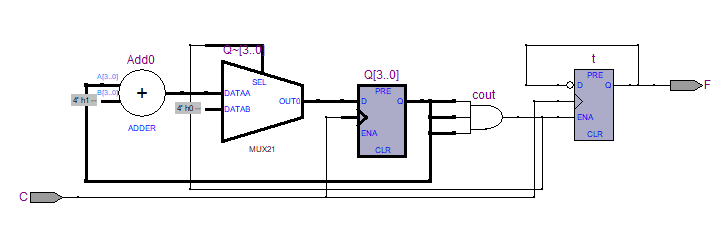

На рисунке 34 представлена функциональная схема для формирования импульсов с задержкой.

Рисунок 34 – Функциональная схема для формирования импульсов с задержкой

4.3 МОДЕЛИРОВАНИЕ

На рисунках 35, 36, 37, 38 представлено моделирование схемы в режиме Timing, собранной в графическом редакторе.

Рисунок 35 – Моделирование схемы, режим Timing, часть 1

Рисунок 36 – Моделирование схемы, режим Timing, часть 2

Рисунок 37 – Моделирование схемы, режим Timing, часть 3

Рисунок 38 – Моделирование схемы, режим Timing, часть 4

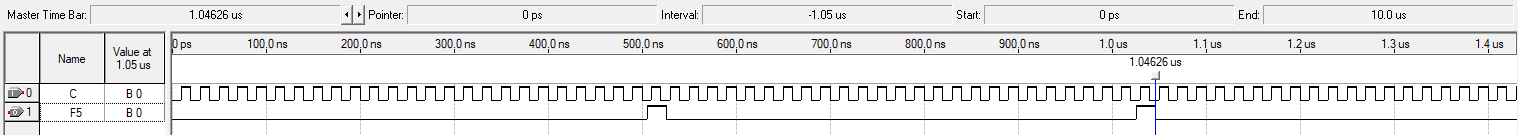

На рисунках 39, 40, 41, 42 представлены результаты моделирования в режиме Functional.

Рисунок 39 – Моделирование схемы, режим Functional, часть 1

Рисунок 40 – Моделирование схемы, режим Functional, часть 2

Рисунок 41 – Моделирование схемы, режим Functional, часть 3

Рисунок 42 – Моделирование схемы, режим Functional, часть 4

Результаты моделирования в Functional и Timing аналогичны и соответствуют ожидаемым – значит схема собрана правильно.