- •Цель работы

- •Постановка задачи

- •1.1 Асинхронный счетчик

- •1.1 Таблица функционирования

- •2.1 Таблица функционирования

- •2.2 Функциональная схема синхронного счетчика

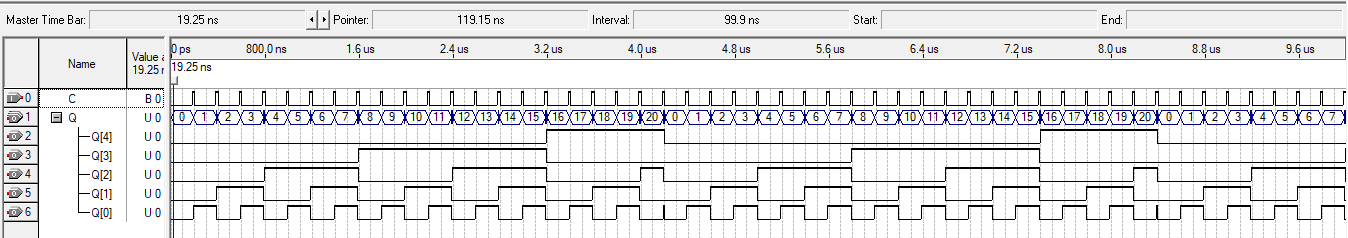

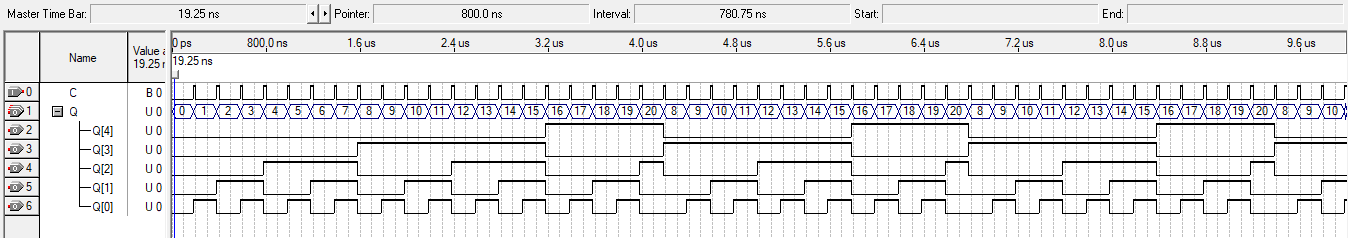

- •2.3 Моделирование синхронного счетчика

- •3.4 Код на vhdl, делитель частоты

- •3.5 Схема из rtl viewer

- •3.6 Моделирование кода

- •4.4 Код на vhdl

- •4.5 Схема из rtl viewer

- •4.6 Моделирование кода на vhdl

- •5. Заключение

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ СЧЁТЧИКОВ

Отчет по лабораторной работе №5

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

23.05.2021

Руководитель

Доцент БИС

___________ Мальчуков А. Н.

23.05.2021

Томск 2021

Цель работы

Изучить двоичные счётчики, их принципы построения и работы.

Постановка задачи

Для 7 варианта необходимо собрать асинхронный, суммирующий счетчик на D триггерах с модулем счета равным 21, синхронный, вычитающий счетчик с убывающим фронтом, асинхронным сбросом и модулем счета равным 26. Помимо этого необходимо собрать делитель частоты с частотой 1785714 Гц и реализовать схему формирования импульсов с задержкой между ними 520 нс. Для вычитающего и суммирующего счетчиков нужно построить таблицы функционирования. Для задач делителя частоты и формирования задержки нужно привести расчеты.

Промоделировать работу всех схем в двух режимах. Провести анализ результатов моделирования разных режимов.

Сверить результаты моделирования с составленными таблицами функционирования и расчётами.

Повторить предыдущие пункты только для описания устройств вместо схем на холстах bdf использовать язык описания аппаратуры VHDL.

Написать выводы о проделанной работе.

1.1 Асинхронный счетчик

1.1 Таблица функционирования

В таблице 1 представлены комбинации нулей и единиц, которые может обработать схема. Таблица 1 – Асинхронный счетчик.

№ сигнала |

Выходы |

||||

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

1 |

1 |

1 |

1 |

16 |

1 |

0 |

0 |

0 |

0 |

17 |

1 |

0 |

0 |

0 |

1 |

18 |

1 |

0 |

0 |

1 |

0 |

19 |

1 |

0 |

0 |

1 |

1 |

20 |

1 |

0 |

1 |

0 |

0 |

21 |

0 |

0 |

0 |

0 |

0 |

22 |

0 |

0 |

0 |

0 |

1 |

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 1 представлен Асинхронный, суммирующий счетчик на D триггерах.

Рисунок 1 – Асинхронный счетчик, функциональная схема

1.3 МОДЕЛИРОВАНИЕ

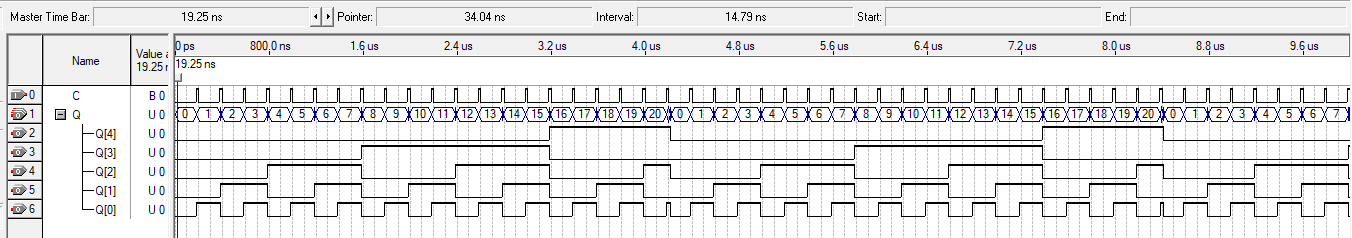

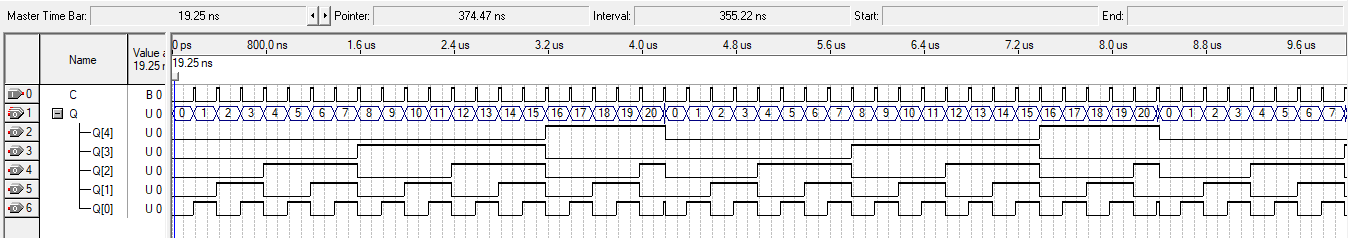

На рисунках 2, 3 представлено моделирование в двух режимах

Рисунок 2 – Моделирование в режиме Timing

Рисунок 3 – Моделирование в режиме Functional

На рисунках перебор всех значений происходит в соответствии с таблицей функционирования (таблица 1). Все значения совпадают с теми, что прописаны в таблице (В режиме Timing).

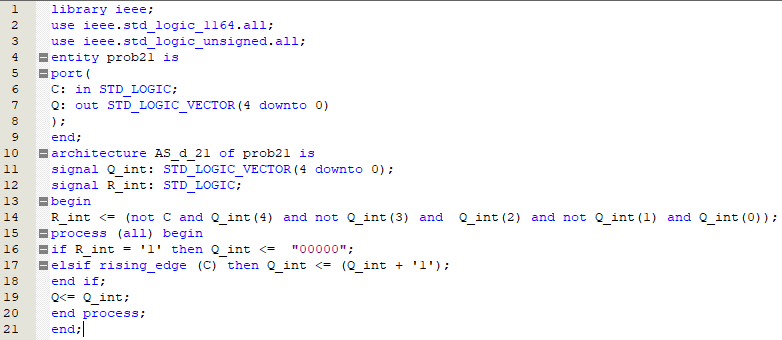

1.4 КОД НА VHDL

На рисунке 4 представлен код на языке VHDL для асинхронного счетчика.

Рисунок 4 – Код для асинхронного счетчика на VHDL

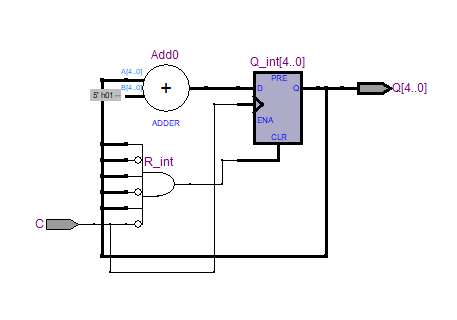

1.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 5 представлена схема, которую собрала программа на основании написанного кода, приведенного в предыдущем пункте.

Рисунок 5 – Схема из RTL viewer

1.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО HDL КОДОМ

На рисунках 6, 7 представлен результат моделирования схемы, описанной на языке VHDL.

Рисунок 6 – Моделирование, VHDL, Functional

Рисунок 7 – Моделирование, VHDL, Timing

Результаты представленные на рисунках 6–7 аналогичны тем, что были получены раннее. Все значения совпадают с таблицей истинности, это означает, что схемы описаны правильно.

2. СИХРОННЫЙ, ВЫЧИТАЮЩИЙ СЧЕТЧИК