- •Цель работы

- •Постановка задачи

- •1.Шифратор 4-2

- •1.1 Таблица истинности

- •2.1 Таблица истинности

- •2.2 Формула

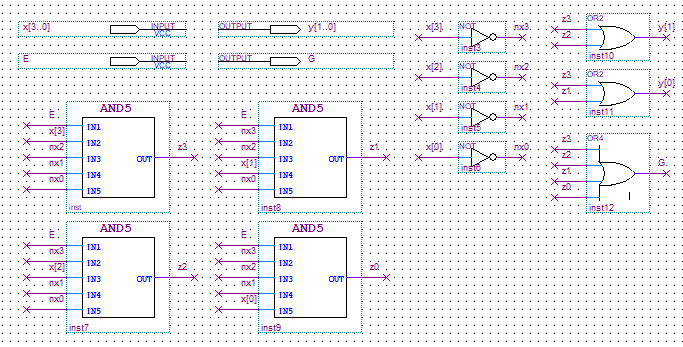

- •2.3 Функциональная схема

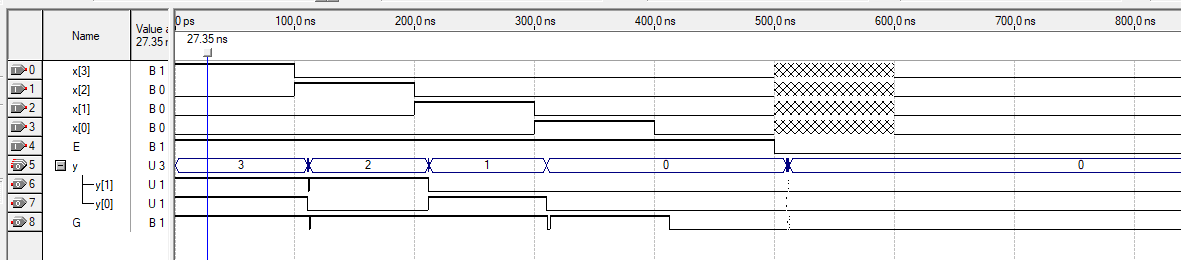

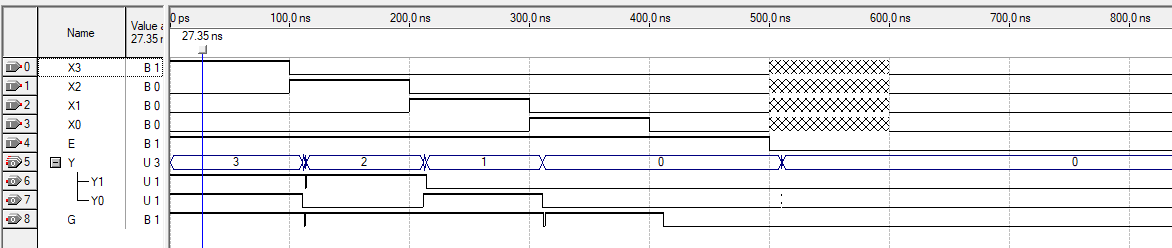

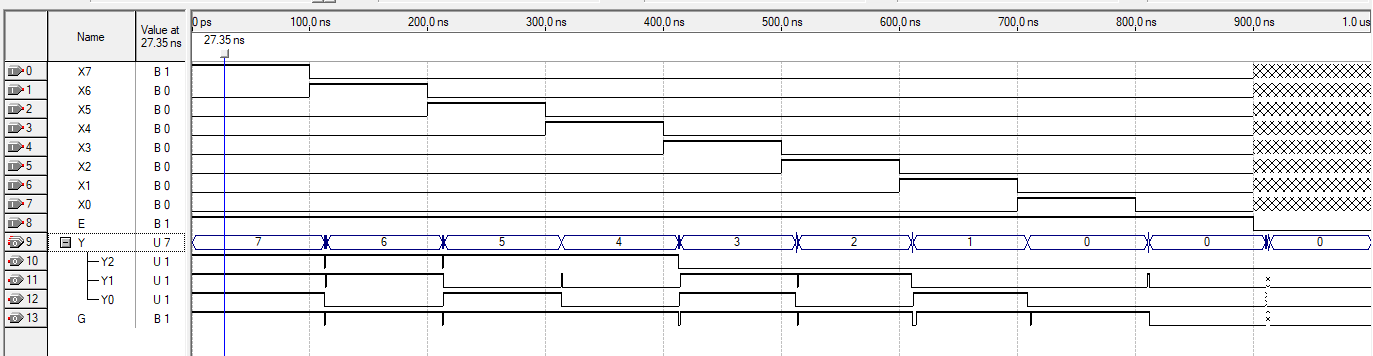

- •2.4 Моделирование функциональной схемы

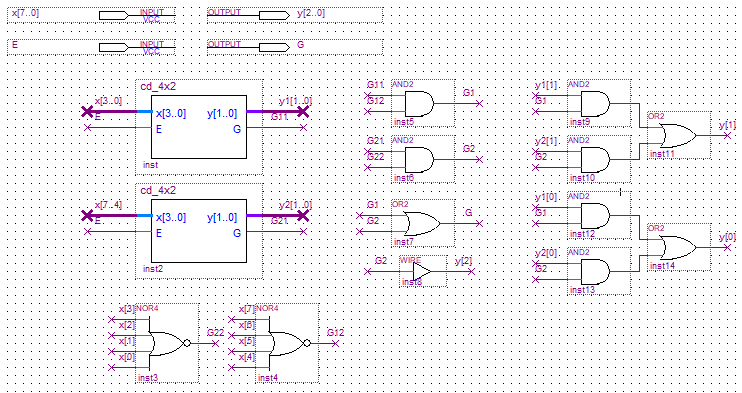

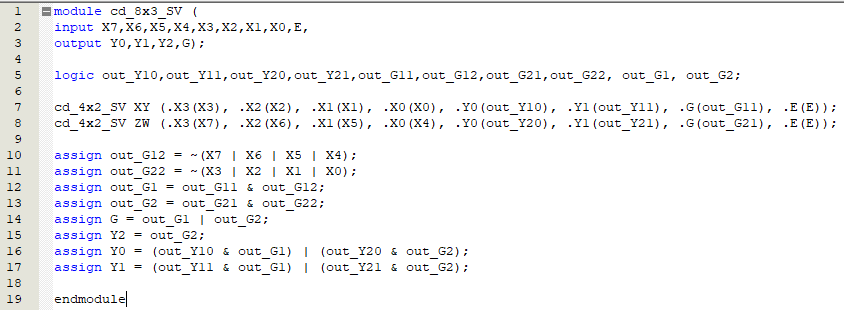

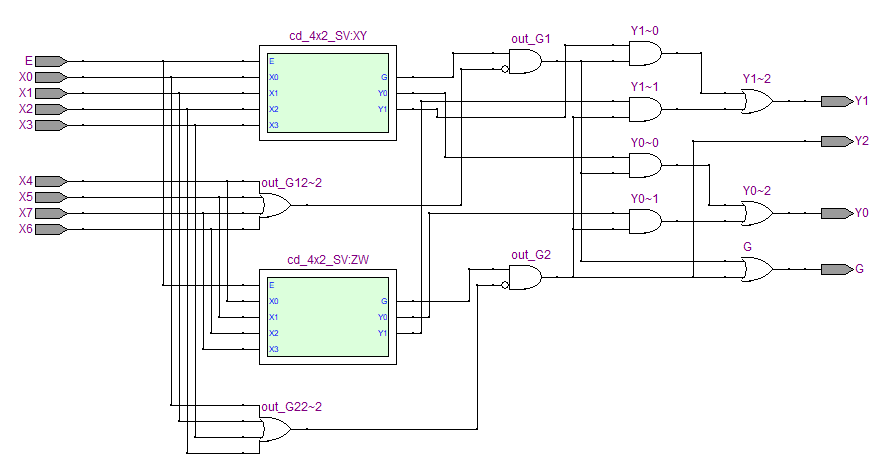

- •2.6 Схема из rtl Viewer для кода hdl

- •2.7 Моделирование устройства, описанного кодом hdl.

- •2.8 Таблица истинности масштабируемого устройства

- •3.1 Таблица истинности

- •3.2 Формула

- •3.3 Функциональная схема

- •3.4 Моделирование функциональной схемы

- •3.6 Схема из rtl Viewer для кода hdl

- •3.7 Моделирование устройства, описанного кодом hdl

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ШИФРАТОРЫ И ДЕШИФРАТОРЫ

Отчет по лабораторной работе №2

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

28.03.2021

Руководитель

Доцент БИС

___________ Мальчуков А.Н.

28.03.2021

Томск 2021

Цель работы

Цель работы: научиться создавать шифраторы и дешифраторы на разных базисах и решать задачу увеличения их размерности.

Постановка задачи

В ходе данной лабораторной работы требуется выполнить следующие задачи:

Шифратор: 4 входа, базис «И, ИЛИ, НЕ», нарастить до 8 входов.

Дешифратор: 8 выходов, базис «ИЛИ-НЕ», нарастить до 16 входов.

Приоритетный шифратор: 6 входов, базис «И-НЕ».

Задания:

1. Составить таблицы истинности для схем. Написать формулы для всех выходов в СДНФ или СКНФ. Привести формулы к требуемому базису согласно варианту.

2. Собрать схемы на холстах .bdf согласно полученным формулам. Если в варианте предполагается наращивание, создать символ для полученного блока.

3. Создайте схему устройства согласно варианту большей размерности на основе созданного ранее символа.

4. Промоделировать работу всех схем в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5. Сверить результаты моделирования с составленными таблицами истинностями.

6. Повторить пункты 2-5, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL. При масштабировании использовать модульное подключение.

7. Написать выводы о проделанной работе.

1.Шифратор 4-2

1.1 Таблица истинности

Таблица истинности для шифратора 10-4 приведена в таблице 1.1.

Таблица 1.1 – Шифратор 10-4

CD 4x2 |

||||||||

Входы |

Выходы |

|||||||

E |

x3 |

x2 |

x1 |

x0 |

y1 |

y0 |

G |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

x |

x |

x |

x |

0 |

0 |

0 |

|

1.2 Формула

На рисунке 1.2 представлены формулы, по которым будет строиться шифратор 4-2.

Рисунок 1.2 – Формулы шифратора 4-2

1.3 Функциональная схема

Функциональная схема шифратора 4-2 приведена на рисунке 1.3

Рисунок 1.3 – Функциональная схема шифратора 4-2

1.4 Моделирование

На рисунке 1.4 представлен результат временного моделирования шифратора 4-2.

Рисунок 1.4 – Временная диаграмма для шифратора 4-2

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено верно.

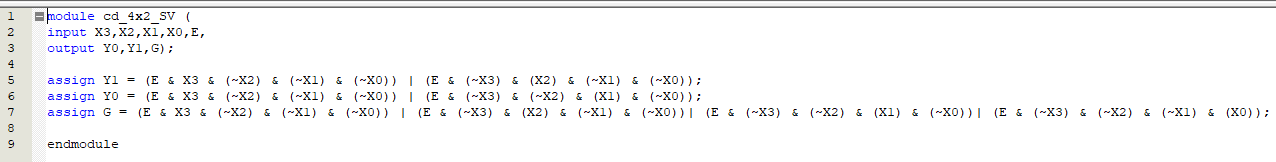

1.5 Код на HDL

На рисунке 1.5 показан код на SystemVerilog для шифратора 4-2.

Рисунок 1.5 – Код описания шифратора 4-2 на SystemVerilog

1.6 Схема из RTL Viewer для кода HDL

На рисунке 1.6 показана схема из RTL Viewer для кода на SystemVerilog.

Рисунок 1.6 – Схема из RTL Viewer

1.7 Моделирование устройства, описанного кодом HDL

На рисунке 1.7 представлен результат временного моделирования шифратора 4-2, описанного на SystemVerilog.

Рисунок 1.7 – Результат временного моделирования шифратора 4-2, описанного на SystemVerilog

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно.

1.8 Таблица истинности масштабируемого устройства

Таблица истинности масштабируемого устройства представлена в таблице 1.8.

Таблица 1.8 – Масштабируемое устройство

CD 8x3 |

||||||||||||

Входы |

Выходы |

|||||||||||

E |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

y2 |

y1 |

y0 |

G |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

1.9 Функциональная схема масштабируемого устройства.

Функциональная схема масштабируемого устройства приведена на рисунке 1.9.

Рисунок 1.9 – Функциональная схема масштабируемого устройства

1.10 Моделирование масштабируемого устройства

Для реализации моделирования масштабируемого устройства была составлена временная диаграмма, которая показана на рисунке 1.10.

Рисунок 1.10 – Временная диаграмма для масштабируемого устройства

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно.

1.11 Код на HDL масштабируемого устройства

На рисунке 1.11 показан код на SystemVerilog для масштабируемого устройства.

Рисунок 1.11 – Код на SystemVerilog для масштабируемого устройства

1.12 Схема из RTL Viewer для кода HDL масштабируемого устройства

На рисунке 1.12 показана схема из RTL Viewer для кода на SystemVerilog.

Рисунок 1.12 – Схема из RTL Viewer

1.13 Моделирование масштабируемого устройства, описанного кодом HDL

На рисунке 1.13 представлен результат временного моделирования шифратора 8-3, описанного на SystemVerilog.

Рисунок 1.13 – Результат временного моделирования шифратора 8-3, описанного на SystemVerilog

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно. Данные результаты совпадают с результатами моделирования схемы.

2 Дешифратор 2-4