Декодеры и кодеры

.docxДекодеры и кодеры

Структуры DC – по способу построения

1.Параллельный 2.Пирамидальные 3.Многоступенчатые DC

При выполнении операций в ЭВМ обычно используют несколько разновидностей двоичного кода (прямой, обратный, дополнительный, двоично-десятичный). При передаче информации по линиям связи удобнее использовать другие виды кодов, которые могут понижать вероятность появления ошибки или даже исправлять ее в дальнейшем: Пример: 2 из 5 , коды Хемминга, коды с проверкой четности или нечетности. Всегда стоит задача преобразования информации из одного кода в другой. Эту задачу на аппаратном уровне решают устройства – преобразователи кодов. Шифратор (кодер) – комбинационное логическое устройство, которое преобразует числа из позиционного кода в двоичный. Используется в устройстве ввода информации.

Устройство

ввода

УГО в общем виде:

информации с

клавиатуры

Входом

СD присваиваются значения десятичных

чисел, подача на один из входов активного

логического уровня воспринимается как

подача соответствующего десятичного

числа.

Этот сигнал преобразуется на

выходе CD в двоичный код.

Если n-число

выходов, то CD имеющий 2n n выходов,

называется полным.

Если число входов

CD<2n, то СD называется не полным.

Рассмотрим

работу СD на примере преобразователя

десятичных чисел от 0?9 в двоично-десятичный

код по соответствующей таблицы истинности.

Входом

СD присваиваются значения десятичных

чисел, подача на один из входов активного

логического уровня воспринимается как

подача соответствующего десятичного

числа.

Этот сигнал преобразуется на

выходе CD в двоичный код.

Если n-число

выходов, то CD имеющий 2n n выходов,

называется полным.

Если число входов

CD<2n, то СD называется не полным.

Рассмотрим

работу СD на примере преобразователя

десятичных чисел от 0?9 в двоично-десятичный

код по соответствующей таблицы истинности.

Таблица истинности

|

X9 |

X8 |

X7 |

X6 |

X5 |

X4 |

X3 |

X2 |

X1 |

X0 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

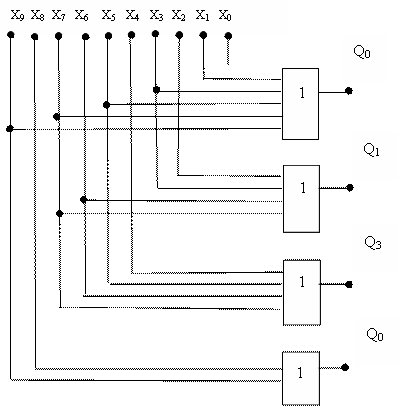

Q3=X8+X9 Q2=X4+X5+X6+X7 Q1=X2 +X3 +X6 +X7 Q0=X1 +X3 +X5 +X7+X9 Данная система ФАЛ характеризует работу СD.

Логическая

схема устройства СD.

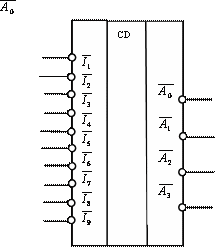

Реальные

МС шифраторов К155 ИВ1 и К155ИВ3.

Входной

и выходной активный логический уровень

равен нулю. Для этой МС характерен

принцип приоритетной выборки. Принцип

приоритетной выборки – если на входе

появляется несколько сигналов активного

логического уровня (в данной ИМС=0), то

приоритетом обладает сигнал находящийся

на входе со старшим номером.

Рассмотрим

на таблице истинности К155 ИВ3:

Входной

и выходной активный логический уровень

равен нулю. Для этой МС характерен

принцип приоритетной выборки. Принцип

приоритетной выборки – если на входе

появляется несколько сигналов активного

логического уровня (в данной ИМС=0), то

приоритетом обладает сигнал находящийся

на входе со старшим номером.

Рассмотрим

на таблице истинности К155 ИВ3:

|

I9 |

I8 |

I7 |

I6 |

I5 |

I4 |

I3 |

I2 |

I1 |

I0 |

A3 |

A2 |

A1 |

A0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

* |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

* |

* |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

* |

* |

* |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

* |

* |

* |

* |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

* |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

1 |

0 |

0 |

0 |

|

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

0 |

1 |

1 |

1 |

|

0 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

0 |

1 |

1 |

0 |

Пример: Для комбинации на выходе 1001 На входах может быть 111000000 111011111 111010110 Как появился на старшем разряде 0, то выходе однозначно появится комбинация 1001.

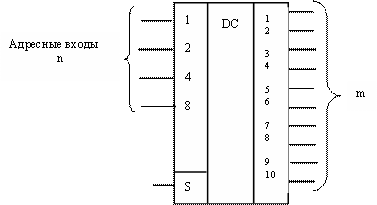

Декодер (дешифратор) – комбинационное логическое устройство для преобразования чисел из двоичного кода в позиционный. Таким образом DC выполняет операцию обратную СD. Сигнал активного уровня может быть только на одном из выходов, адрес который определяется комбинацией входных сигналов. Пример: К155 ИD 1 Число n – порядок декодера. Если 2n =m - полный DC, если m<2n не полный DC. Полный DC – функционально полный элемент. Функционирование полного DC можно описать системой булевых функций:

yi = s (a2a1a0), где i- номер входа (a2a1a0)-полное множество конституент лог.1, где

|

a |

b |

3 |

2 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

Выходы

могут быть прямыми и инверсными. В DC

часто применяют разрешающие – стробирующие

входы. С их помощью DC может быть

преобразован в демультиплексор или

увеличить порядок DC. Могут быть парафазные

входы для подачи наряду с входными

переменными их инверсий. Т.О. С помощью

DC можно реализовать любую функцию.

Конституента

единицы – такая логическая функция n

аргументов, которая принимает значение

равное 1 только на одном наборе

аргументов.

Выходы

могут быть прямыми и инверсными. В DC

часто применяют разрешающие – стробирующие

входы. С их помощью DC может быть

преобразован в демультиплексор или

увеличить порядок DC. Могут быть парафазные

входы для подачи наряду с входными

переменными их инверсий. Т.О. С помощью

DC можно реализовать любую функцию.

Конституента

единицы – такая логическая функция n

аргументов, которая принимает значение

равное 1 только на одном наборе

аргументов.

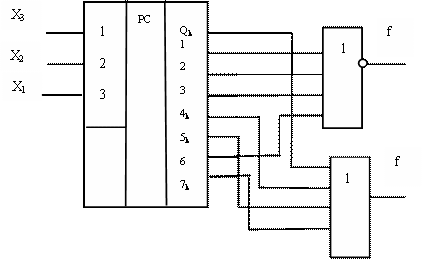

![]() -

обобщенная формула для реализации

некоторой логической функции

h-подмножество конституент, в которой

функция равна 1. (объед.по «ИЛИ2» , «1»)

-

обобщенная формула для реализации

некоторой логической функции

h-подмножество конституент, в которой

функция равна 1. (объед.по «ИЛИ2» , «1»)

![]() -

для DC c прямыми выходами

l-подмножество

конститует в котором функция равна 0

(объед.по «ИЛИ» с инверсией)

Пример:

-

для DC c прямыми выходами

l-подмножество

конститует в котором функция равна 0

(объед.по «ИЛИ» с инверсией)

Пример:

![]()

![]() -

для DC с инверсными выходами назначения

h и l то же.

-

для DC с инверсными выходами назначения

h и l то же.

Структуры DC – по способу построения

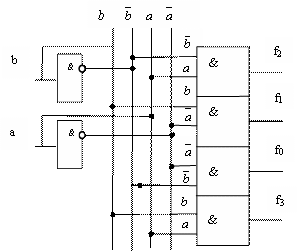

1.Параллельный, одноступенчатый, линейный – самый быстродействующий. Основное отличие всех структур сводится к разнице по: - быстродействию, - числе используемых элементарных логических элементов, - самый быстродействующий - N =n+2n ,где n- разряд DC

|

a |

b |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

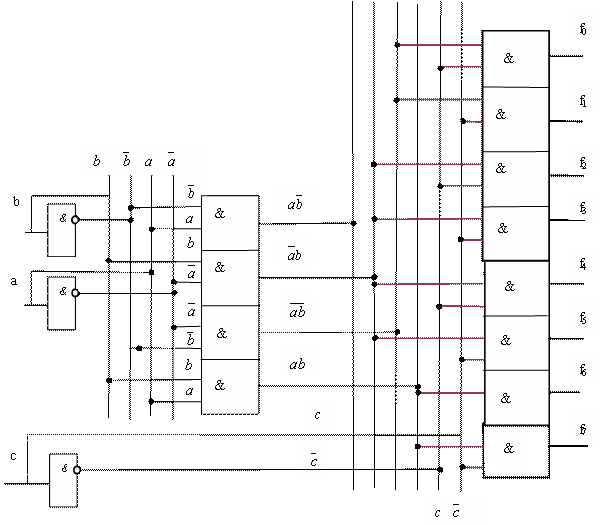

2.Пирамидальные

Для получения DC N+1 разрядного кода надо дважды повторить все комбинации N разрядного кода для значений 0 и 1 старшего разряда (N+1). N = 2*2n + (n – 1)*2n - 1

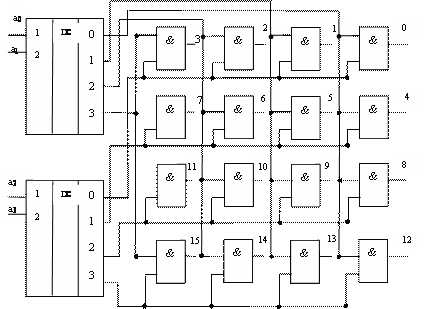

3.Многоступенчатые DC

По

идеологии построения сходны с предыдущими,

но повторение комбинации n-разрядного

кода производится не для одного разряда,

а для другого n-разрядного кода.

N = 2*2n + 2(n/2)*2n/2

Вернутся к содержанию...

Используются технологии uCoz