Элементы систем автоматики

..pdfкольцевая проточка золотника соединяет входное отверстие золотниковой коробки с ее выходным отверстием, при этом на выходе пневматического реле скачкообразно появляется выходной сигнал Ðî.

При снятии сигнала управления Ðó пружина 3 перемещает мембрану 2 и клапан 4 в исходное положение. Этот клапан перекрывает поступление сжатого воздуха в торцевую полость золотниковой коробки 5, в результате чего под действием пружины 7 золотник 6 возвращается в исходное состояние, закрывая канал соединения входного и выходного отверстий золотниковой коробки. При этом на выходе пневматического реле выходной сигнал Ðî скачкообразно снижается до нуля.

3. ТЕХНИЧЕСКИЕ СРЕДСТВА

АВТОМАТИЗАЦИИ ДЛЯ ЦИФРОВЫХ СИСТЕМ

В настоящее время аналоговые системы управления повсеместно заменяются цифровыми, в основе работы которых заложены принципы получения, передачи и обработки цифровых сигналов. Понятия о структуре цифровых сигналов были изложены в начале нашего курса. В принцип работы цифровых систем заложены и принципы алгебры логики.

Использование сигналов в цифровой форме позволяет значи- тельно повысить помехозащищенность систем управления, а это свойство в настоящее время является решающим при выборе типа системы управления.

3.1. Логические элементы цифровой автоматики

Основой систем цифровой автоматики кроме цифровых сигналов являются еще и логические элементы, принцип работы которых основан на законах науки, называемой АЛГЕБРОЙ ЛОГИКИ. Все входные параметры (входные сигналы логических элементов)

41

по законам этой науки принимают за аргументы, а выходные параметры (выходные сигналы логических элементов), в свою очередь, принимают за функции. Как аргументы, так и функции этих логиче- ских законов (элементов) всегда дискретны и могут принимать только одно из двух значений: ИСТИННО или ЛОЖНО. Применительно к логическим элементам автоматики истинно всегда соответствует значению логической единицы, а ложно — это всегда логический ноль. Основные логические элементы и соответствующие им логические функции алгебры логики представлены в табл. 1.

Ò à á ë è ö à 1

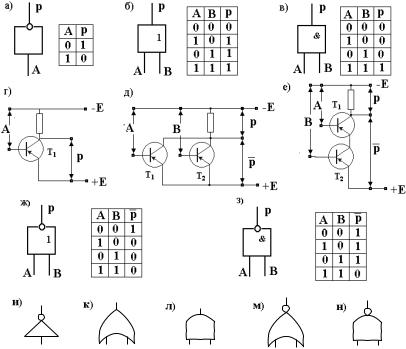

Логический элемент НЕ (изображается согласно схеме, представленной на рис. 29, а) работает на принципе реализации закона логического отрицания (или инверсии), по которому выходной параметр (сигнал) логического элемента всегда противоположен входному. Принципиально этот элемент реализуется в релейным варианте, показанном в соответствующем столбце строки ¹ 1 табл. 1. Этот элемент можно реализовать и в транзисторном варианте, представленном на рис. 29, г. При отсутствии сигнала А на базе

42

Рис. 29. Схемы основных логических элементов, представленных в различных вариантах их реализации

транзистора он закрыт, поэтому выходной потенциал Р равен напряжению источника питания Е, т. е. в этом случае он равен единице. При подаче сигнала А, равном потенциалу открытия транзистора (т. е. равном 1), выходной потенциал Р снижается до нуля, поэтому на выходе элемента в этом случае появляется нулевой сигнал.

Логический элемент ИЛИ работает на принципе реализации закона логического сложения, по которому выходной сигнал всегда единичен, если единичен хотя бы один входной сигнал. На логиче- ских схемах этот элемент изображается фигурой, представленной на рис. 29, б. Рядом с этой схемой показана таблица логического состояния (логических выходов при определенных значениях входных сигналов) этого элемента.

Принципиально этот элемент реализуется в релейном варианте, показанном в соответствующем столбце строки ¹ 2 табл. 1. Этот

43

элемент также можно реализовать для двух входных сигналов по транзисторной схеме показанной на рис. 29, д.

Выходной сигнал Р для этого элемента снимается между коллекторным выходом транзисторов и отрицательным потенциалом источника питания. Если же этот сигнал снимать между эмиттером и коллектором транзисторов, то реализуется составная логическая функция ИЛИ-НЕ, которая работает на принципе реализации двух логических законов: логического сложения и логического отрицания, при этом вначале выходной сигнал формируется по закону логического сложения, а затем инвертируется. На логических схемах этот элемент изображается фигурой, представленной на рис. 29, ж. Рядом со схемой также показана таблица логического состояния, которая противоположна аналогичной схеме для элемента ИЛИ. Релейный вариант реализации этой схемы показан в столбце строки ¹ 4 табл. 1.

Логический элемент И работает на принципе реализации закона логического умножения, по которому выходной сигнал этого элемента единичен только тогда, когда единичен хотя бы один из входных сигналов элемента. На логических схемах этот элемент изображается фигурой, представленной на рис. 29, в. Рядом со схемой также показана таблица логического состояния (логических выходов) этого элемента при всех возможных вариантах состояния входных сигналов.

Принципиально этот элемент реализуется в релейном варианте, показанном в соответствующем столбце строки ¹ 3 табл. 1. В транзисторном варианте этот элемент для двух входных сигналов можно реализовать по схеме, показанной на рис. 29, е.

Логический элемент И-НЕ работает аналогично на принципе двух логических функций: логического умножения и логического отрицания, которые функционируют в той же последовательности, что и предыдущая совместная функция. На логических схемах этот элемент изображается фигурой, представленной на рис. 29, з. Варианты логических состояний для этой функции противоположны аналогичным состояниям функции элемента И. Релейный вариант реализации этой функции показан в столбце строки ¹ 5 табл. 1. Транзисторный вариант элемента И-НЕ имеет то же исполнение, что и элемента И, только его выходной сигнал снимается между эмиттером первого транзистора и коллектором второго.

44

В табл. 1 даны эквивалентные релейные схемы для каждого из вышеперечисленных элементов, а также даны ссылки на эквивалентные схемы их изображения по российскому и евростандарту, представленные на рис. 29.

3.2. Запоминающие элементы цифровой автоматики

Для запоминания (записи) однобитовых двоичных символов «0» или «1» применяют логические устройства, которые называются триггерами. Триггеры могут быть статическими и динамическими.

3.2.1. Статический RS-триггер

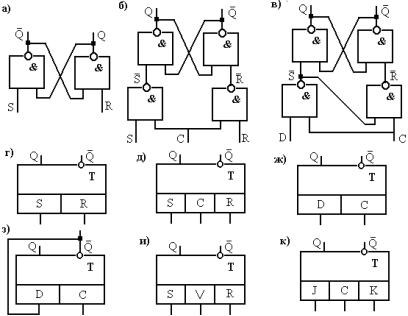

Статический RS-триггер может быть выполнен на основе соединения двух логических элементов И-НЕ по схеме, показанной на рис. 30, а. Триггер типа RS может быть представлен в двух вариантах: синхронном и асинхронном.

Рис. 30. Логические схемы асинхронно-статического RS-триггера,

синхронного R-триггера и D-триггера

45

Для асинхронного варианта это логическое устройство имеет два входа: один из них вход S информационный, а другой вход R обнуления триггера. У всех триггеров два выхода: один из них Q прямой, другой Q инверсный. В табл. 2 приведены параметры логиче- ского состояния асинхронного RS-триггера.

Согласно этой таблице триггер работает как переключатель при подаче на соответствующий

S |

R |

Q |

Q |

вход нуля или единицы. |

1 |

0 |

1 |

0 |

Одновременная подача на |

0 |

1 |

0 |

1 |

входы двух нулей или двух еди- |

0 |

0 |

1 |

1 |

ниц приводит к неопределенно- |

|

|

|

|

му (неоднозначному) состоя- |

1 |

1 |

|

Запрет |

|

|

|

нию этого триггера, поэтому такой режим работы нежелателен.

Схема синхронного статического RS-триггера показана на рис. 30, б, а в табл. 3 приведены параметры его логического состояния.

Ò à á ë è ö à 3

Ñ |

S |

R |

Q |

|

Q |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

|

запрет |

|

Согласно параметрам этой таблицы синхронный RS-триг- гер работает как переключатель

(аналогично предыдущей схеме) только тогда, когда подается единичный сигнал на его С вход. При нулевом состоянии входа С триггер этого типа выключен из работы, т. е. всегда находится в нулевом состоянии.

При подаче на этот вход

единичного символа он начинает работать в режиме асинхронного RS-триггера.

3.2.2. Динамический D-триггер

Структура динамического D-триггера показана на рис. 30, в. Триггер этого типа имеет вход С для подачи тактового сигнала и информационный вход D. У триггера этого типа также два выхода: один из них Q прямой, другой Q инверсный. Параметры логического состояния этого триггера приведены в табл. 4.

46

Анализ параметров этой таблицы показывает, что до тех

пор, пока за тактовый цикл импульс на входе С не переходит с уровня 0 на уровень 1, информационный вход D не изменяет предыдущего состояния этого триггера. Это свойство триггера данного типа успешно используется во многих цифровых логических устройствах.

Ò à á ë è ö à 4

Ñ |

D |

Q |

Q |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Обычно на принципиальных схемах цифровых устройств триггеры различных типов изо-

бражают с помощью фигур, представленных на рис. 30, г–к.

Если инверсный выход Q D-триггера соединить с его входом D, то получим триггер с особыми свойствами (рис. 30, з). Такой триггер называют переключающим Т-триггером, который за каждый цикл тактового сигнала на входе С меняет свое состояние на противоположное. На принципиальных схемах цифровых систем этот триггер представлен в виде схемы, показанной на рис. 30, и. На рис. 30, к показана схема универсального JK-триггера, свойства которого зависят от соотношения сигналов на входах J и K. Некоторыми из этих свойств мы воспользуемся в дальнейшем при изуче- нии сложных логических устройств.

3.3. Регистры памяти

Триггеры различного типа используются только для записи однобитовой цифровой информации. Для записи многоразрядных цифровых сигналов используются устройства, которые называются запоминающими регистрами. Запоминающие регистры бывают двух типов: параллельными и последовательными. Оба типа регистров создаются на основе различного типа триггеров и отличаются способом записи цифровых сигналов. Регистры, как и триггеры, относятся к энергозависимым элементам памяти.

3.3.1. Параллельный регистр

Параллельные регистры применяются для записи и считывания цифровых сигналов в параллельном коде, а это значит, что одновре-

47

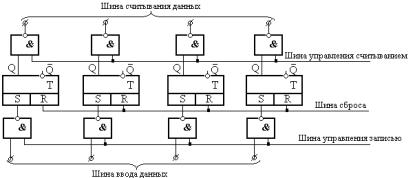

Рис. 31. Схема параллельного регистра

менно все разряды цифрового сигнала могут быть записаны в регистр или быть считаны из него. Схема параллельного регистра показана на рис. 31. Основу этого регистра составляют триггеры типа RS, входы R которых одновременно подключены к шине сброса. Это позволяет при подаче единичного импульса сброса на эту шину одновременно обнулять все триггеры регистра. Количество триггеров в регистре численно равно разрядности цифрового сигнала. Входы S всех триггеров регистра соответственно соединены с выходами логи- ческих ключей И, предназначенных для управления процессом записи цифровых сигналов в этот регистр. Один из входов этих ключей соединен с шиной управления записью, а к другим входам этих клю- чей поразрядно подаются символы цифрового сигнала, записываемого из шины ввода данных. Аналогично устроена система считывания цифровых сигналов из этого регистра. Для этой цели также используют логические ключи И, соединенные одним из своих входов с шиной управления считыванием. К другим входам этих ключей подсоединены выходы всех триггеров регистра. Выходы всех логических ключей считывания подсоединены к шине данных считывания.

Принцип работы параллельного регистра. Перед записью оче- редного цифрового сигнала в регистр на шину сброса подается единичный импульс, который переводит все RS-триггеры в нулевое состояние. После этого на шину ввода данных поразрядно подается цифровой сигнал, который после подачи единичного импульса разрешения записи изменит состояние тех триггеров, на входы S которых через ключи И подается единичный символ. Записанная инфор-

48

мация в регистре остается неизменной до тех пор, пока не будет дана команда на запись нового цифрового сигнала. Перед записью новой информации необходимо обнулить регистр. Информация в регистре пропадает также при выключении электропитания триггеров регистра, поэтому этот вид записи цифровых сигналов относится к энергозависимым. При считывании информации из этого регистра подается единичный импульс на шину управления считыванием. После чего логические ключи И поразрядно выставляют на шине считывания данных символы состояния разрядных триггеров регистра. Состояние этих триггеров при считывании информации из регистра не меняется, поэтому считывание информации может производится многократно.

Если систему считывания информации из регистра аналогично подсоединить к выходам Q разрядных триггеров регистра, то записанная информация регистра будет считываться в обратном (инверсном) коде, что необходимо выполнять при некоторых алгебраи- ческих операциях над двоичными числами.

3.3.2. Последовательный регистр

Последовательные регистры применяются для записи цифровых сигналов в последовательном коде, а это значит, что символы цифрового сигнала одним проводом последовательно подаются на информационный вход триггера младшего разряда, а затем за каждый такт также последовательно сдвигаются в сторону триггеров старших разрядов. Схема последовательного регистра показана на рис. 32

Основой последовательного регистра является D-триггер, коли- чество которых в регистре численно равно разрядности записываемого цифрового сигнала. Каждый выход Q предыдущего триггера соединен с входом D последующего, а вход D триггера младшего разряда связан с шиной последовательного ввода данных. Входы С всех триггеров связаны с шиной подачи тактовых импульсов, которые подаются одновременно сразу на все триггеры регистра. Этот регистр имеет аналогичную с параллельным регистром систему записи и считывания сигнала, которая устроена и работает точно так же.

Принцип работы последовательного регистра. На входы С всех триггеров регистра одновременно подаются тактовые импульсы. За время первого такта на вход D триггера младшего разряда из

49

Рис. 32. Схема последовательного регистра

шины ввода подается первый символ записываемого цифрового сигнала. Если этот символ единица, то в момент перехода тактового сигнала с нуля на единицу триггер младшего разряда установится

âединичное состояние. При этом все остальные триггеры останутся

âнулевом состоянии. Если следующим символом записываемого цифрового сигнала будет нуль, то в момент перехода второго тактового импульса с нуля на единицу триггер младшего разряда перейдет в нулевое состояние, а последующий триггер станет единич- ным, т. к. на его входе D появится единица с выхода Q предыдущего триггера. Таким образом, единичный символ младшего разряда при втором тактовом импульсе переходит во второй разряд (т. е. сдвигается на один разряд вправо), а на его место становится следующий символ из шины ввода. При следующем тактовом импульсе эти символы аналогично и одновременно сдвинутся вправо еще на один разряд (и так далее).

Итак, чтобы записать цифровой сигнал в последовательный регистр нужно на его входы С подавать столько тактовых импульсов, сколько символов содержится в записываемом цифровом сигнале. Все символы этого сигнала нужно последовательно выставлять че- рез шину ввода на входе D-триггера младшего разряда.

Считывание цифровой информации из последовательного регистра может осуществляться двояко: в последовательном и параллельном коде. Для считывания цифровых сигналов в последова-

50