- •Типовой расчет по дисциплине «тдэс»

- •Содержание

- •Аннотация

- •Введение

- •Индивидуальное задание:

- •Проектирование синхронного автомата

- •Подбор микросхем

- •Временные диаграммы работы автомата:

- •Базис «и-не»:

- •Подбор микросхем

- •Временные диаграммы работы автомата:

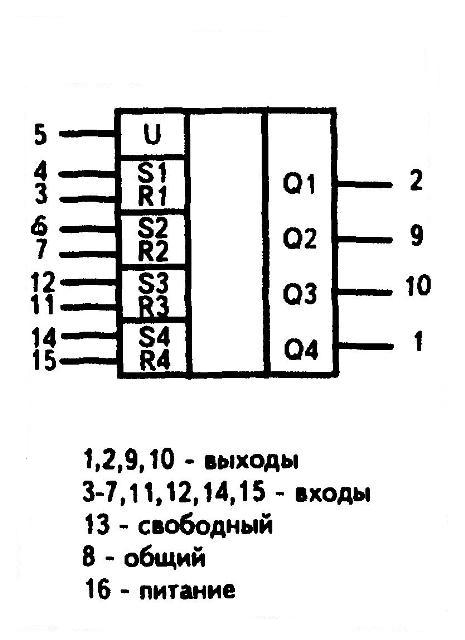

- •Rs-триггер

- •Подбор микросхем

- •Временные диаграммы работы автомата:

- •Базис «и-не»:

- •Подбор микросхем

- •Временные диаграммы работы автомата:

- •Заключение

- •Список литературы:

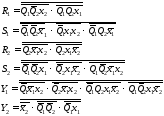

Базис «и-не»:

;

(4)

;

(4)

Совпадений элементов не имеется.

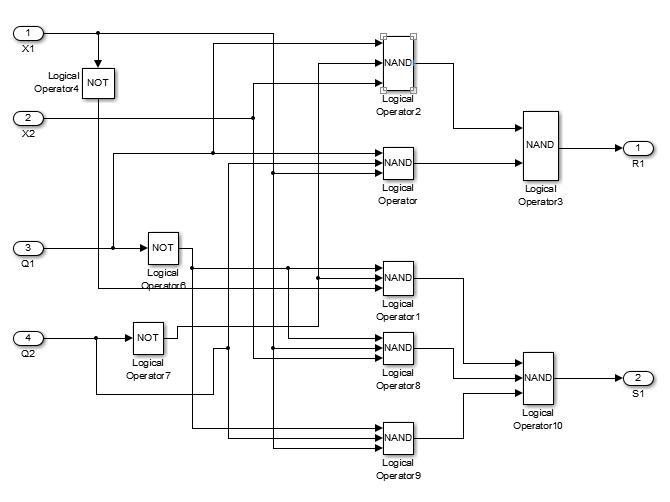

Структурная схема:

Рис.10

Подбор микросхем

Для реализации данного автомата понадобится 2 RS- триггера, 4 элемента 4И-НЕ, 14 элементов 3И-НЕ, 7 элементов 2И-НЕ.

Воспользуемся микросхемами, представляющими собой сборки из нескольких однотипных элементов:

К561ТР2 – четыре RS-триггера;

Напряжение питания. 3...15 В

К561ЛА8 – 2 элемента 4И-НЕ;

Напряжение питания: 3..15V

К561ЛА9 – 5 элементов 3И-НЕ;

Напряжение питания: 3..15V

К561ЛА7 - 2 элемента 2И-НЕ.

Напряжение питания: 3..15V

Таким образом, нам понадобятся:

- 1 микросхема К561ТР2;

- 2 микросхемы К561ЛА8;

- 5 микросхем К561ЛА9;

- 2 микросхемы К561ЛА7.

Незадействованные входы заземлим.

|

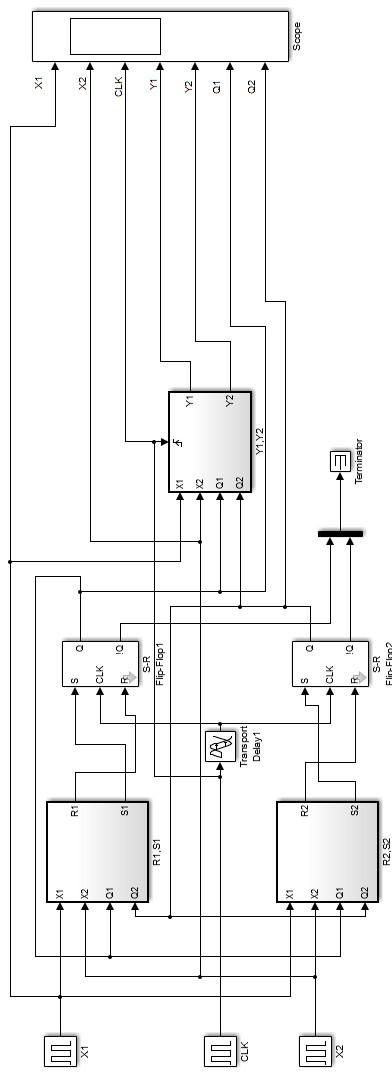

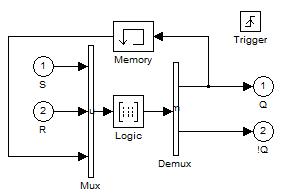

Моделирование в Simulink

|

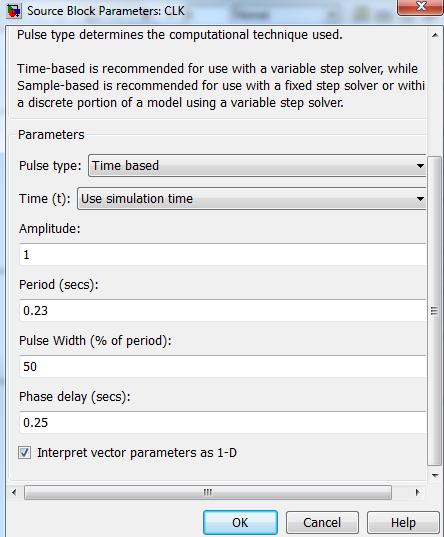

|

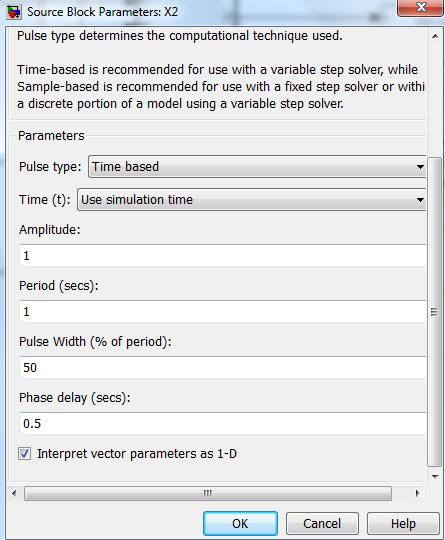

Для реализации автомата составим систему с использование подсистем для формировании сигналов R1, S1, R2, S2, Y1, Y2. Блоки подсистем возьмем из библиотеки: Simulink Ports&Subsystems Subsystem(Triggered Subsystem). RS-триггеры возьмем из библиотеки: Simulink Extras Flip Flops S-R Flip-Flop. Для RS-триггеров и подсистемы Y1, Y2 установим срабатывание по положительному фронту. Неиспользуемые выходы подключим к Terminator (Simulink Sinks Terminator). Для снятия сигналов используем осциллографы: Simulink Sinks Scope. Настроив их параметры для удобного анализа процессов. Для подачи сигналов X1, X2, CLK используем Pulse Generator: Simulink Sources Pulse Generator. Задав параметры для каждого сигнала отдельно:

На входа RS- триггеров установим элемент задержки, для правильного их переключения. Выберем элемент задержки Simulink ContiniousTransport Delay. Обеспечивает задержку входного сигнала на заданное время.

Зададим настройки:

Time Delay — время задержки сигнала (не отрицательное значение);

Initial input — начальное значение выходного сигнала;

Buffer size — размер памяти, выделяемой для хранения задержанного сигнала. Задается в байтах числом, кратным 8 (по умолчанию 1024);

Элемент запаздывания мы ставим для того чтобы учитывать предыдущие значения Q1 и Q2 .

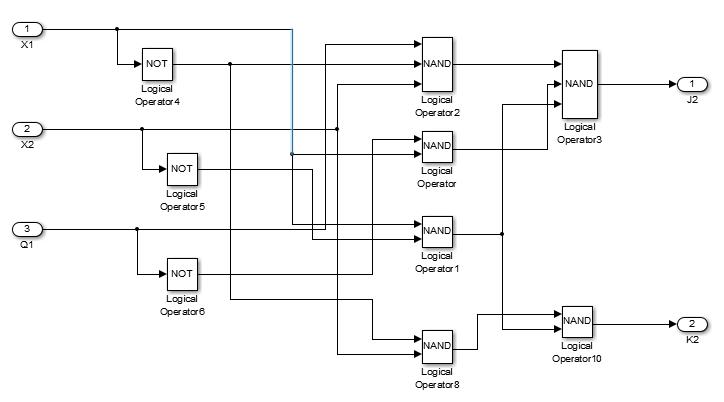

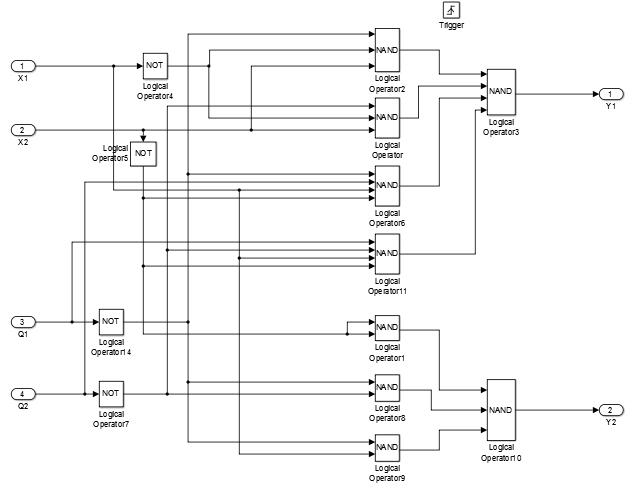

Рассмотрим подробнее используемые подсистемы:

Подсистемы реализуют минимизированные логические функции для сигналов R1, S1, R2, S2, Y1, Y2. Для этого применяются логические элементы ИЛИ-НЕ: Fixed-Point Blockset Logic&Comparison Examples NAND. Для всех логических элементов определим тип выходных данных Boolean.

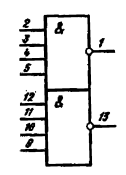

Подсистема R1, S1:

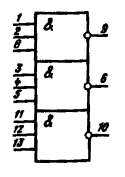

Подсистема R2, S2:

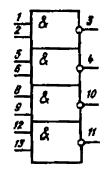

Подсистема Y1, Y2:

Вследствие того, что выходной сигнал должен зависеть от синхросигнала, то в подсистему Y1, Y2 введен триггер (по фронту). Для этого откроем правой кнопкой мыши вкладку и выберем меню Look Under Mask:

Переключение автомата происходит по фронту.

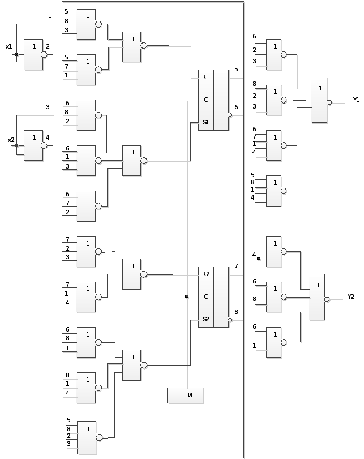

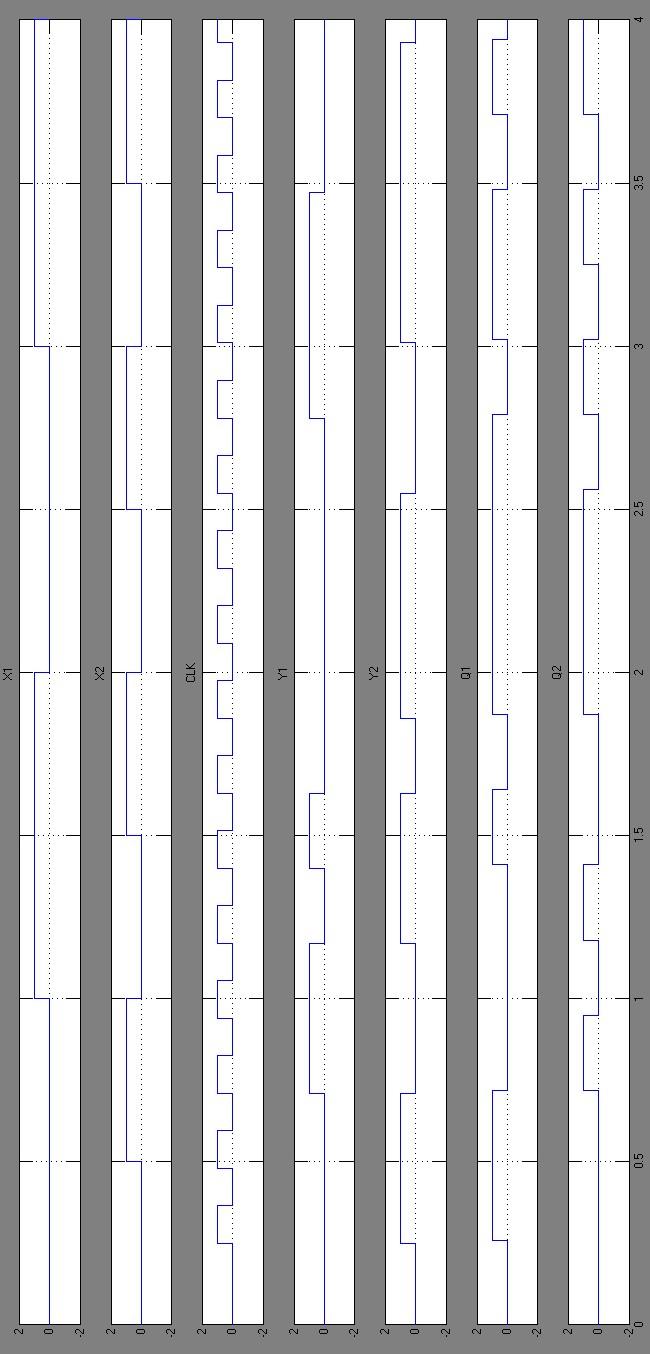

Временные диаграммы работы автомата:

Рис. 11

Поясним работу автомата по (Рис. 11):

|

Такт |

Начальное состояние |

Входное воздействие |

Следующее состояние |

Выходное состояние | ||||

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

2 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

3 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

5 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

7 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

8 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

|

9 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

10 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |