Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Программа, методические указания и контрольные задания (ЦиМПУ)

.pdf

Входы А1, А0 служат для приема адреса источника, от которого подается информация в данный момент времени. Таблица истинности данного мультиплексора приведена в таблице 3.5.

Таблица 3.5 – Таблица истинности одноразрядного мультиплексора для m = 4

Логические аргументы |

Логическая функция |

|||||

|

|

|

|

|

|

|

x0 |

x1 |

x2 |

x3 |

а1 |

а0 |

y |

0 |

x |

x |

x |

0 |

0 |

0 |

1 |

x |

x |

x |

0 |

0 |

1 |

|

|

|

|

|

|

|

x |

0 |

x |

x |

0 |

1 |

0 |

x |

1 |

x |

x |

0 |

1 |

1 |

|

|

|

|

|

|

|

x |

x |

0 |

x |

1 |

0 |

0 |

x |

x |

1 |

x |

1 |

0 |

1 |

|

|

|

|

|

|

|

x |

x |

x |

0 |

1 |

1 |

0 |

x |

x |

x |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

Запишем логическую функцию для выхода мультиплексора в

СДНФ: |

|

y = x0 ∙ a1 ∙ a0 ˅ x1 ∙ a1 ∙ a0 ˅ x2 ∙ a1 ∙ a0 ˅ x3 ∙ a1 ∙ a0 |

(3.2) |

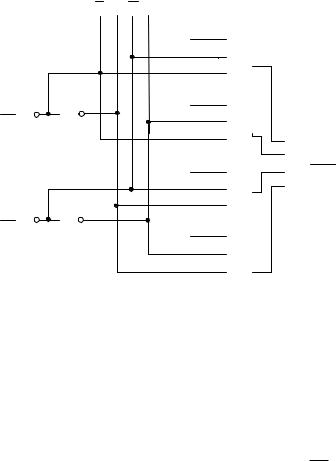

Логическая схема одноразрядного мультиплексора, построенная по логической функции (3.2) представлена на рисунке 3.5.

Для проверки правильного функционирования логической схемы одноразрядного мультиплексора проставим на выходах логических элементов значения сигналов, если a1 = 0, a0 = 1. Поскольку на выход y передается поток данных со входа x3, то схема функционирует в соответствии с таблицей истинности.

Методика синтеза одноразрядных мультиплексоров, заданных в вариантах 2 и 8, аналогична. Разница в том, что адрес будет трехразрядным.

31

|

|

|

a 1 |

a 1 |

a0 |

a 0 |

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

x0 |

0 |

& |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

1 |

1 |

1 |

|

|

x1 |

1 |

& |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

0 |

x3 |

y |

|

|

|

|

|

|

x2 |

|

& |

|

||

|

|

|

|

|

|

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x3 |

1 |

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

x3 |

|

|

Рисунок 3.4 – Логическая схема одноразрядного мультиплексора для m = 4

Впункте 7 задачи 3 (варианты 2 и 8) необходимо изучить микросхему дешифратора. Справочные данные заданной микросхемы дешифратора приведены в [3, приложения Б и В]. Основные параметры заданной микросхемы запишите в таблицу, аналогичную таблице 3.4.

Ввариантах 3, 4, 5, 7, и 9 требуется синтезировать схему дешиф-

ратора со стробированием, т. е. с разрешающим входом EN , на заданное число информационных входов (выходов). Рассмотрим пример синтеза полного двоичного дешифратора на два информационных входа. Условное графическое отображение такого дешифратора со входом разрешения приведено на рисунке 3.6.

32

x |

|

|

DC |

y |

|

|

2 |

1 |

0 |

0 |

|||

|

|

|||||

|

|

|

1 |

y1 |

||

x1 |

2 |

|

|

|

||

|

|

|

2 |

y2 |

||

|

|

EN |

3 |

y3 |

||

Рисунок 3.6 – Условное графическое обозначение двоичного дешифратора со входом разрешения

Принцип работы данного дешифратора поясняется следующей таблицей истинности (таблица 3.6).

Таблица 3.6 – Таблица истинности двоичного дешифратора

Логические аргументы |

|

|

Логические функции |

|

|||||

|

|

|

|

|

|

|

|

|

|

EN |

x1 |

|

x2 |

y0 |

|

y1 |

y2 |

|

y3 |

|

|

|

|

|

|

|

|

|

|

1 |

x |

|

x |

0 |

|

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

|

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

|

1 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

|

0 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

|

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

Примечание – Знаком «x» обозначен произвольный сигнал (0 или 1).

По данным таблицы 3.6 запишем систему логических функций в СДНФ, описывающих работу дешифратора:

33

y |

0 |

x |

x |

2 |

EN; |

|

|

1 |

|

|

|

||

y |

|

x |

x |

2 |

EN; |

|

1 |

1 |

|

|

|||

y |

2 |

x |

x |

2 |

EN; |

|

|

1 |

|

|

|

||

y |

3 |

x |

x |

2 |

EN. |

|

|

1 |

|

|

|

||

(3.3)

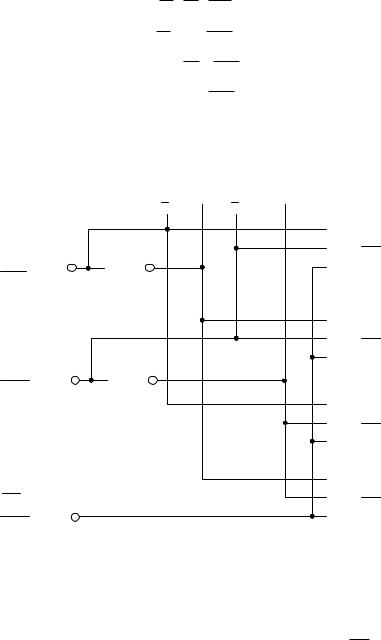

Логическая схема данного дешифратора в основном базисе со входом разрешения, построенная по системе логических функций (3.3) представлена на рисунке 3.7.

|

|

|

x |

|

x2 |

x |

|

x1 |

|

|

|

|

|

|

|

|

2 |

|

1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

0 |

1 |

|

0 |

1 |

0 |

& |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

y |

|

|

|

1 |

|

1 |

|

|

|

|

|

|

0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

1 |

|

|

|

|

||

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

& |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

y |

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

x |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

1 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

y |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

& |

1 |

|

|

EN |

1 |

|

|

|

|

|

|

|

|

y |

3 |

||

1 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 3.7 – Логическая схема двоичного дешифратора со входом разрешения

Для проверки правильности функционирования логической схемы двоичного дешифратора со входом разрешения проставим на выходах

логических элементов значения сигналов, если x1 = 1, x2 = 1, EN = 0.

34

Так как возбужден выход у3, то схема дешифратора функционирует в соответствии с таблицей истинности (таблица 3.5).

Методика синтеза двоичных дешифраторов, заданных в вариантах 3, 4, 5, 7 и 9 аналогична.

В пункте 7 задачи 3 (варианты 3, 4, 5, 7 и 9) необходимо изучить микросхему мультиплексора. Справочные данные заданной микросхемы мультиплексора приведены в [3, приложения Б и В]. Основные параметры заданной микросхемы запишите в таблицу, аналогичную по форме таблице 3.4.

Задача 4

Изучите заданное последовательностное цифровое устройство (ПЦУ) и заданную микросхему (таблица 3.7).

Таблица 3.7 – Исходные данные к задаче 4

Номер |

|

Наименование ПЦУ |

Микросхема |

||||

варианта |

|

|

|

|

|

|

|

1 |

|

Асинхронные RS-триггеры |

ЭКР1554ИЕ10 |

||||

2 |

|

Синхронные RS-триггеры со статиче- |

ЭКР1594ИР8 |

||||

|

|

ским управлением |

|

||||

3 |

|

Синхронные D-триггеры со статиче- |

ЭКР1564ИЕ6 |

||||

|

|

ским управлением |

|

||||

4 |

|

JK-триггеры со статическим управле- |

ЭКР1554ИР35 |

||||

|

|

нием |

|

||||

5 |

|

T-триггеры со статическим управлени- |

ЭКР1554ИР23 |

||||

|

|

ем |

|

||||

6 |

|

|

|

|

|

|

ЭКР1554ИЕ18 |

|

Асинхронные RS-триггеры |

||||||

|

|

|

|||||

7 |

|

Синхронные RS-триггеры со статиче- |

ЭКР1564ИР9 |

||||

|

|

ским управлением |

|

||||

8 |

|

Синхронные D-триггеры со статиче- |

ЭКР1594ИЕ7 |

||||

|

|

ским управлением |

|

||||

9 |

|

JK-триггеры со статическим управле- |

ЭКР1594ИР22 |

||||

|

|

нием |

|

||||

10 |

|

T-триггеры со статическим управлени- |

ЭКР1554ИЕ23 |

||||

|

|

ем |

|

||||

|

Методические указания по выполнению задачи 4 |

||||||

35

Взадаче 4 рассматриваются следующие ПЦУ: триггеры, регистры

исчетчики. Перед решением задачи 4 изучите по [1, с. 128–170] темы № 2.2 «Триггерные устройства», № 2.3 «Регистры памяти и сдвига» и № 2.4 «Счетчики и делители частоты». Изучите назначение и принцип построения указанных ПЦУ, а также примеры микросхем.

Описание заданного триггера выполните в следующем порядке: 1. Дайте определение заданного триггера, начертите его УГО и

укажите назначение выводов (входов и выходов).

2. В вариантах 1 и 6 задачи 4 начертите таблицу состояний асин-

хронного RS-триггера (для варианта 6 – RS -триггера). Получите его характеристическое уравнение и постройте логическую схему.

В остальных вариантах задачи 4 начертите таблицу состояний заданного триггера, совмещенную с таблицей истинности комбинационной схемы (КС), и получите логические функции Sn и R n для вы-

ходов КС. Постройте логическую схему заданного триггера на основе асинхронного RS -триггера и разработанной КС. Поясните принцип работы, укажите достоинства и недостатки.

Описание заданной микросхемы ПЦУ выполните в следующем порядке:

1.Дайте определение и поясните назначение заданного ПЦУ.

2.Зарисуйте по [4, приложение В] УГО заданной микросхемы ПЦУ и укажите назначение выводов.

3.Зарисуйте по [4, приложение В] таблицу состояний заданной микросхемы ПЦУ, укажите возможные режимы работы и условия их обеспечения.

4.Определите по [4, приложение Б] основные статические и динамические параметры заданной микросхемы ПЦУ и запишите в таблицу, аналогичную по форме таблице 4.2.

36

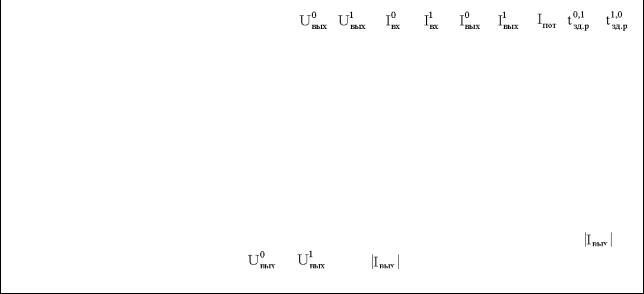

Таблица 4.2 – Основные статические и динамические параметры заданных микросхем (образец заполнения)

Международ- |

Условное обо- |

Схемо- |

UП |

|

|

|

|

|

|

|

|

|

|

|

(tP |

(tP |

|

ное обозначе- |

значение по |

техника |

(VCC) |

(V ), |

(V ), |

(I ), |

(I |

|

), |

(I ), |

(I |

|

), |

(I ), |

|||

IH |

OH |

LH), не |

HL), не |

||||||||||||||

ние микро- |

ГОСТ 17021-88 |

|

|

OL |

OH |

IL |

|

|

OL |

|

|

CC |

|||||

|

|

не |

не ме- |

не |

не |

не |

не |

|

не |

||||||||

схем |

(прототип) |

|

|

|

более |

более |

|||||||||||

|

|

более |

нее |

более |

более |

более |

более |

более |

|||||||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

В |

В |

В |

мкА |

мкА |

мА |

мА |

мкА |

нс |

нс |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

IN74ACT273 |

ЭКР1594ИР35 |

КМОП |

5 |

0,1 |

4,9 |

– 1,0 |

1,0 |

24 |

– 24 |

80 |

11 |

12 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

IN74HC163A |

ЭКР1564ИЕ18 |

КМОП |

5 |

0,1 |

4,9 |

– 1,0 |

1,0 |

4 |

– 4 |

40 |

23 |

25 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Примечания |

|

|

|

|

|

1 |

В скобках указаны международные обозначения соответствующих параметров. |

|

|||

2 |

Параметры указаны для напряжения источника питания UП = 5 В и рабочей температуры от ми- |

||||

нус 40 до плюс 85°С. Максимальный потребляемый ток Iпот указан для выходного тока |

= 0 |

||||

мкА, а уровни выходных напряжений |

и |

– для |

≤ 50 мкА. |

|

|

37

ЛИТЕРАТУРА

1 Богородов, В. И. Цифровые и микропроцессорные устройства : учеб. пособие / В. И. Богородов. – Минск : УО ВГКС, 2015. – 340 с.

2 Калабеков, Б. А. Цифровые устройства и микропроцессорные системы : учеб. для техникумов связи / Б. А. Калабеков. – М. : Горячая линия – Телеком, 2007. – 336 с.

3 Цифровые и микропроцессорные устройства : лабораторный практикум для учащихся специальностей 2-45 01 33 – Сети телекоммуникаций,

2-45 01 32 – Системы радиосвязи, |

радиовещания и телевидения. |

В 4 ч. / сост. В. И. Богородов. – Минск : |

ВГКС, 2009. – Ч. 1 – 84 с. |

4 Цифровые и микропроцессорные устройства : лабораторный практикум для учащихся специальностей 2-45 01 33 – Сети телекоммуникаций,

2-45 01 32 – Системы радиосвязи, |

радиовещания и телевидения. |

В 4 ч. / сост. В. И. Богородов. – Минск : |

ВГКС, 2009. – Ч. 2 – 63 с. |

38

СОДЕРЖАНИЕ |

|

ВВЕДЕНИЕ ........................................................................................ |

3 |

КОНТРОЛЬНЫЕ ЗАДАНИЯ............................................................ |

9 |

Задача 1 ............................................................................................... |

9 |

Методические указания по выполнению задачи 1 ....................... |

10 |

Задача 2 ............................................................................................. |

18 |

Методические указания по выполнению задачи 2 ....................... |

19 |

Задача 3 ............................................................................................. |

24 |

Методические указания по выполнению задачи 3 ....................... |

25 |

Задача 4 ............................................................................................. |

35 |

Методические указания по выполнению задачи 4 ....................... |

35 |

ЛИТЕРАТУРА ................................................................................. |

38 |

39

Учебное издание

ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА

Методические указания и контрольные задания для учащихся заочной формы обучения специальностей

2-45 01 33 – Сети телекоммуникаций 2-45 01 32 – Системы радиосвязи, радиовещания и телевидения

Составитель Богородов Владимир Ильич

Редактор С.В. Андреева

Компьютерная верстка В. Н. Масленникова

План 2014/2015 уч. г., поз. __

Подписано в печать ___________. Формат 60*84/16. Бумага офсетная. Гарнитура «Times».

Печать цифровая.

Усл. печ. л. ___. Уч.-изд. л. ___. Тираж ___ экз. Заказ ___.

Издатель и полиграфическое исполнение:

Учреждение образования «Высший государственный колледж связи» ЛИ № 02330/0131902 от 03.01.2007.

Ул. Ф. Скорины, 8/2, 220114, Минск