Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Программа, методические указания и контрольные задания (ЦиМПУ)

.pdf

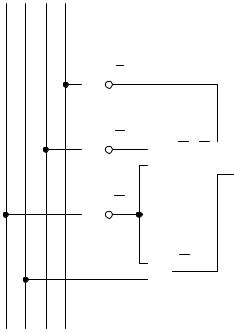

3.2 Построим логическую схему устройства по выражению (2.1). Для этого потребуется:

–два логических элемента 2 И;

–один логический элемент 3 ИЛИ;

–три логических элемента 3 НЕ.

Логическая схема устройства в базисе И, ИЛИ, НЕ, построенная по логической функции (2.1), представлена на рисунке 2.3.

X1 X2 |

X3 |

X4 |

0 1 0 1

1 |

X4 |

|

0 |

1 |

X 3 |

|

1 |

1 |

X1 |

|

1 |

& |

X |

1 |

X |

3 |

|

|

|||||

|

|

|

|

1

&X 1 X 2

1

1 |

f |

(X ,X ,X ,X |

) |

|||

|

||||||

|

11 |

1 |

2 |

3 |

4 |

|

|

1 |

|

|

|

|

|

Рисунок 2.3 – Логическая схема устройства в базисе И, ИЛИ, НЕ

вМДНФ

4.Рассмотрим пример синтеза КЦУ в базисе И-НЕ для той же

ЛФ.

4.1 Преобразуем ЛФ (2.1) в базис И-НЕ, используя правило де Моргана:

21

f |

11(МДНФ) |

(X ,X |

,X |

,X |

4 |

) X |

4 |

X |

X |

3 |

X |

X |

2 |

|

|

|

1 |

2 |

3 |

|

|

1 |

|

1 |

|

|

|||||

X4 X1 X3 X1 X2 X4 X1 X3 X1 X2

X4 |(X1 |X3)|(X1 |X2 ).

(2.2)

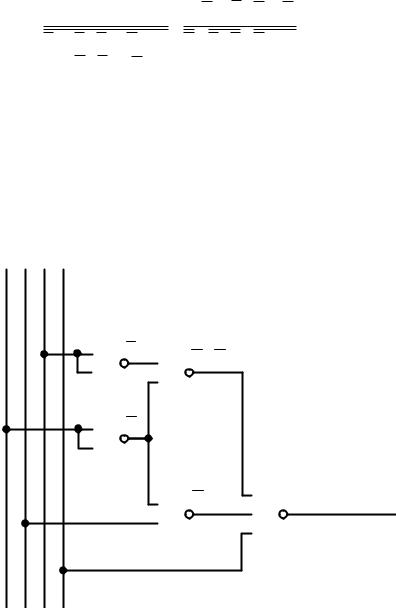

4.2 Построим логическую схему устройства в базисе И-НЕ по выражению (2.2), при этом одиночные отрицания аргументов реализуем на основе ЛЭ 2 И-НЕ с объединенными входами. Для этого необходимо использовать:

–четыре логических элемента 2 И-НЕ;

–один логический элемент 3 И-НЕ.

Логическая схема устройства в базисе И-НЕ представлена на рисунке 2.4.

X X X |

3 |

X |

|

1 |

2 |

4 |

|

0 1 0 1

&

&

X3 1

X1

1

&

&

X1 |X 3

0

X1 |X 2

0

&

f11 (X1, X2 , X3 , X4 )

1

Рисунок 2.4 – Логическая схема устройства в базисе И-НЕ

22

4.3 Построим принципиальную электрическую схему устройства в базисе И-НЕ на микросхемах стандартной логики схемотехники КМОП серии 1554. Для этого по приложениям Б и В в [3] выбираем стандартные микросхемы интегральных ЛЭ серии 1554 и соединяем их между собой в соответствии с логической схемой на рисунке 2.4. Выбираем микросхему ЭКР1554ЛА3 (IN74AC00N), в одном корпусе которой выполнено четыре ЛЭ 2 И-НЕ, а также ЭКР1554ЛА4 (IN74AC10N) – три ЛЭ 3 И-НЕ (два останутся свободными). Принципиальная электрическая схема устройства в базисе И- НЕ представлена на рисунке 2.5. На схеме указаны буквеннопозиционные обозначения микросхем по ГОСТ 2.710 – 81, номера выводов, а также уровни сигналов для пятого набора аргументов (уровни сигналов указаны под линиями выводов микросхем).

X X |

|

1 |

2 |

X3

X4

|

|

|

|

|

|

DD1 - ЭКР1554ЛА3, |

|

|

|

||||||

0 |

1 |

0 |

1 |

|

DD2 -ЭКР1554ЛА4. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

DD1.1 |

|

DD1.3 |

|

|

|

|

|

||||

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

& |

3 |

9 |

|

& |

8 |

|

|

|

|

|||

|

|

|

2 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

1 |

10 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

0 |

|

Вывод 14 DD1, DD2 - |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

DD1.2 |

|

|

|

|

|

питание, вывод 7 - |

|||||

|

|

|

|

|

|

|

|

|

общий. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

4 |

& |

6 |

|

|

|

|

|

|

|

|

||

|

|

|

5 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

1 |

|

DD1.4 |

|

DD2.1 |

|||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

1 |

& 12 |

|

|||

|

|

|

|

|

|

|

|

12 & |

|

|

|||||

|

|

|

|

|

|

|

|

11 |

2 |

f11 (X1, X2 , X3 , X4 ) |

|||||

|

|

|

|

|

|

|

|

13 |

|

0 |

13 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.5 – Принципиальная электрическая схема устройства в базисе И-НЕ

23

4.4 Определим среднюю задержку распространения сигнала от входа к выходу устройства и среднюю потребляемую мощность.

В худшем случае сигнал передается через три ЛЭ. Для расчета средней задержки возьмем данные из приложения Б в [3]. В результате получаем суммарную среднюю задержку распространения сигнала от

входа к выходу устройства |

6 |

22,75 |

нс. |

tзд.р.ср (2 7,75 7,25) 10 |

Для расчета средней потребляемой мощности всей схемы необходимо расчетным путем определить среднюю потребляемую мощность каждой микросхемы путем умножения среднего потребляемого тока ( см. [3], приложение Б ) на напряжение источника питания. В результате получаем суммарную среднюю потребляемую

мощность

P |

6 |

5 400 10 |

6 |

400 |

(40 40) 10 |

|

|||

пот.ср |

|

|

|

|

мкВт.

5. Проверим правильность функционирования логических и принципиальной схем КЦУ (рисунки 2.3...2.5). Для этого проставим на выходах всех логических элементов значения сигналов для пятого набора аргументов. Поскольку на выходах схем единичный уровень сигнала, то они функционируют в соответствии с таблицей истинности (см. значение логической функции f11 для пятого набора аргументов в

таблице 2.1).

Задача 3

1. Разработайте в основном базисе логическую схему комбинационного цифрового устройства (КЦУ) и изучите микросхему (таблице

3.1.)

Таблица 3.1 – Исходные данные к задаче 3

Номер |

Наименование КЦУ |

Микросхема |

варианта |

|

|

1 |

2 |

3 |

|

|

|

1 |

Преобразователь кода 8421 в код «с избытком 3» |

ЭКР1554КП7 |

|

|

|

2 |

Мультиплексор на восемь входов без стробирования |

ЭКР1554ИД7 |

3 |

Дешифратор кода 2421 на десять выходов со стро- |

ЭКР1554КП15 |

|

бированием |

|

|

|

|

4 |

Шифратор для преобразования десятичных цифр в |

ЭКР1554КП12 |

|

код «с избытком 3» со стробированием |

|

|

|

|

24

5 |

Дешифратор кода 7421 на десять выходов со стро- |

ЭКР1554КП11 |

|

бированием |

|

|

|

|

6 |

Преобразователь кода 8421 в код Грея |

ЭКР1554КП2 |

|

|

|

7 |

Шифратор для преобразования десятичных цифр в |

ЭКР1554КП18 |

|

код 7421 со стробированием |

|

|

|

|

8 |

Мультиплексор на восемь входов со стробировани- |

ЭКР1554ИД14 |

|

ем |

|

|

|

|

9 |

Дешифратор кода «с избытком 3» на десять выходов |

ЭКР1554КП14 |

|

со стробированием |

|

|

|

|

10 |

Преобразователь кода «с избытком 3» в код 8421 |

ЭКР1554КП16 |

|

|

|

2.Дайте определение и поясните назначение заданного КЦУ.

3.Приведите его условное графическое обозначение и поясните назначение выводов.

4.Составьте таблицу истинности для заданного КЦУ.

5.Запишите логические функции для выходов заданного КЦУ в базисе И, ИЛИ, НЕ (для преобразователей кодов логические функции минимизировать табличным методом с помощью карт Карно).

6.Постройте логическую схему КЦУ в основном базисе.

7.Проверьте правильность функционирования построенной логической схемы КЦУ для четвертой строки таблицы истинности.

8.Изучите заданную микросхему КЦУ. Начертите УГО, укажите назначение микросхемы, начертите таблицу состояний и поясните принцип работы. Укажите основные статические и динамические параметры в виде таблицы.

Методические указания по выполнению задачи 3

Взадаче 3 рассматриваются следующие типовые КЦУ: преобразователи кодов, мультиплексоры, шифраторы и дешифраторы. Перед решением задачи 3 изучите тему № 2.1 «Типовые КЦУ» по [1, с. 91–

127].

Ввариантах 1, 6 и 10 задачи 3 требуется синтезировать в основном базисе схемы преобразователей кодов. Рассмотрим пример синтеза преобразователя кода 8421 в код 2421 при минимизации логических функций с помощью карт Карно. Условное графическое обозначение такого преобразователя кода представлено на рисунке 3.1.

25

X1

X2

X3

X4

1 |

X/Y |

1 |

2 |

|

2 |

4 |

|

4 |

8 |

|

2 |

|

|

|

Y1

Y2 Y3

Y4

Рисунок 3.1 – Условное графическое обозначение преобразователя кода 8421 в код 2421

Закон функционирования преобразователя кода представлен в таблице 3.2.

Таблица 3.2 – Таблица истинности преобразователя кода 8421 в код

2421

Десятичное |

|

|

Код 8421 |

|

|

Код 2421 |

|

||||

число |

X |

4 |

X |

3 |

X |

2 |

X |

Y |

Y |

Y |

Y |

|

|

|

|

1 |

4 |

3 |

2 |

1 |

|||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|||

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|||

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|||

3 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|||

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|||

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|||

6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

|||

7 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|||

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|||

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|||

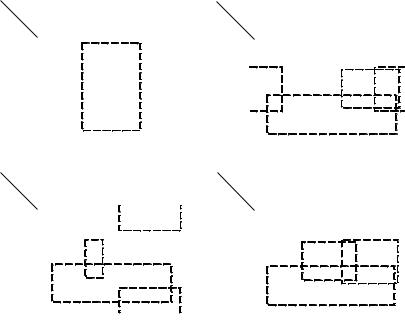

На основании ним карты Карно

выходов Y1 |

, …, Y4 |

таблицы истинности преобразователя кодов запол- (рисунок 3.2) и запишем логические функции для в МДНФ.

26

|

|

|

X |

X |

|

|

|

|

|

|

|

|

|

|

X |

X |

2 |

|

1 |

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

11 |

|

|

10 |

|

|

|

|

00 |

0 |

|

1 |

|

|

|

1 |

|

|

0 |

|

Y |

|

: |

01 |

0 |

|

1 |

|

|

|

1 |

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

Ф |

|

Ф |

|

|

|

Ф |

|

|

Ф |

|

|

|

|

10 |

0 |

|

1 |

|

|

|

Ф |

|

|

Ф |

|

|

|

|

|

|

|

|

Y X . |

|

|

|

||||

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

|

|

|

X |

X |

|

|

|

|

|

|

|

|

|

|

X |

X |

2 |

|

1 |

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

11 |

|

|

10 |

|

|

|

|

00 |

0 |

|

0 |

|

|

|

1 |

|

|

1 |

|

Y |

|

: |

01 |

0 |

|

1 |

|

|

|

0 |

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

Ф |

|

Ф |

|

|

|

Ф |

|

|

Ф |

|

|

|

|

10 |

1 |

|

1 |

|

|

|

Ф |

|

|

Ф |

|

|

|

|

|

|

Y X |

4 |

X |

2 |

X |

3 |

X |

X |

2 |

X . |

|

|

|

|

|

2 |

|

|

1 |

|

3 |

||||

|

|

|

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

|

|

11 |

|

|

10 |

|||

|

|

|

00 |

0 |

|

0 |

|

|

|

|

0 |

|

|

0 |

||||

|

|

|

01 |

1 |

|

0 |

|

|

|

|

1 |

|

|

1 |

||||

Y |

: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

Ф |

|

Ф |

|

|

|

|

Ф |

|

|

Ф |

||||

|

|

|

10 |

1 |

|

1 |

|

|

|

|

Ф |

|

|

Ф |

||||

|

|

|

|

|

Y X |

4 |

X |

2 |

X |

3 |

X |

X |

. |

|

||||

|

|

|

|

|

3 |

|

|

|

|

|

1 |

|

3 |

|

|

|||

|

|

|

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

|

|

11 |

|

|

10 |

|||

|

|

|

00 |

0 |

|

0 |

|

|

|

|

0 |

|

|

0 |

||||

|

|

|

01 |

0 |

|

1 |

|

|

|

|

1 |

|

|

1 |

||||

Y |

: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

Ф |

|

Ф |

|

|

|

|

Ф |

|

|

Ф |

||||

|

|

|

10 |

1 |

|

1 |

|

|

|

|

Ф |

|

|

Ф |

||||

|

|

|

|

|

Y X |

4 |

X |

X |

X |

2 |

X |

. |

||||||

|

|

|

|

|

4 |

|

|

|

1 |

|

|

3 |

|

|

3 |

|

||

Рисунок 3.2 – Карты Карно для преобразователя кода 8421 в код 2421

Y1 X1; |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Y2 X4 X2 X 3 X1 X 2 |

X3 |

|

|||||||

; |

(3.1) |

||||||||

|

|

|

|

|

|

|

|

|

|

Y3 X4 X2 X3 X 1 X3; |

|

|

|

||||||

Y4 X4 X1 X3 X2 X3. |

|

|

|

||||||

|

|

|

|||||||

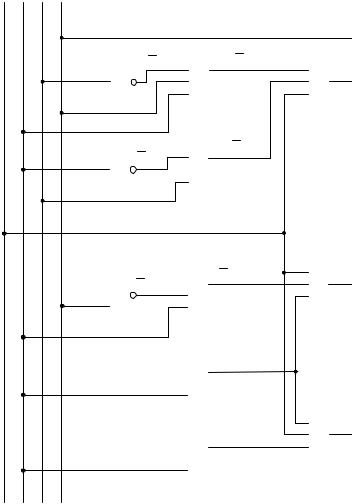

Логическая схема преобразователя кода 8421 в код 2421 в основном базисе, построенная по логическим функциям (3.1), представлена на рисунке 3.3.

Для проверки правильности функционирования логической схемы преобразователя кода проставим на выходах логических элементов значения сигналов для входного кодового слова 0011. Поскольку на выходах схемы устанавливается кодовое слово 0011, то преобразователь кода функционирует в соответствии с таблицей истинности.

Следует помнить, что проверка правильности функционирования только по одному входному набору является неполной.

27

Методика синтеза преобразователей кодов, заданных в вариантах 1, 6 и 10, аналогична. Для составления таблицы истинности следует использовать данные таблицы 3.3.

X |

4 |

X |

3 |

X |

2 |

X |

|

|

|

1 |

|||

0 |

|

0 |

|

1 |

1 |

|

1 |

X |

2 |

& |

|

|||

|

|

||

|

0 |

|

|

1 |

X |

3 |

& |

|

|

|

|

|

1 |

|

|

|

X |

1 |

& |

1 |

|

||

|

|

||

|

|

|

|

|

0 |

|

|

&

&

&

&

X |

·X ·X |

3 |

|

1 |

2 |

1 |

|

0 |

|

|

|

|

|

|

X |

·X |

3 |

2 |

|

|

1 |

|

|

X |

·X |

3 |

1 |

1 |

|

|

|

0 |

|

|

|

X |

·X |

3 |

2 |

|

|

0 |

|

|

|

|

1 |

X |

·X |

3 |

1 |

|

|

0 |

|

|

Y1 1

Y2 1

Y3 0

Y4 0

Рисунок 3.3 – Логическая схема преобразователя кода 8421 в код 2421 в базисе И, ИЛИ, НЕ

28

Таблица 3.3 – Двоично-десятичные коды

Десятичное |

|

Двоично-десятичные коды |

|

||

число |

8421 |

2421 |

Грея |

|

«с избытком 3» |

0 |

0000 |

0000 |

0000 |

|

0011 |

1 |

0001 |

0001 |

0001 |

|

0100 |

2 |

0010 |

0010 |

0011 |

|

0101 |

3 |

0011 |

0011 |

0010 |

|

0110 |

4 |

0100 |

0100 |

0110 |

|

0111 |

5 |

0101 |

1011 |

0111 |

|

1000 |

6 |

0110 |

1100 |

0101 |

|

1001 |

7 |

0111 |

1101 |

0100 |

|

1010 |

8 |

1000 |

1110 |

1100 |

|

1011 |

9 |

1001 |

1111 |

1101 |

|

1100 |

Примечание – Код «с избытком 3» часто называют кодом 8421+3

Впункте 7 задачи 3 (варианты 1, 6 и 10) необходимо изучить микросхему мультиплексора. Справочные данные заданной микросхемы мультиплексора приведены в [3, приложения Б и В]. Основные параметры заданной микросхемы запишите в таблицу, аналогичную по форме таблицы 3.4.

Ввариантах 2 и 8 задачи 3 требуется синтезировать в основном базисе схему одноразрядного мультиплексора на заданное число информационных входов m. Рассмотрим пример синтеза одноразрядного мультиплексора на четыре информационных входа Y (m = 4).

Условное графическое отображение такого мультиплексора приведено на рисунке 3.4.

x |

I |

MUX |

|

|

|

|

|||

|

0 |

|

|

|

x |

0 |

|

|

|

I |

|

|

||

|

1 |

|

|

|

x |

|

1 |

|

|

|

I |

|

|

|

2 |

|

|

||

x |

|

2 |

Y |

y |

3 |

I |

|||

a0 |

3 |

|

|

|

A |

|

|

||

a |

|

0 |

|

|

|

A |

|

|

|

1 |

|

|

||

|

|

1 |

|

|

Рисунок 3.4 – Условное графическое обозначение одноразрядного мультиплексора для m = 4

29

30

Таблица 3.4 – Основные статические и динамические параметры заданных микросхем (образец заполнения)

Международ- |

Условное обо- |

Схемо- |

UП |

|

|

|

|

|

|

|

|

|

|

|

(tP |

(tP |

|

ное обозначе- |

значение по |

техника |

(VCC) |

(V ), |

(V ), |

(I ), |

(I |

|

), |

(I ), |

(I |

|

), |

(I ), |

|||

IH |

OH |

LH), не |

HL), не |

||||||||||||||

ние микро- |

ГОСТ 17021-88 |

|

|

OL |

OH |

IL |

|

|

OL |

|

|

CC |

|||||

|

|

не |

не ме- |

не |

не |

не |

не |

|

не |

||||||||

схем |

(прототип) |

|

|

|

более |

более |

|||||||||||

|

|

более |

нее |

более |

более |

более |

более |

более |

|||||||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

В |

В |

В |

мкА |

мкА |

мА |

мА |

мкА |

нс |

нс |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

IN74HC139A |

ЭКР1564ИД14 |

КМОП |

5 |

0,1 |

4,9 |

– 1,0 |

1,0 |

4 |

– 4 |

40 |

29 |

29 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

IN74HC251A |

ЭКР1564КП15 |

КМОП |

5 |

0,1 |

4,9 |

– 1,0 |

1,0 |

4 |

– 4 |

80 |

46 |

46 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Примечания:

1.В скобках указаны международные обозначения соответствующих параметров.

2.Параметры указаны для напряжения источника питания UП = 5 В и рабочей температуры от минус

40 до плюс 85°С. Максимальный потребляемый ток Iпот указан для выходного тока  = 0 мкА, а уровни выходных напряжений

= 0 мкА, а уровни выходных напряжений  и

и  – для

– для  ≤ 50 мкА.

≤ 50 мкА.