Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Методические указания и задания к курсовому проекту (ЦиМПУ)

.pdfЛИТЕРАТУРА

1 Микросхемы интегральные. Термины и определения : ГОСТ 17021-88 ЕСКД. – Введ. 1990-01-01. – М. : Изд-во стандартов, 1989.

2 Обозначения буквенно-позиционные в электрических схемах : ГОСТ 2.710-81 ЕСКД. – Введ. 1983-01-01. – М. : Изд-во стандартов, 1982.

3 Обозначения условные графические в электрических схемах. Элементы цифровой техники : ГОСТ 2.743-91 ЕСКД. – Введ. 1993- 01-01. – М. : Изд-во стандартов, 1992.

4 Общие требования к текстовым документам : ГОСТ 1.105-95 ЕСКД. – Введ. 1997-01-01. – М. : Изд-во стандартов, 1996.

5 Стандарт предприятия. Курсовое и дипломное проектирование. Общие требования: СТП 01–2016. – Введ. 2016–01–01. –Минск : УО БГАС, 2016. – 100 с.

6 Браммер, Ю. А. Цифровые устройства: учеб. пособие для вузов / Ю. А. Браммер, И. М. Пащук. – М. : Высш. Шк., 2004. – 229 с.

7 Калабеков, Б. А. Цифровые устройства и микропроцессорные системы : учеб. для техникумов связи / Б. А. Калабеков. – М. : Горячая линия – Телеком, 2002. – 336 с.

8 Лысиков, Б. Г. Цифровая и вычислительная техника : учеб. / Б. Г. Лысиков. – Минск : Экоперспектива, 2002. – 264 с.

9 Угрюмов, Е. П. Цифровая схемотехника : учеб. пособие для вузов. – 2-е изд., перераб. и доп. / Е.П. Угрюмов. – Спб. : БХВ-

Петербург, 2005. – 800 с.

10 Фролкин, В. Т. Импульсные и цифровые устройства : учеб. пособие для вузов / В. Т. Фролкин, Л. Н. Панов – М. : Радио и связь,

1992. – 336 с.

11 Цифровые и микропроцессорные устройства : Лабораторный практикум для студентов специальностей 2-45 01 03 – Сети телекоммуникаций, 2-45 01 02 – Системы радиосвязи, радиовещания и телевидения. В 4 ч. / сост. В. И. Богородов. – Минск : ВГКС, 2009. – Ч.1

– 84 с; Ч.2 – 63 с.

12 Цифровые интегральные микросхемы : справочник, 2-е изд., перераб и доп. / М. И. Богданович [и др.]. – Мн. : Беларусь,

Полымя, 1996. – 605 с.

13 НИКТРУП «Белмикросистемы» [Электронный ресурс]. – 2005. –

Режим доступа: http://www.bms.by.

61

ПРИЛОЖЕНИЕ А (справочное)

Пример синтеза счетчика на JK-триггерах

Методику синтеза счетчика на JK-триггерах рассмотрим на примере синтеза логической схемы счетчика с коэффициентом пересчета Kпер = 10 при использовании карт Карно.

Необходимое число триггеров будет определяться как минимальное n, удовлетворяющее неравенству 2n ≥ Kпер. В данном случае число триггеров n = 4.

В счетчике с коэффициентом пересчета Kпер = 10 десять состояний, причем каждый десятый импульс сбрасывает счетчик в нулевое состояние. Переход счетчика из текущего в следующее состояние связан с переключением триггеров. Для переключения триггеров счетчика в требуемые состояния (таблица А.1) на их входах J и K необходимы определенные уровни сигналов. В таблице А.2 показаны все возможные переходы состояний триггера и требуемые для этих переходов уровни сигналов на входах J и K. На основании таблицы А.2 в таблице А.1 указаны уровни сигналов на входах J и K, которые обеспечивают переходы счетчика в следующее состояние.

Таблица А.1 – Таблица переходов счетчика с коэффициентом пересчета Kпер = 10, совмещенная с таблицей истинности комбинационных схем возбуждения входов J и K триггеров

Номер |

|

Текущее |

|

|

Следующее |

|

Уровни сигналов на входах триггеров |

|||||||||||

входно- |

|

состояние |

|

|

|

состояние |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

го |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

импуль |

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

|

Q2 |

Q1 |

|

Q0 |

J3 |

K3 |

J2 |

K2 |

J1 |

K1 |

J0 |

K0 |

са |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

|

7 |

8 |

|

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

|

1 |

0 |

X |

0 |

X |

0 |

X |

1 |

X |

2 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

|

0 |

0 |

X |

0 |

X |

1 |

X |

X |

1 |

3 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

|

1 |

0 |

X |

0 |

X |

X |

0 |

1 |

X |

4 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

|

0 |

0 |

X |

1 |

X |

X |

1 |

X |

1 |

5 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

|

1 |

0 |

X |

X |

0 |

0 |

X |

1 |

X |

62

Окончание таблицы А.1

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

6 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

X |

X |

0 |

1 |

X |

X |

1 |

7 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

X |

X |

0 |

X |

0 |

1 |

X |

8 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

X |

X |

1 |

X |

1 |

X |

1 |

9 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

X |

0 |

0 |

X |

0 |

X |

1 |

X |

10 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

X |

1 |

0 |

X |

0 |

X |

X |

1 |

Таблица А.2 – Таблица переходов JK-триггера |

|

|

|

|

|

Вид перехода |

Уровни сигналов на входах |

|

триггера |

J |

K |

0 0 |

0 |

X |

0 1 |

1 |

X |

1 0 |

X |

1 |

1 1 |

X |

0 |

Примечание – Знак «X» означает произвольный уровень |

||

сигнала (0 или 1). |

|

|

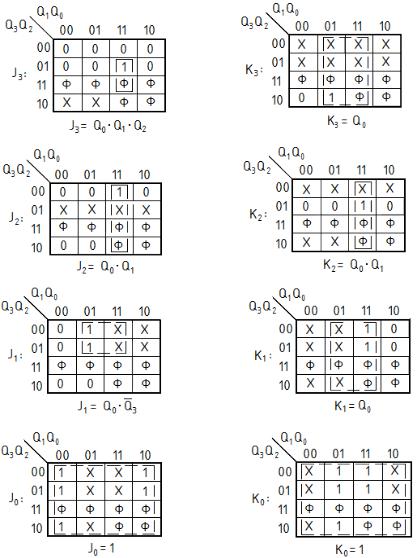

Пусть к моменту подачи первого импульса счетчик находился в состоянии 0000. Под действием этого импульса должно быть обеспечено новое состояние 0001 (таблица А.1). Следовательно, в триггере младшего разряда T0 происходит переход вида 0 1, обеспечиваемый при следующих уровнях на информационных входах: J0 = 1, K0 = X. В остальных триггерах происходит переход вида 0 0, который обеспечивается

уровнями J1 = 0, K1 = X, J2 = 0, K2 = X, J3 = 0, K3 = X. Эти значения занесены в клетки карт Карно для входов J и K всех

триггеров, соответствующие состоянию счетчика 0000 (рисунок А.1). Пользуясь таблицей А.1, можно заполнить карты Карно для входов J и K всех триггеров счетчика. При этом следует помнить, что уровни сигналов на входах J и K являются логическими функциями текущего состояния триггеров и на картах Карно (рисунок А.1) под Q3, Q2, Q1, Q0 понимается текущее состояние счетчика, т. е. перед поступлением на вход счетчика очередного импульса. На картах Карно знаком «Ф»

63

обозначены неопределенные значения функций возбуждения входов J и K, соответствующие лишним состояниям счетчика.

Рисунок А.1 – Карты Карно для счетчика с коэффициентом пересчета Kпер = 10

64

Следует помнить, что при минимизации не полностью заданных логических функций произвольные и неопределенные значения функции можно доопределять с целью упрощения результата минимизации. Следовательно, на картах Карно при записи результата минимизации в МДНФ в замкнутые области следует объединять клетки, заполненные единицами, а также произвольными и неопределенными значениями логической функции.

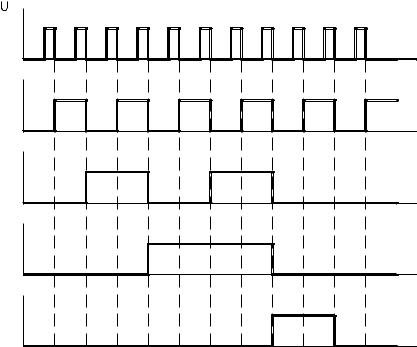

По картам Карно запишем следующие выражения для функций возбуждения входов J и K всех триггеров счетчика в МДНФ

(А.1)

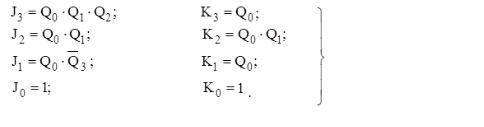

Логическая схема счетчика, построенная по логическим функциям (А.1), представлена на рисунке А.2.

65

Рисунок А.2 – Логическая схема счетчика на JK-триггерах с

коэффициентом пересчета Kпер = 10

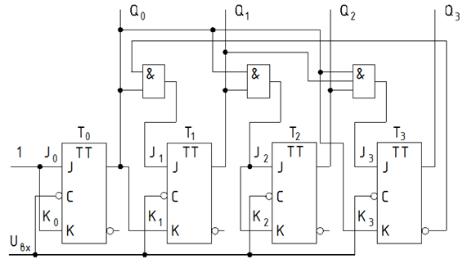

Работа счетчика (рисунок А.2) поясняется временными диаграммами, приведенными на рисунке А.3 (число входных импульсов N определяется по формуле N = Kпер + 1).

66

Q

Q

Q

Q

вх |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

|

t

0

t

1

t

2

t

3

t

Рисунок А.3 – Временные диаграммы работы счетчика с коэффициентом пересчета Kпер = 10

Из временных диаграмм следует, что каждый десятый импульс сбрасывает счетчик в исходное нулевое состояние, а одиннадцатый начинает новый цикл работы, повторяющий предыдущий.

Синтез счетчика с заданным коэффициентом пересчета выполните по вышерассмотренной методике.

67

ПРИЛОЖЕНИЕ Б

(обязательное)

Примеры оформления заданий по курсовому проектированию к темам № 1…5

Б.1 Пример оформления задания к теме № 1

Учреждение образования «Белорусская государственная академия связи»

|

(наименование высшего учебного заведения) |

Факультет |

электросвязи (или заочного и дистанционного образования) |

«УТВЕРЖДАЮ» |

|

Зав. кафедрой |

ИКТ |

«____» _______________2015 г.

ЗАДАНИЕ

по курсовому проектированию

Студенту |

3 курса гр.ТЭ112 Н. В. Ивановой |

1.Тема проекта «Устройство умножения двоичных чисел» по дисциплине «Цифровые и микропроцессорные устройства»,

вариант № 1.1.

2.Сроки сдачи студентом законченного 01.04.2015 г.

проекта |

|

3. Исходные данные к проекту |

Множимое A = 14(10) = 1110(2). |

Множитель B = 9(10) = 1001(2). Коэффициент пересчета счетчика

Кпер = 9. Микросхемы схемотехники КМОП серий 1594 и 5564.

4. Содержание расчетно-пояснительной записки (перечень подлежащих разработке вопросов) Введение.

1 Описание принципа работы заданной структурной

электрической схемы устройства умножения двоичных чисел.

2 Теоретическое обоснование и логическое проектирование

узлов устройства.

2.1Назначение и принцип построения матричных умножителей двоичных чисел.

2.2Разработка логической схемы счетчика с коэффициентом

68

пересчета Кпер = 9.

2.3Разработка логической схемы матричного умножителя четырехразрядных двоичных чисел.

2.4Разработка логической схемы двухразрядного двоичного сумматора с параллельным переносом в базисе И, ИЛИ, НЕ. 3 Анализ и выбор элементной базы.

4 Разработка и описание принципиальной электрической схемы устройства.

5 Расчет быстродействия и потребляемой мощности. Заключение.

Литература.

5. Перечень графического материала (с точным указанием обязательных чертежей и графиков)

Лист 1. Умножитель двоичных чисел. Схема логическая

(формат А3).

Лист 2. Устройство умножения двоичных чисел. Схема

электрическая принципиальная (формат А2).

Лист 3. Устройство умножения двоичных чисел. Перечень

элементов (формат А4).

6. Консультанты по проекту (с указанием разделов проекта)

7. Дата выдачи задания 01.02.2015 г.

8. Календарный график работы над проектом на весь период проектирования (с указанием сроков выполнения и трудоемкости отдельных этапов)

Неделя 1 – Введение. Раздел 1 – 10 %.

Неделя 2 – Раздел 2 – 20 %.

Неделя 3, 4 – Раздел 3 – 25 %.

Неделя 5, 6 – Раздел 4 – 25 %.

Неделя 7, 8 – Раздел 5. Заключение. Литература. Оформление

поясни тельной записки – 20 %.

Руководитель /В. И. Петров/

|

|

Подпись |

|

|

Задание принял к исполнению |

01.02.2015 г. |

/Н. В. Иванова/ |

||

(дата и подпись студента)

69

Б.2 Пример оформления задания к теме № 2

Учреждение образования «Белорусская государственная академия связи»

(наименование высшего учебного заведения)

Факультет электросвязи (или заочного образования)

«УТВЕРЖДАЮ» Зав. кафедрой ИКТ

«____» _______________2015 г.

ЗАДАНИЕ

по курсовому проектированию

|

Студенту |

3 курса гр.ТЭ112 И. Н. Иванову |

||

1. |

Тема проекта |

«Устройство суммирования двоичных чисел» |

||

по дисциплине «Цифровые и микропроцессорные устройства», |

||||

вариант № 2.1. |

|

|

|

|

2. |

Сроки сдачи студентом законченного проекта |

01.04.2015 г. |

||

3. |

Исходные данные к проекту |

Слагаемое |

||

A = D(16) = 1101(2). Слагаемое B = 7(16) = 0111(2). Коэффициент

пересчета счетчика Кпер = 15. Микросхемы схемотехники

КМОП серий 1594 и 5564.

4. Содержание расчетно-пояснительной записки (перечень подлежащих разработке вопросов) Введение.

1 Описание принципа работы заданной структурной электри-

ческой схемы устройства суммирования двоичных чисел.

2 Теоретическое обоснование и логическое проектирование

узлов устройства.

2.1Назначение и принцип построения четырехразрядных двоичных сумматоров с параллельным переносом.

2.2Разработка логической схемы счетчика с коэффициентом пересчета Кпер = 15.

2.3Разработка логической схемы четырехразрядного двоичного

сумматора с параллельным переносом в базисе И-НЕ.

70