Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Методические указания и задания к курсовому проекту (ЦиМПУ)

.pdf

которого может менятся в пределах от 0 до F в шестнадцатеричной СС.

Счетчик Y2 предназначен для параллельного ввода операнда B в двоичной СС, значение которого также может менятся от 0 до F.

Регистр Y4 предназначен для фиксации результата сравнения, который представляет собой трехразрядное слово.

Блок индикации Y5 предназначен для индикации результата сравнения с помощью светодиодных индикаторов.

Работа устройства синхронизируется тактовыми импульсами Uс. Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 4.2.

Рисунок 4.2 – Временная диаграмма, поясняющая процесс функционирования устройства сравнения

В момент времени t1 по отрицательному фронту тактового импульса (рисунок 4.2) начинается ввод операндов А и В в регистр Y1 и счетчик Y2 (рисунок 4.1). К моменту времени t2 ввод заканчивается, и начинается процесс сравнения в компараторе. Этот процесс в худшем случае завершается к моменту времени t3. Затем по положительному фронту тактового импульса результат сравнения фиксируется в регистре Y4 и одновременно поступает в блок индикации Y5. Например, при сравнении равных операндов A = B = 1101(2) на выходе FA = B компаратора Y3 вырабатывается единичный сигнал, а на выходах FA < B и FA > B вырабатываются нулевые сигналы1).

41

4.2 Задание на проектирование к теме № 4

Описать принцип построения и разработать в основном базисе логическую схему четырехразрядного компаратора двоичных чисел. Разработать логическую схему суммирующуего четырехразрядного счетчика с коэффициентом пересчета Кпер, заданным в таблице 4.1. Разработать принципиальную электрическую схему устройства сравнения по заданной структурной схеме (рисунок 4.1) на микросхемах схемотехники КМОП, серии которых указаны в таблице 4.1.

Таблица 4.1 – Исходные данные для проектирования устройства сравнения двоичных чисел

Номер |

Значение |

Значение |

Серии |

|

|

операнда А |

операнда B |

Кпер |

|||

варианта |

микросхем |

||||

(P = 16) |

(P = 16) |

|

|||

|

|

|

|||

4.1 |

D |

D |

1594, 5564 |

15 |

|

4.2 |

B |

6 |

1554, 1564 |

14 |

|

4.3 |

3 |

D |

1594, 5564 |

13 |

|

4.4 |

8 |

B |

1554, 1564 |

12 |

|

4.5 |

F |

4 |

1594, 5564 |

11 |

|

4.6 |

8 |

C |

1554, 1564 |

9 |

|

4.7 |

C |

C |

1594, 5564 |

15 |

Описать работу принципиальной электрической схемы устройства сравнения в течениие одного периода сигнала синхронизации Uс при сравнении заданных в таблице 4.1 операндов A и B.

____________________

1) В пояснительной записке приводить пример сравнения чисел А и В согласно заданному варианту

42

4.3 Назначение и принцип построения компараторов четырехразрядных двоичных чисел

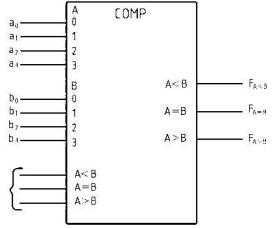

Компаратором (устройством сравнения) называется КЦУ, которое предназначено для сравнения двух двоичных чисел. УГО компаратора четырехразрядных двоичных чисел (рисунок 4.3) представляет собой прямоугольник с аббревиатурой COMP во внутреннем поле (от англ. Comparator) [6].

Рисунок 4.3 – Условное графическое обозначение четырехразрядного компаратора двоичных чисел

Компаратор имеет две группы входов. На одну из них поступают разряды числа А, на другую группу – разряды числа В.

Появление единичного сигнала на одном из трех выходов компаратора фиксирует результат сравнения. Эти соотношения используются как логические условия (признаки) в микропрограммах, в устройствах автоматического контроля и диагностики и т. д.

В таблице 4.2 показана связь между сигналами на выходах и

входах компаратора при сравнении одноразрядных чисел |

i и bi, |

которые могут быть равны единице или нулю. |

На |

|

43 |

соответствующем выходе появляется единичный сигнал, когда в должном соотношении находятся коды на входах. Например,

если ai = 1, bi = 1 |

(числа |

одинаковы), |

то |

функция, |

||

характеризующая |

равенство |

чисел, |

FA=B = 1, |

а |

функции, |

|

характеризующие |

их |

неравенство, |

FA<B = 0 |

и |

FA>B = 0. |

|

Аналогично заполняются другие строки таблицы.

Таблица 4.2 – Таблица истинности одноразрядного компаратора

Логические аргументы |

Логические функции |

|

|||

|

|

|

|

|

|

ai |

bi |

FA<B |

FA=B |

|

FA>B |

0 |

0 |

0 |

1 |

|

0 |

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

0 |

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

1 |

1 |

0 |

1 |

|

0 |

|

|

|

|

|

|

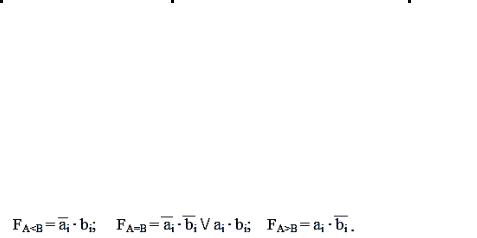

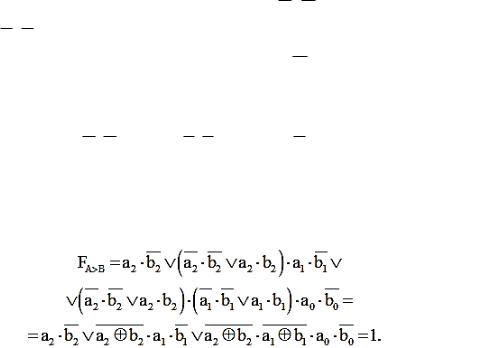

По данным таблицы 4.2 запишем логические функции для одноразрядного компаратора в СДНФ:

(4.1)

Если значения i и i таковы, что правые части функций принимают единичные значения, то соотношения, указанные в индексах левых частей, выполняются. Если правые части функций принимают нулевые значения, то соотношения между ai и i противоположны указанным.

Логическая схема одноразрядного компаратора, реализующая функции (4.1), приведена на рисунке 4.4.

44

a |

i |

b |

i |

1 |

a |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

i |

|

& |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

a |

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

a |

i |

b |

i |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

& |

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

b |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

i |

|

|

|

i

i

i

b

b

b

i |

F |

|

|

|

A<B |

i |

1 |

|

F |

|

A=B |

i |

F |

|

|

|

A>B |

Рисунок 4.4 – Логическая схема одноразрядного компаратора

Остановимся подробнее на равенстве чисел. Заметим, что функция FA=B функция «Равнозначность». По смыслу она противоположна функции FA≠B «Неравнозначность»:

̅̅̅ ̅̅̅ |

, т. е. ̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅ (4.2) |

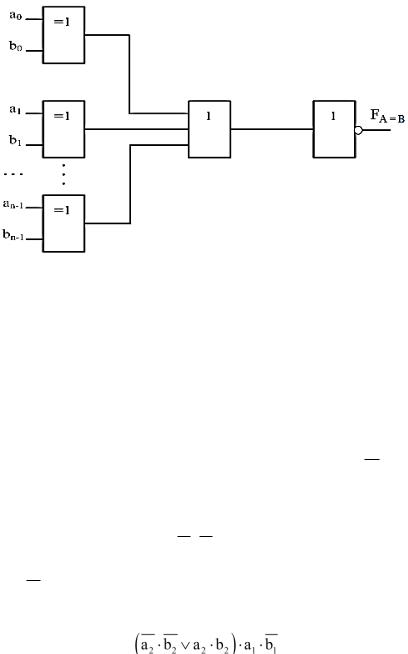

Поэтому проверку равенства одноименных разрядов двух чисел можно осуществить, используя логический элемент «Исключающее ИЛИ», дополненный инвертором (рисунок 4.5).

Когда цифры в одноименных разрядах чисел А и В одинаковы, то на выходах всех логических элементов «Исключающее ИЛИ» нулевые сигналы и функция FA=B = 1. Если хотя бы в одной паре разрядов находятся разные цифры, то на выходе соответствующего логического элемента «Исключающее ИЛИ» единичный сигнал и функция FA=B = 0, что указывает на неравенство чисел А и В.

45

Рисунок 4.5 – Логическая схема для проверки равенства двух многоразрядных двоичных чисел

Рассмотрим теперь неравенство чисел, используя выражение (4.1). Пусть А > В. Выявление такого неравенства начинается со старших разрядов; если они равны, то сравнивается следующая пара одноименных разрядов и т. д. Например, в случае трехразрядных чисел A и B могут быть следующие варианты:

– неравенство цифр в старших разрядах (a2 > b2), что в

соответствии с (4.1) представляется

При этом неравенство чисел А > выражением;

– равенство цифр в старших

выражением |

a |

2 |

b |

2 |

1 |

. |

|

|

|

В описывается тем же

разрядах (a2 = b2), что

представляется выражением |

a |

2 |

b |

|

|

в средних разрядах (a1 > b1),

2 |

a |

|

что

2

b |

2 |

1 |

и неравенство цифр |

|

|

описывается выражением

a |

1 |

b |

1 |

. При этом неравенство чисел А > В представляется |

|

1 |

|

конъюнкцией двух приведенных выражений

=1;

46

–равенство цифр в старших и средних разрядах

|

, |

|

что |

описывается выражениями |

|

a |

2 |

b |

2 |

a |

2 |

b |

2 |

1 |

и |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

a |

b a |

1 |

b |

1 |

, |

|

и неравенство цифр |

|

|

в |

|

младших |

разрядах |

||||||||||||||||||||||||

1 |

1 |

1 |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

(a0 > b0), что описывается выражением |

|

a |

0 |

b |

0 |

1 |

. При этом |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

неравенство |

чисел |

А > В |

|

представляется конъюнкциями |

трех |

||||||||||||||||||||||||||||||||

предыдущих выражений |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

a |

2 |

b |

2 |

a |

2 |

b |

2 |

|

|

|

a |

1 |

b a |

1 |

b |

|

a |

0 |

b |

0 |

1 |

. |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

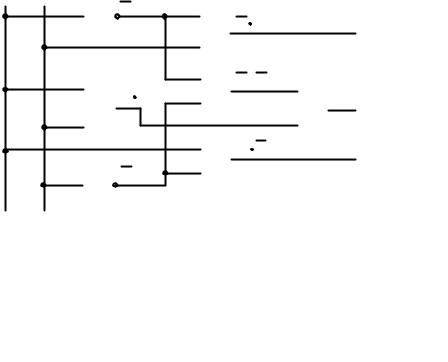

Поскольку возможен любой из трех вариантов, то выражение, учитывающее все варианты, запишется в виде дизъюнкций приведенных конъюнкций:

(4.3)

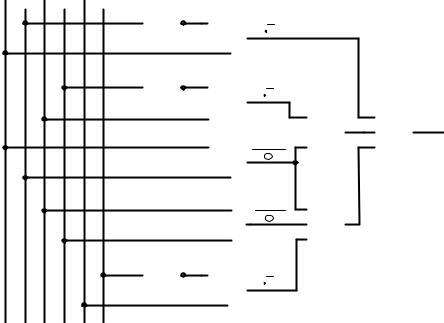

Если на выходе схемы (рисунок 4.6), элементы которой реализуют выражение (4.3), устанавливается единичный сигнал, то число А > B.

47

a2 |

b |

|

a1 |

b |

|

a0 |

b |

|

|

|

|

|

|

|

|

|

2 |

|

1 |

|

0 |

1 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

a |

2 |

b |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

a |

|

b |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A>B |

|

|

|

|

|

|

|

|

|

=1 |

a2 |

+ b2 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

=1 |

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

a1 + b1 |

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

a |

|

b |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

||

Рисунок 4.6 – Логическая схема для проверки неравенства двух трехразрядных двоичных чисел

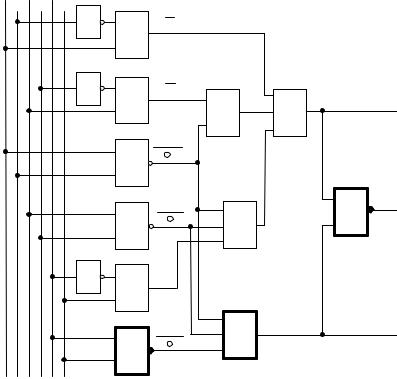

На рисунке 4.7 предыдущая схема дополнена логическим элементом «Исключающее ИЛИ–НЕ» (на входы которого подаются разряды a0, b0), конъюнктором (на выходе которого формируется функция FA=B) и элементом ИЛИ–НЕ (на выходе которого формируется функция FA<B). Если a2 = b2, a1 = b1,

a0 = b0, то FA=B = 1, т. е. число А = В. Если в результате сравнения чисел FA>B = 0 и FA=B = 0, то на выходе элемента

ИЛИ–НЕ единичный сигнал (FA<B = 1), т. е. число A < B.

48

а |

|

а |

1 |

|

|

а |

0 |

|

|

|

2 |

b |

|

b |

|

|

b |

|

|

||

|

2 |

|

1 |

|

|

0 |

1 |

|||

|

|

|

|

|

|

|

|

|

|

1

1

&a2•b2

&a1•b1

|

|

|

& |

1 |

|

|

|

|

F |

|

|

|

|

A>B |

=1 |

a2 |

+ b2 |

|

|

|

|

|||

|

|

|

|

1 |

=1 |

a1 |

& |

FA<B |

|

|

+ b1 |

|

||

&a0•b0

|

|

|

|

& |

|

=1 |

a |

+ |

b |

F |

A=B |

|

0 |

||||

|

0 |

|

|

Рисунок 4.7 – Логическая схема трехразрядного компаратора

По аналогичным схемам (см. рисунок 4.7) строятся компараторы для сравнения двоичных чисел с большей разрядностью.

4.4 Методические указания по разработке разделов проекта к теме № 4

Синтез заданного счетчика выполните по методике, приведенной в приложении А.

Логическую схему четырехразрядного компаратора двоичных чисел разработайте в основном базисе. Для этого на

49

основании логических функций (4.1)…(4.3) запишите логические функции для выходов четырехразрядного компаратора. Логическую схему компаратора (лист 1) вычертите

вформате А3 и выполните указания раздела 6.

Впринципиальной схеме компаратора на листе 2 допускается использование логических элементов «Исключающее ИЛИ».

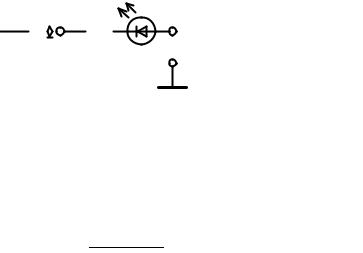

Для реализации блока индикации Y5 (рисунок 4.1) рекомендуется использовать светодиодные индикаторы, управляемые инвертором с открытым стоком (рисунок 4.8).

|

|

|

|

R |

HG1 |

|

|

|

|

|

|

U |

вх |

1 |

|

огр |

|

|

|

+ |

|||

|

|

|

|

||

|

1 |

|

0 |

|

|

|

|

|

U |

||

|

|

|

|

|

|

|

|

|

|

|

п |

|

|

|

|

|

|

Рисунок 4.8 – Фрагмент принципиальной схемы блока индикации

В разделе 3 следует также выбрать светодиоды для блока индикации и указать их основные электрические параметры в виде таблицы. Затем следует вычислить сопротивление резистора Rогр по формуле:

(4.4)

После чего выбрать номинальное значение резистора Rогр типа С2-33 из ряда Е12 (с допуском ±10%) и определить мощность рассеяния.

Принципиальную электрическую схему устройства cравнения (лист 2) разработайте в формате А2 на выбранных микросхемах на основе заданной структурной схемы (рисунок 4.1) и разработанной логической схемы компаратора (лист 1), а затем выполните указания раздела 6.

50