- •Архитектура микропроцессора

- •Итак, под «архитектурой» понимается совместимость с определённым набором команд, то есть, можно сказать, «архитектура процессора с точки зрения программиста». Есть и другая трактовка того же термина.

- •Различия между ядрами одной микроархитектуры

- •Ревизии

- •Лекция-практика-3

- •Многоуровневое кэширование

- •Размер кэшируемой области памяти.

- •Общие концепции работы кеша жесткого диска

- •2. Ускоренный обмен данными

- •3. Поддержка двух портов ata.

- •4. Возможность подключения приводов cd-rom и стриммеров.

Лекция-практика-3

Организация оперативной памяти

Элементная база

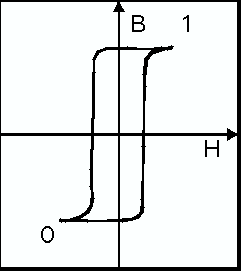

Чаще всего в качестве энергонезависимой памяти использовались ферритовые сердечники. Они представляют собой тор, изготовленных из специальных материалов — ферритов. Ферриты характеризуются тем, что петля гистерезиса зависимости их намагниченности от внешнего магнитного пол носит практически прямоугольный характер.

Вследствие этого намагниченность этого сердечника меняется скачками (положение двоичного 0 или 1, смотри рисунок B.1.) Поэтому, собрав схему, показанную на рисунке B.2, практически собран простейший элемент памяти емкостью в 1 бит. Память на ферритовых сердечниках работала медленно и неэффективно: ведь на перемагничивание сердечника требовалось время и затрачивалось много электрической энергии. Поэтому с улучшением надежности элементной базы ЭВМ энергонезависимая память стала вытесняться энергозависимой — более быстрой, экономной и дешевой. Тем не менее, ученые разных стран по-прежнему ведут работы по поиску быстрой энергозависимой памяти, которая могла бы работать в ЭВМ для критически важных приложений, прежде всего военных.

Рис.

B.1. Диаграмма намагниченности

ферритов.

В отличие от памяти на ферритовых сердечниках полупроводниковая память энергозависимая. Это значит, что

при выключении питания ее содержимое теряется.

Преимуществами же полупроводниковой памяти перед ее заменителями являются:

малая рассеиваемая мощность;

высокое быстродействие;

компактность.

Эти преимущества намного перекрывают недостатки полупроводниковой памяти, что делают ее незаменимой в ОЗУ современных компьютеров.

Сама же память, основанная на триггерах, называется статической (SRAM).

Статическое ОЗУ —дорогой и неэкономичный вид ОЗУ. Поэтому его используют в основном для кэш-памяти, регистрах микропроцессорах и системах управления RDRAM

Для того, чтобы удешевить оперативную память, в 90-х годах XX века вместо дорогого статического ОЗУ на триггерах стали использовать динамическое ОЗУ (DRAM). Принцип устройства DRAM следующий: система металл-диэлектрик-полупроводник способна работать как конденсатор. Как известно, конденсатор способен некоторое время “держать” на себе электрический заряд. Обозначив “заряженное” состояние как 1 и “незаряженное” как 0, мы получим ячейку памяти емкостью 1 бит. Поскольку заряд на конденсаторе рассеивается через некоторый промежуток времени (который зависит от качества материала и технологии его изготовления), то его необходимо периодически “подзаряжать” (регенерировать), считывая и вновь записывая в него данные. Из-за этого и возникло понятие “динамическая” для этого вида памяти.

За 10 лет, прошедших со времени создания первых микросхем DRAM, их развитие шло “семимильными" шагами по сравнению с SRAM. Эволюция DRAM рассматривается в следующем подразделе.

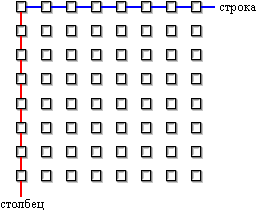

Каждая ячейка способна хранить только один бит. Если конденсатор ячейки заряжен, то это означает, что бит включен, если разряжен – выключен. Если необходимо запомнить один байт данных, то понадобится 8 ячеек (1 байт = 8 битам). Ячейки расположены в матрицах и каждая из них имеет свой адрес, состоящий из номера строки и номера столбца.

Теперь рассмотрим, как происходит чтение. Сначала на все входы подается сигнал RAS (Row Address Strobe, срабатывает по спаду импульса) – это адрес строки. После этого, все данные из этой строки записываются в буфер. Затем на регистр подается сигнал CAS (Column Address Strobe, срабатывает по спаду импульса) – это сигнал столбца и происходит выбор бита с соответствующим адресом. Этот бит и подается на выход. Но во время считывания данные в ячейках считанной строки разрушаются и их необходимо перезаписать взяв из буфера.

Теперь запись. Подается сигнал WR (Write) и информация поступает на шину столбца не из регистра, а с информационного входа памяти через коммутатор, определенный адресом столбца. Таким образом, прохождение данных при записи определяется комбинацией сигналов адреса столбца и строки и разрешения записи данных в память. При записи данные из регистра строки на выход не поступают.

Следует учесть то, что матрицы с ячейками расположены вот таким вот образом:

Это означает, что за один раз будет считан не один бит, а несколько. Если параллельно расположено 8 матриц, то сразу считан будет один байт. Это называется разрядностью. Количество линий, по которым будут передаваться данные от (или на) параллельных матриц, определяется разрядностью шины ввода/вывода микросхемы. Говоря о работе DRAM необходимо учитывать один момент. Фишка заключается в том, что конденсаторы не могут бесконечно долго хранить заряд и он в конце концов «стекает». Поэтому конденсаторы необходимо перезаряжать. Операция перезарядки называется Refresh или регенерацией. Происходит эта операция примерно каждые 2 мс и порой занимает до 10 % (а то и больше) рабочего времени процессора.

Важнейшей характеристикой DRAM является быстродействие, а проще говоря, продолжительность цикла + время задержки + время доступа, где продолжительность цикла – время, затраченное на передачу данных, время задержки – начальная установка адреса строки и столбца, а время доступа – время поиска самой ячейки. Измеряется эта фигня в наносекундах (одна миллиардная доля секунды). Современные микросхемы памяти имеют быстродействие ниже 10 мс.

Быстродействие оперативной памяти определяется временем выполнения операций чтения-записи. Существенными являются следующие характеристики:

Время доступа(access time) – задержка появления на выходе памяти данных относительно начала цикла чтения.

Длительность цикла определяется как минимальный период следования друг тза другом обращений к памяти( циклы чтения и записи могут требовать различного времени) В цикл обращения кроме доступа входит и фаза восстановления( возврата к исходному состоянию), соизмеримая по времени с активной.

Производительность памяти – скорость потока записываемых или считываемых данных(Мб/с)

Разрядность шины памяти – количество байт, с которыми операция чтения.записи может быть выполнена одновременно.

Банк памяти – комплект модулей памяти, обеспечивающих требуемую разрядность хранимых данных( напр, пара SIMM или один DIMM)

Можно выделить 2 способа организации ОП, имеющей целью снизить циклы ожидания, связанные с регенерацией информации: страничную организацию и «интерливинг»

Страничный метод базируется на том, что повторения сигнала RAS можно избежать, если последовательно выбираемые ячейки памяти лежат в пределах одной страницы. Считывание идёт в статический буфер для строки целиком, конкретный бит выбирается адресом столбца.(FPM DRAM так и работал)

Использование интерливинга подразумевает использование нескольких банков памяти. Идея заключается в том, что смежные блоки данных располагаются в разных банках. При последовательном обращении активная фаза обращения к одному банку выполняется во время регенерации другого банка, и простоя, обусловленного регенерацией, не будет. Чем больше банков – тем выше производительность.

Пакетная организация считывания данных.

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

4) закрыть строку с помощью команды подзарядки строки PRECHARGE (как вариант, это делается автоматически, если на втором шаге использовать команду «RD+AP»).

Виды оперативной памяти

FPM DRAM Строка – страница памяти. Адрес строки выставляется только один раз, и сигнал RAS удерживается для всех последующих обращений по записи или чтению. Способность работать таким образом – заслуга контроллера памяти , расположенного либо в МП либо в северном мосту чипсета

EDO – добавлен набор регистров – защёлок, которые удерживают информацию до сл запроса( для выходных данных) ТО есть считывание может проводиться внешними схемами до следующего импульса CAS.Что позволяет сократить длину импульса.

BEDO – дополнетельно внутренний счётчик адреса колонок Это позволяет выставлять адрес колонки только в начале, а в следующие разы выдаются только очереждные данные.

SDRAM – работает без тактов ожидания внутри пакетного цикла работает на частоте системной шины. От асинхронной памяти, где все процессы инициируются только сигналами RAS и CAS, отличие – наличие постоянно присутствующего сигнала тактовой частоты шины. Микросхемы такой памяти – это программируемые устройства со своим набором команд и внутренней организацией чередования банков. Перспективно – помешение КЭШа прямо на кристалл такой памяти.

Лекция

КЭШ

Cache (запас) - обозначает быстродействующую буферную память между процессором и основной памятью. Кэш служит для частичной компенсации разницы в скорости процессора и основной памяти - туда попадают наиболее часто используемые данные.

Это быстрое запоминающее устройство небольшого объема на основе SRAM, которое применяется при обмене данными между процессором и оперативной памятью, более медленной по сравнению с ЦП.

Контроллер кэш-памяти, анализируя выполняемые программы, заносит часто используемые данные в кэш. При чтении этих данных из кэш-памяти получается ощутимый выигрыш в производительности, т.к. время доступа к кэшу ниже, чем к ОЗУ.