2.Принципиальная схема.

На основе функциональной схемы была составлена принципиальная схема (Приложение 1). Для её разработки были использованы следующие микросхемы: КР1821ВМ85А, 1533ИР22, КР580ВА86, КР573РФ2, КР537РУ10, КР580ВВ55А, 1533ИД7.

КР1821ВМ85А

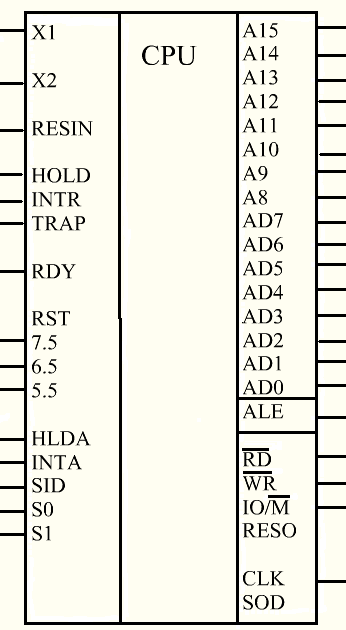

Восьмиразрядный микропроцессор Intel 8085 заключён в корпус типа DIP (с двусторонней упаковкой выводов). Расположение выводов приведено на рисунке 3, а в таблице 1 приведено название выводов и их назначение.

Рисунок 3. КР1821ВМ85А

Таблица 1 – название выводов микропроцессора

Выводы |

Описание |

Тип |

AD0-AD7 |

Шина адреса/данных |

Двунаправленная, три состояния |

A8-A15 |

Шина адреса |

Выход, три состояния |

ALE |

Разрешение захвата адреса |

Выход |

|

Управление считыванием |

Выход, три состояния |

|

Управление записью |

Выход, три состояния |

IO/ |

Указатель ВВ или памяти |

Выход, три состояния |

S0, S1 |

Указатель состояния шины |

Выход |

RDY |

Вызов состояния ожидания |

Вход |

SID |

Ввод последовательных данных |

Вход |

SOD |

Вывод последовательных данных |

Выход |

HOLD |

Требование захвата |

Вход |

HLDA |

Подтверждение состояния захвата |

Выход |

INTR |

Запрос прерывания |

Вход |

TRAP |

Запрос немаскированного прерывания |

Вход |

RST 5.5 RST 6.5 RST 7.5 |

Запрос аппаратного векторного прерывания |

Вход |

INTA |

Подтверждение запроса на прерывание |

Выход |

RESIN |

Сброс системы |

Выход |

X1, X2 |

Соединения кристалла или внешнего ГТИ |

Вход |

CLK |

Сигнал внутреннего ГТИ |

Выход |

Intel 8085 имеет 16 адресных линий. Восемь старших разрядов выведены на выводы A8-A15. Как и в случае типового микропроцессора подсоединение к шинам прямое. Микропроцессор снабжён внутренним генератором тактовых импульсов, входы которого X1 и X2 обычно соединены с кристаллом.

Микропроцессор снабжён специальным сигналом для того, чтобы информировать периферийные устройства, производит ли мультиплексированная шина операции на адресной шине или на шине данных. Это специальный сигнал, называемый сигналом разрешения захвата адреса (ALE).

Многие выводы МП Intel 8085, показанные на рисунке 1, выполняют функции управления :

и – используются для информации устройства памяти или УВВ,

т. Е. определяют, наступило ли время послать или принять данные по шине данных (в этом случае по мультиплексированной шине).

RESIN– вход сброса. Шины адреса, данных и линии управления находятся в состоянии высокого сопротивления в ходе сброса.

CLK – выход генератора тактовых импульсов Intel 8085.

INTR – вход запроса прерывания в Intel 8085 является универсальным прерыванием. Кроме входа нормального запроса на прерывание (INTR) микропроцессор Intel 8085 снабжён четырьмя другими входами прерывания:

TRAP, RST7.5, RST6.5, RST5.5.

Сигнал TRAP или один из трёх сигналов RST влекут за собой ветвление микропроцессора по вызываемому специальному адресу. Команды рестартов RST могут быть разрешены или запрещены программно, но прерывания по входу TRAP таким образом запрещены быть не могут. Запрос на прерывание INTR вызывает переход к новому адресу, указанному специальной командой, выданной периферией, когда активизируется выход, подтверждающий получение запроса на прерывание (INTR).

SID и SOD – это слаборазвитые ввод и вывод последовательных данных, соответственно. Отдельный бит данных на выводах SID загружается в наиболее значимый разряд (бит 7) аккумулятора командой RIM в Intel 8085. Вывод выхода SOD активизируется или сбрасывается командой SIM в МП.

RDY – это вход, который информирует микропроцессор, что периферия готова выдать или принять данные. Если RDY имеет L- уровень в цикле считывания или записи, микропроцессор его интерпретирует, как требование перейти в состояние ожидания. В этих условиях МП будет ждать до тех пор, пока периферия не просигнализирует, что она готова передать или получить данные. Затем будем продолжать выполнение цикла записи или считывания. Вход RDY удобен при использовании очень медленных по сравнению со скоростью обработки данных в микропроцессоре устройств памяти или периферии.

HOLD – входной сигнал требования захвата – оповещает микропроцессор, что другое устройство хочет использовать шины адреса и данных. По получении сигнала HOLD МП завершает текущую операцию. , и IO/ переводятся в третье состояние, то есть исключается взаимодействие с передачами данных на шинах.

HLDA – выход подтверждение состояния захвата. Он указывает периферии,

что запрос HOLD был получен, и микропроцессор не будет управлять шинами в следующем цикле тактовых импульсов.

IO/ , S0 и S1 – выходы, являющиеся сигналами управления, которые информируют периферию о типе машинного цикла, выполняемого МП (Таблица 2).

Таблица 2

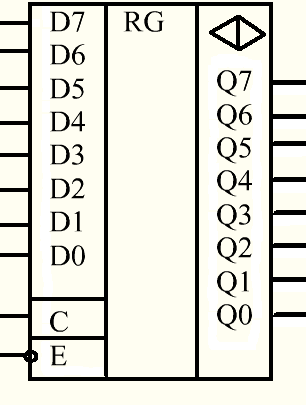

1533ИР22

Микросхема 1533ИР22 – восьмиразрядный регистр хранения информации, тактируемый импульсом, с возможностью перевода выходов в высокоимпедансное состояние. Условно графическое изображение микросхемы приведено на рисунке 4.

Рисунок 4. 1533ИР22

Запись информации в триггеры регистра происходит при подаче логической 1 на вход С, в этом случае сигналы на выходах регистра повторяют входные, регистр «прозрачен» для сигналов на входах D1 – D8. При подаче логического 0 на вход С регистр переходит в режим хранения информации.

Выходы микросхемы находятся в активном состоянии, если на вход ЕО подан логический 0. Если же на вход ЕО подать логическую 1,выходы регистра переходят в высокоимпедансное состояние. Сигнал на входе ЕО не влияет на запись в триггеры, запись может производиться как при логическом 0, так и при логической 1 на этом входе.

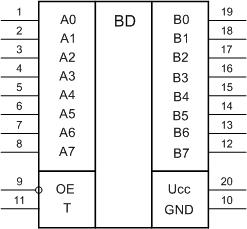

КР580ВА86

Микросхема КР580ВА86 – двунаправленный 8-разрядный шинный формирователь, предназначенный для обмена данными между микропроцессором и системной шиной; обладает повышенной нагрузочной способностью.

Рисунок 5. КР580ВА86

Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления. При помощи схемы управления производиться разрешение передачи (управление 3-м состоянием выхода) и выбор направления передачи данных.

В зависимости от состояния управляющих сигналов ОЕ и Т микросхемы могут работать в режиме передачи данных А->B, B; B, B ->A или в режиме выключено:

при ОЕ = 0, Т = 1 – направление передачи А->B, B;

при ОЕ = 0, Т = 0 – направление передачи B, B ->A;

при ОЕ = 0, Т = Х – на выходе А, В, В – 3-е состояние, где Х – безразличное состояние.

Назначение выводов представлено в таблице 3.

Таблица 3.

Вывод |

Обозначение |

Выводы |

Функциональное назначение выводов |

1-8 |

A0-A7 |

Вход/выход |

Информационная шина |

9 |

OE |

Вход |

Разрешение передачи (управление 3-м состоянием) |

10 |

GND |

- |

Общий |

11 |

T |

Вход |

Выбор направления передачи |

12-19 |

B7-B0 |

Выход/вход |

Информационная шина |

20 |

Ucc |

- |

Напряжение питания +5В |

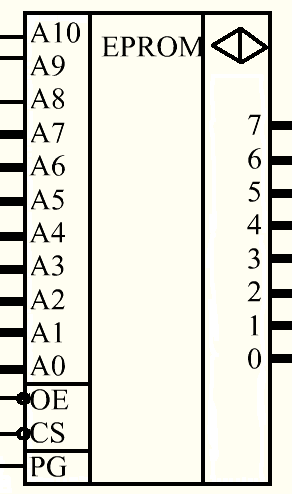

КР573РФ2

Микросхемы КР573 РФ2 является перепрограммируемым постоянным запоминающим устройством со стиранием информации ультрафиолетовым излучением емкостью 2048 байт. Условно графическое изображение микросхемы приведено на рисунке 6.

Рисунок 6. КР573 РФ2

Данные из запоминающей ячейки, адрес которой присутствует на адресных входах в течение всего цикла, считываются при подаче сигналов нулевого уровня на вход выбора кристалла CS и вход разрешения выхода CEO.

КР537РУ10

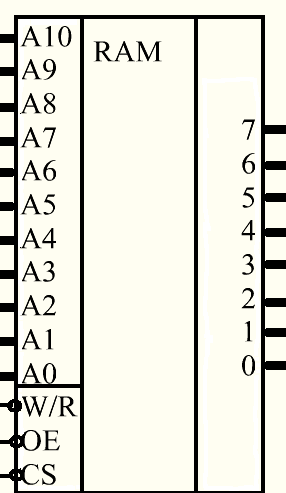

Микросхема КР537РУ10 представляет собой оперативное запоминающее устройство статического типа, изготовленное по КМОП технологии. Условно графическое изображение микросхемы приведено на рисунке 7.

Рисунок 7. КР537РУ10

Информационная емкость микросхемы 2048×8 бит. На адресные входы подается код полного адреса требуемой запоминающей ячейки (а не отдельные адреса строки и столбца как в предыдущем случае) и удерживается на протяжении всего цикла. Вход CS является входом выбора кристалла. Микросхема осуществляет цикл записи или чтения только при нулевом уровне сигнала на этом входе. Вход OE является входом разрешения выхода. При подаче на этот вход сигнала нулевого уровня выходы данных микросхемы выходят из высокоимпедансного состояния и на них появляются данные из запоминающей ячейки, адрес которой в данный момент присутствует на адресных входах. Запись данных в микросхему осуществляется по положительному перепаду сигнала на входе WR/RD при единичном уровне сигнала на входе OE и нулевом – на входе CS.