- •1. Формулировка задания

- •2. Схема 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.1. Общие сведения по работе 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.2. Описание работы мультиплексора 4→1

- •2.3. Описание работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.4. Проверка работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами в сапр xilinx ise 8.2i

- •3. Схема 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок intel) и обратно, с сигналом загрузки данных

- •3.1. Описание схемы 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных

- •3.2. Проверка работы схемы 32-рязрядного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных в сапр xilinx ise 8.2i

3.2. Проверка работы схемы 32-рязрядного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных в сапр xilinx ise 8.2i

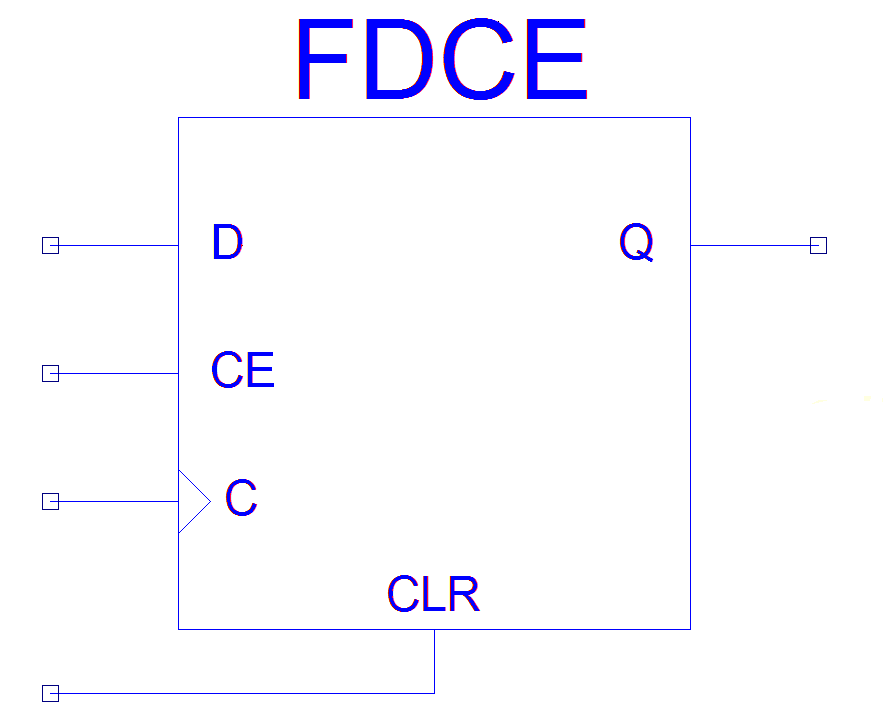

При конструировании данной схемы будем использовать вместо синхронных D–триггеров более сложные FDCE триггеры с разрешающим входом (рис.3.2).

Рис.3.2 FDCE триггер

FDCE триггер входит в стандартный набор компонентов САПР XILINX и имеет четыре входа: D – информационный, CE – разрешающий, C – вход синхронизации и CLR – вход сброса; и один выход Q.

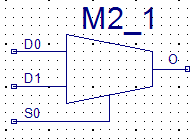

Также для построения схемы будем использовать мультиплексор 2→1 из стандартного набора компонентов САПР XILINX (рис 3.3.). С тремя входами: D0, D1, S0 и одним выходом – O. D0 и D1 – информационные входы, S0 – управляющий вход.

Рис.3.3. Мультиплексор 2→1

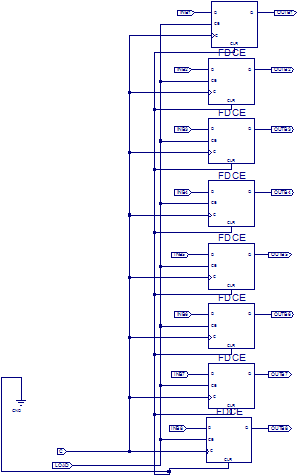

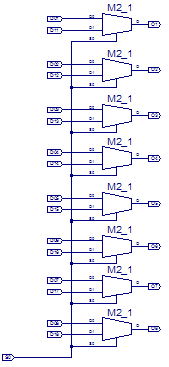

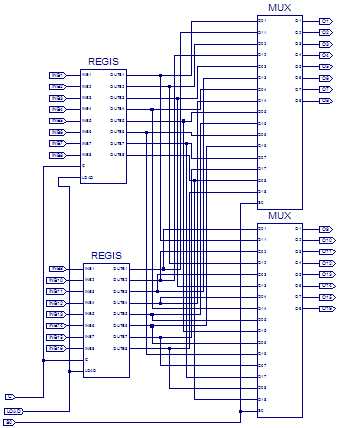

Построим 8-рязрядный регистр (рис 3.4.) и 16-рязрядный мультиплексор 2→1 (рис 3.5.) на базе элементов, представленных выше.

Рис.3.4. Схема 8-разрядного регистра на FDCE триггерах

Рис.3.5. Схема 16-разрядного мультиплексора 2→1

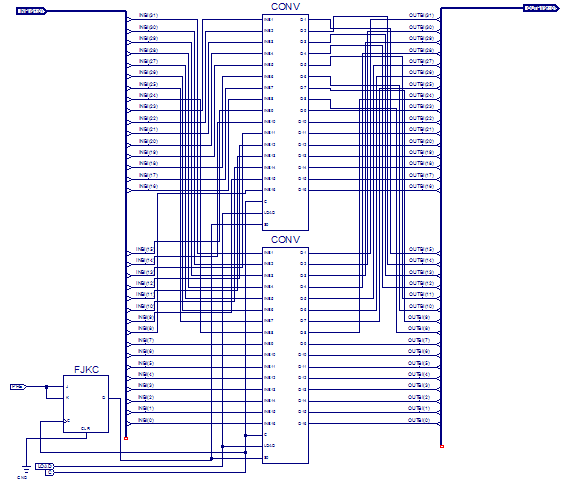

Из схем, представленных выше были получены библиотечные элементы 16-разрядного мультиплексора 2→1 и 8-разрядного регистра на FDCE триггерах. На их основе была построена схема элемента «CONV», представленная на рис. 3.6., который отвечает за преобразование двух байтов 32-разрядного слова.

Рис.3.6. Схема элемента «CONV»

Из схемы элемента «CONV» был получен библиотечный элемент, на основе которого была построена схема 32-разрядного синхронного преобразователя порядка следования байт в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных, представленная на рис. 3.7.

Рис.3.7. Схема 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных

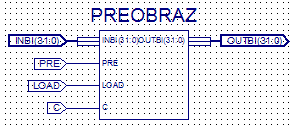

Из выше приведенной схемы был получен библиотечный элемент, на основе которого была построена схема, представленная на рис. 3.8.

Рис.3.8. Схема 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных

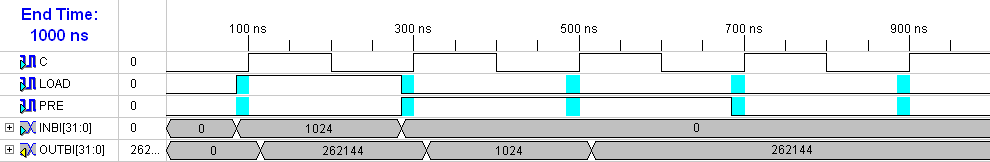

В результате моделирования работы устройства, представленного на рис.3.8. были получены временные диаграммы, показанные на рис.3.9.

Рис.3.9. Диаграммы работы 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных

ВыводЫ

В результате работы был смоделирован мультиплексор 4→1 и 4-х разрядный мультиплексор 4→1 с тристабильными выходами, построенный на его основе. Также были получены временные диаграммы работы данных устройств, соответствующие таблицам истинности рассматриваемых устройств.

Была смоделирована схема 32-рязрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно с сигналом загрузки данных. Были получены временные диаграммы, соответствующие теоретическому материалу.