- •4. Порядок выполнения работы

- •Включить лабораторную плату dsk 5510 и выполнить ее тестирование.

- •Ознакомиться с примером разработки простого приложения

- •Создать новый проект

- •Добавить файлы в проект

- •Ознакомиться с кодом файла источника.

- •Построить проект и запустить программу.

- •Научиться использовать точки пробника и окна просмотра переменных

- •Научиться добавлять точки пробника для чтения данных из файлов.

- •Научиться пользоваться средствами визуализации и анимации

- •3. Методические указания

- •3.1. Цифровой сигнальный процессор tms320c55xx

- •3.2. Средства разработки и отладки программ

- •Контрольные вопросы

- •Приложение 1 Файл источника

- •Приложение 2

- •Структурная схема отладочной платы

Научиться пользоваться средствами визуализации и анимации

Выберете ViewGraphTime/Frequency.

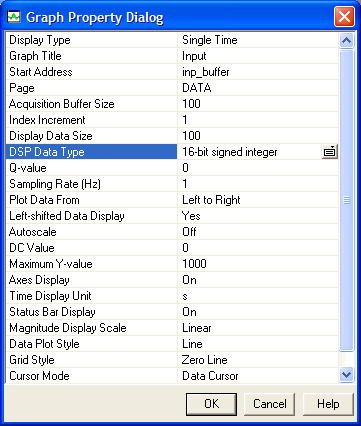

В диалоговом окне Graph Property Dialog измените Graph Title, Start Address, Acquisition Buffer Size, Display Data Size, DSP Data Type, Autoscale, and Maximum Y-на значения, показанные на картинке.

Нажмите OK. Появится окно просмотра графиков.

С помощью нажатия на правую кнопку мыши, щелкнув по окну просмотра графика, выберете Clear Display из всплывающего меню.

Выбрать ViewGraphTime/Frequency снова.

Измените Graph Title на Output и Start Address на out_buffer. Все остальные установки оставьте те же.

Нажмите OK Появится окно просмотра графиков. С помощью нажатия на правую кнопку мыши, щелкнув по окну появившегося графика, выберете Clear Display из всплывающего меню.

В окне volume.c поставьте курсор напротиы линии dataIO.

Нажать (Toggle Breakpoint)или F9. Рядом с голубым кружком появится красный точка останова.

Расставьте окна так, чтобы были видны оба графика.

Нажать на панели инструментов

(Animate) или нажмите F12

для запуска программы.

(Animate) или нажмите F12

для запуска программы.

The Animate command is similar to the Run command. It causes the target application to run until it reaches a breakpoint. The target is then halted and the windows are updated. However, unlike the Run command, the Animate command then resumes execution until it reaches another breakpoint. This process continues until the target is manually halted. Think of the Animate command as a run-break-continue process.

Нажмите DebugHalt для остановки программы. Поэксперементируйте с установками в Graph Property Dialog

3. Методические указания

3.1. Цифровой сигнальный процессор tms320c55xx

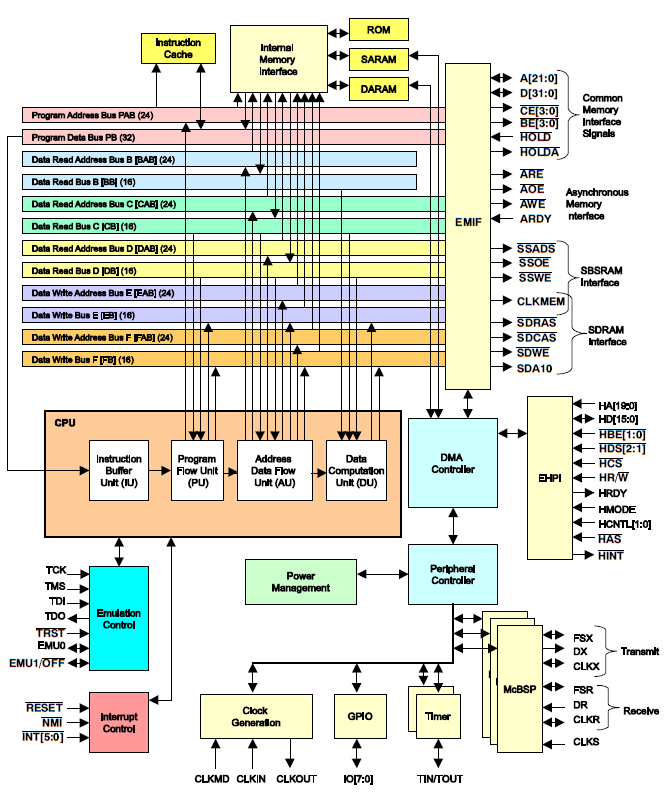

Цифровые сигнальные процессоры (ЦСП) с фиксированной точкой TMS320VC5510/5510A основаны на ядре TMS320C55xx. Данная архитектура обладает высокой производительностью (благодаря повышению параллелизма) при низком энергопотреблении.

Набор периферийных устройств процессоров 5510/5510A включает в себя интерфейс внешней памяти (EMIF), обеспечивающий непосредственное подключение различных типов асинхронной памяти, таких, как EPROM и SRAM, а также высокоскоростных запоминающих устройств высокой плотности, таких, как синхронные DRAM и SRAM с пакетной выборкой. Три полнодуплексных многоканальных буферизованных последовательных порта (McBSP) обеспечивают непосредственное подключение большого ряда устройств со стандартными последовательными интерфейсами и многоканальный обмен (до 128 каналов). Порт управляющего контроллера (EHPI) представляет собой 16-битный параллельный интерфейс, обеспечивающий внешнему управляющему процессору доступ к встроенной памяти процессоров 5510/5510A. Порт EHPI может быть сконфигурирован как в мультиплексный, так и в немультиплексный режим, что позволяет использовать его совместно с самыми различными управляющими процессорами. Контроллер прямого доступа к памяти (DMA) обеспечивает перемещение данных по шести независимым каналам без вмешательства ядра, его суммарная пропускная способность составляет до двух 16-битных слов за цикл. Кроме этого, набор периферийных устройств включает в себя 2 таймера общего назначения, восемь выводов общего назначения (GPIO) и генератор с ФАПЧ и цифровым управлением (DPLL).

Рис1. Структурная схема ЦСП 320C55xx.

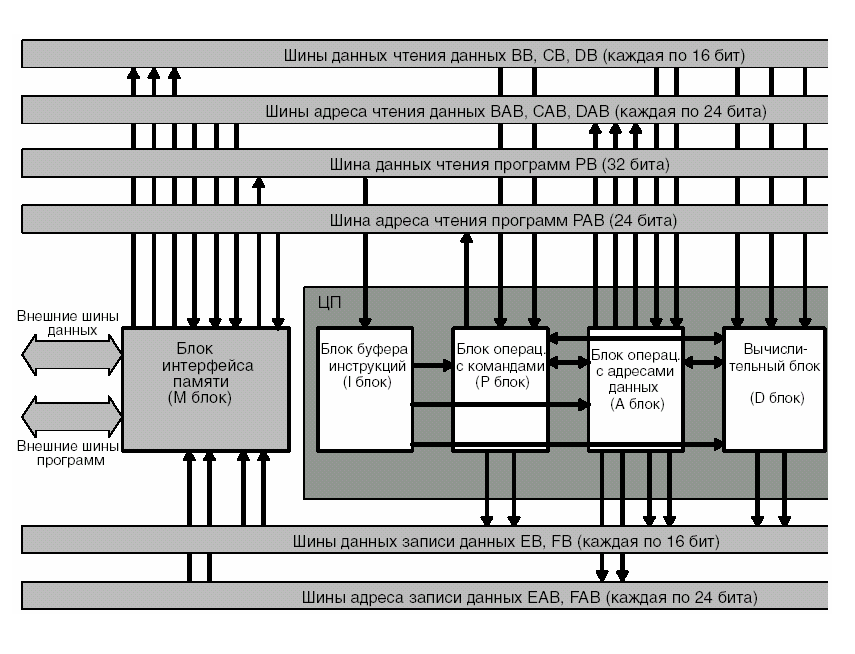

Ядро процессора (рис.2) обладает внутренней шинной структурой, состоящей из программной шины, трёх шин чтения данных, двух шин записи данных и вспомогательных шин для периферии и контроллера прямого доступа к памяти (DMA), что позволяет выполнять вплоть до трёх операций чтения данных и двух операций записи данных за один цикл. Параллельно этому, контроллер DMA может осуществить до двух операций перемещения данных без задействования ядра.

Рис.2. Структурная схема ядра ЦСП TMS320C55x.

Шины данных чтения данных (BB, CB, DB). Данные три шины предназначены для пересылки 16-ти разрядных данных из пространства данных или пространства I/O (ввода/вывода) к функциональным блокам ядра. Шина BB переносит данные из внутренней памяти в блок D (главным образом в двойной блок умножителя-накопителя (MAC)). Эта шина не соединена с внешней памятью. Инструкции, которые осуществляют считывание трех операндов одновременно, используют шины BB, CB и DB. Шины CB и DB передают данные в блок P, блок A и блок D. Инструкции, которые считывают два операнда одновременно, используют шины CB и DB. Инструкции, которые производят одиночное считывание, используют шину DB.

Шины адреса чтения данных (BAB, CAB, DAB). Эти три шины пересылают 24-битные адреса в блок интерфейса памяти, который, затем, передает запрашиваемые значения в шину данных чтения данных. Все адреса пространства данных генерируются в блоке A. Шина BAB передает адреса для данных, которые пересылаются из внутренней памяти в ядро через шину BB. Шина CAB содержит адреса для данных, которые передаются к ядру посредством шины CB. Шина DAB передает адреса для данных, которые пересылаются к ядру либо только по шине DB, либо по шинам CB и DB одновременно.

Шина данных чтения программ (PB). Шина PB пересылает 32-битный (4 байта) адрес программного кода к блоку I, где инструкции декодируются.

Шина адреса чтения программ (PAB). Шина PAB пересылает 24-битный адрес программного кода, который передается в ядро через шину PB.

Шины данных записи данных (EB, FB). Эти две шины передают 16-битные данные из функциональных блоков ядра к пространству данных или пространству ввода/вывода. Шины EB и FB принимают данные из блока P, блока A и блока D. Инструкции, которые записывают два 16 - разрядных значения в память одновременно, используют шины EB и FB. Инструкции, производящие одиночную запись, используют шину EB.

Шины адреса записи данных (EAB, FAB). Данные две шины пересылают 24-битные адреса к блоку интерфейса памяти, который затем принимает значения, поступившие от шин данных записи данных. Все адреса пространства данных генерируются в блоке A. Шина EAB передает адреса для данных, которые перемесылаются в память посредством либо только шины EB, либо шин EB и FB одновременно. Шина FAB передает адреса для данных, которые пересылаются в память через шину FB.

Ядро процессора TMS320C55xx состоит из четырех основных блоков: блок буфера инструкций (I блок), блок операций с адресами команд (P блок), блок операций с адресами данных (A блок), вычислительный блок (D блок). В состав ядра также входит блок интерфейса памяти (M блок).

Блок буфера инструкций (I блок). Семейством цифровых сигнальных процессоров C55x поддерживаются инструкции с переменным числом байт, что позволяет увеличить плотность кода. В течение каждого цикла блок I принимает 4 байта программного кода в свой буфер и далее декодирует один из шести байтов кода, которые были получены ранее. Затем блок I пересылает данные в блок P, блок A и блок D для исполнения инструкций. Например, любые константы, которые были закодированы в инструкциях (для загрузки регистров, обеспечивающих число сдвигов, определение битовых номеров и т.д.), извлекаются в блоке I и перемещаются в соответствующий блок. Модуль инструкций осуществляет выборку инструкций из внутренней либо внешней памяти и определяет очередь инструкций для блока операций с адресами команд (программного модуля).

Блок операций с адресами команд (P блок). Программный модуль (блок Р) декодирует инструкции, определяет задачи для адресного устройства и устройства данных и управляет защищённым конвейером. Для предотвращения переполнения конвейера при выполнении условных переходов используется предсказание переходов. Процессоры 5510/5510A также имеют встроенный кэш инструкций размером 24 KБайт для снижения числа операций доступа к внешней памяти, повышения производительности и снижения энергопотребления. Блок P генерирует все адреса пространства программ и пересылает их с помощью шины PAB. Он также контролирует последовательность выполнения инструкций с помощью таких операций, как аппаратное зацикливание, условный переход и условное исполнение.

Блок операций с адресами данных (A блок). Адресный блок (блок A) содержит всю необходимую логику и все регистры для генерации адресов пространства данных, которые передаются посредством шин BAB, CAB и DAB. Он также содержит 16-ти разрядное арифметическое логическое устройство (ALU), которое может осуществлять арифметические, логические, сдвиговые операции и операцию насыщения.

Вычислительный блок (D блок). Блок D содержит следующие вычислительные блоки:

40-битное многорегистровое устройство циклического сдвига, которое обеспечивает сдвиг в диапазоне от –32 до 31;

40-битное арифметическое логическое устройство (ALU), производящее арифметические, логические операции и операции округления и насыщения;

два блока умножителей-накопителей (MAC), осуществляющие 17- разрядное умножение и 40 - разрядное сложение или вычитание в одном цикле.

Сценарий совместного использования двух АЛУ (блока А и блока D) определяется набором инструкций, обеспечивая оптимальную параллельную работу и снижение энергопотребления.

Блок интерфейса памяти (M блок) служит связующим звеном для передачи всех данных между ядром и пространством данных или пространством ввода/вывода.