Последовательностные устройства

Особенностью последовательностных логических устройств является зависимость выходного сигнала не только от значения действующих в настоящий момент на входе логических переменных, но и от тех значений переменных, которые действовали на входе в предыдущие моменты времени, т.е. для последовательностного устройства существенное значение имеет предыстория состояния входных информационных переменных. Следовательно, в подобных элементах должна существовать ячейка памяти, хранящая значение переменных в предыдущие моменты времени. Данную функцию во всех цифровых схемах выполняют триггерные устройства или триггеры

Триггеры

Триггерами называют большой класс электронных устройств, обладающих способностью длительно находится в одном из двух (трех) устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко расшифровывается по значению выходного напряжения. По принципу работы триггеры относятся к импульсным элементам.

Слово «триггер» в переводе с английского означает спусковое устройство, курок. В технической литературе на английском языке термин «trigger» обычно применяют в значении глагола «запускать».

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера понимается способность оставаться в одном из двух устойчивых состояний и после прекращения действия переключающего сигнала. С учетом представления информации в виде нулей и единиц можно констатировать, что триггер помнит (хранит) один разряд числа, записанного в двоичном коде. Первые триггерные схемы на электронных лампах (катодные реле) были описаны в 1918 году М.А. Бонч-Бруевичем.

Классификация триггеров. По способу представления информации триггеры делятся на статические и динамические.

Динамические триггеры представляют систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определенной частоты, а другое – отсутствием выходных импульсов (нулевое). Смена состояний производится внешними импульсами управления. Динамические триггеры имеют ограниченное использование и в данном курсе не рассматриваются.

Статические триггеры характеризуются выходным состоянием с неизменным уровнем напряжения: высоким – близким к напряжению питания и низким – около нуля. Статические триггеры часто называют потенциальными.

Статические триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы – симметричные и несимметричные. Название определяется внутренней структурой устройства.

Симметричные триггеры имеют симметрию схемы двухкаскадного усилителя с положительной обратной связью, а также идентичность характеристик параметров симметричных элементов и связей между ними. В несимметричных триггерах симметрии плеч нет.

Основную массу триггерных устройств составляют симметричные триггеры.

Особенностью всех

триггеров является наличие двух выходов:

прямого

![]() и инверсного

и инверсного

![]() ,

связанных функциональным единством,

т.е. при наличии единицы на

-выходе

потенциал

будет нулевым и наоборот.

,

связанных функциональным единством,

т.е. при наличии единицы на

-выходе

потенциал

будет нулевым и наоборот.

По способу приема информации различают асинхронные и синхронные триггеры (см. рисунок 6.1).

Асинхронные триггеры изменяют свое состояние непосредственно в момент появления соответствующего входного информационного сигнала.

Синхронные триггеры изменяют свое состояние в строго определенные (тактовые) моменты времени, соответствующие действию активного сигнала на специализированном входе, который называется тактовый или синхронизирующий «С».

Рисунок 6.1 –

Классификация триггеров по способу

ввода информации

По способу управления синхронные триггеры подразделяются на статические, управляемые постоянным уровнем на входе синхронизации и динамические – их управление осуществляется перепадом напряжения (фронтом).

Входные управляющие сигналы могут быть прямыми и инверсными.

Кроме того, синхронизируемые триггеры делятся на однотактные и двухтактные. В однотактных триггерах информация передается на выход за один такт, в двухактных – за два. Однотактные триггеры в обозначении функции имеют «Т», двухтактные – «ТТ».

По функциональным особенностям триггеры подразделяют на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS – триггеры);

- универсальные (JK – триггеры);

- с памятью (D _триггеры);

- со счетным входом (Т – триггеры).

Входы управления триггерами обозначают:

R – вход установки в нулевое состояние;

S – вход установки в единичное состояние;

J – вход установки в состояние «1» в универсальном JK- триггере

K - вход установки в состояние «0» в универсальном триггере

Т – счетный (общий) вход;

D – информационный вход установки в состояние «1» или «0»;

V – дополнительный управляющий вход для разрешения приема информации (вход выборки);

С – вход синхронизации (тактовый вход).

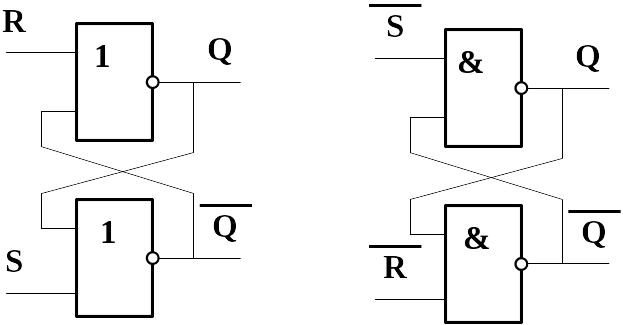

Асинхронный RS – триггер – простейшее устройство, представляющее собой бистабильную ячейку памяти. Относится к симметричным триггерам. Асинхронные RS - триггеры применяются в качестве самостоятельных устройств, а также входят в состав других, более сложных триггеров в качестве ячеек памяти. На рисунке 6.2 изображен простейший RS – триггер и его таблица истинности.

Рисунок 6.2 –

Асинхронный RS

– триггер и таблица истинности его

состояния

Согласно таблице в единичное состояние триггер переключается при единице на входе S, а в нулевое – при единице на входе R. Наличие единичных уровней на обоих информационных входах дает неопределенное состояние выхода и в эксплуатационных режима не предусматривается.

RS – триггер – устройство с раздельными входами управления, функцию которого можно легко реализовать двумя элементами «ИЛИ – НЕ» (прямое управление) или двумя элементами «И – НЕ» (инверсное управление) (см. рисунок 6.3).

а

б

а - прямое управление;

б – инверсное управление;

Рисунок 6.3 –

Асинхронный RS

– триггер и таблица истинности его

состояния

а - прямое управление;

б – инверсное управление;

Рисунок 7.3 –

Асинхронный RS

– триггер и таблица истинности его

состояния

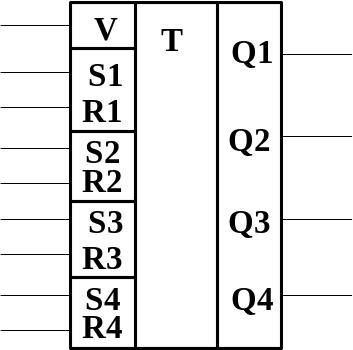

В интегральном исполнении практически все серии широкого применения включают в свой состав асинхронные RS – триггеры (например, 4 асинхронных триггера с прямым управлением имеет ИМС К564ТР2, см. рисунок 6.4).

Рисунок 6.4 –

Счетверенный асинхронный RS

– триггер К564ТР2 с входом выборки

Кроме информационных входов R и S данная ИМС снабжена общим вспомогательным входом выборки V, при наличии нуля на котором микросхема переходит в высокоимпедансное (третье) состояние.

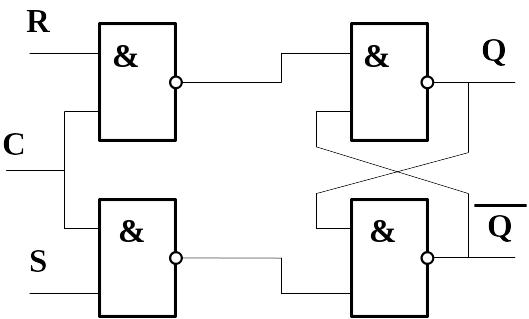

Синхронные (тактируемые) RS – триггеры получают из асинхронных путем подключения к его входам схем управления на базовых ЛЭ (см. рисунок 6.5).

Рисунок 6.5–

Тактируемый RS

– триггер со статическим управлением

Информационные сигналы по входам R и S воспринимаются триггером только при наличии единичного уровня на тактовом входе «С». Так работают синхронные триггеры со статическим управлением. Во время действия высокого уровня на входе «С» этот триггер функционирует как обычный асинхронный, поэтому смена информационных сигналов должна производится в момент паузы тактового импульса, иначе возникнут нарушения в работе устройства.

В динамических синхронных триггерах информация на входах R и S может обновляться и в период действия импульса синхронизации и в моменты паузы. Такой порядок работы стал возможен благодаря использованию в схемном решении вместо двух элементов совпадения на входе (см. рисунок 6.5) четырех RS – триггеров.

Работа триггера с динамическим управлением основана на эффекте переключения соответствующим фронтом импульса синхронизации. Например, триггер на рисунке 6.6 управляется отрицательным перепадом (из единицы в ноль) тактового импульса, а переключение по информационным R и S входам осуществляется единичными уровнями сигналов.

На принципиальных схемах триггеры с динамическим управлением обозначают с помощью стрелки-треугольника входа тактирования, при этом стрелка, обращенная внутрь триггера, говорит о прямом управлении (положительным фронтом импульса синхронизации), наружу – инверсное управление (см. рисунок 6.7).

Рисунок 6.6–

Синхронный RS

– триггер с динамическим инверсным

управлением

Рисунок 6.6–

Изображение синхронного RS

– триггера с динамическим инверсным

управлением на принципиальных схемах

Шестиэлементные триггерные системы широко используются для организации триггеров других типов, например D – триггеров, JK – триггеров, Т – триггеров.

JK – триггеры для всех входных комбинаций, кроме одной (Jn=1, Kn=1), функционируют подобно RS – триггеру, при этом вход «J» играет роль входа S, а «K» - входа R. Входная комбинация Jn = Kn = 1 приводит к опрокидыванию триггера и смене выходных сигналов на противоположные по приходу каждого тактового импульса.

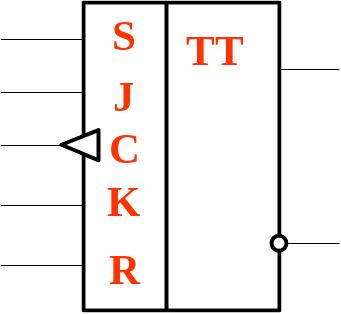

JK – триггеры выпускаются только тактируемыми (см. рисунок 6.7). Как правило, устойчивая работа данных триггеров обеспечивается их двухступенчатой структурой (по положительному фронту тактового импульса информация передается на выход первого триггера, по отрицательному – на выход второго).

Рисунок 6.7–

Изображение JK

– триггера с прямым динамическим

управлением на принципиальных схемах

(К561ТВ1)

Таблица истинности состояния JK – триггера приведена в таблице 6.1.

Таблица 6.1 Таблица состояния JK – триггера (К561ТВ1) для динамического управления по входам J и K

Асинхронная установка триггера в нулевое и единичное состояние осуществляется входам R и S независимо от состояния уровней на J и K входах.

D – триггеры в отличии от рассмотренных выше имеют для установки в состояние 0 и 1 один информационный вход D.

Применение находят D – триггеры в асинхронном и синхронном исполнении.

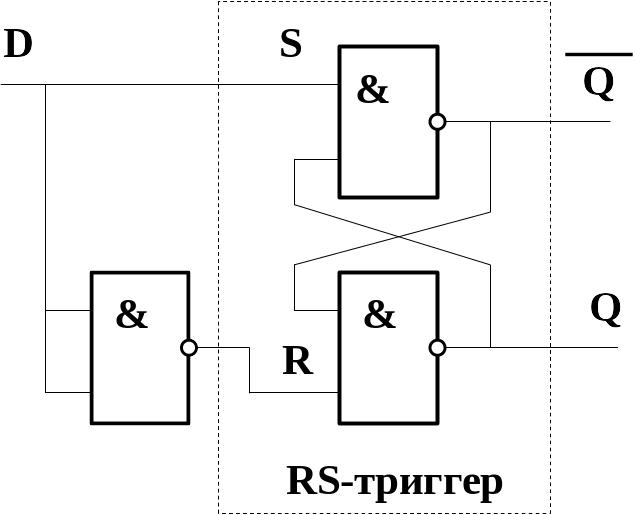

Асинхронные D – триггеры обеспечивают передачу сигнала с входа D на выход, не обладая при этом свойством памяти (см. рисунок 6.8).

Рисунок 6.8–

Структурная схема асинхронного D

- триггера

Подобные схемные решения используются для формирования импульсных сигналов с крутыми фронтами (см.рисунок 6.9).

Рисунок 6.9– Форма

сигналов на входе D

и выходе Q

формирователя

импульсов на

основе асинхронного D

- триггера

В практических целях асинхронные D – триггеры, как элементы памяти не используют и в этом ключе их относят к D – триггерам достаточно условно.

Хранения информации у D – триггеров обеспечивается за счет цепей синхронизации и, поэтому, все D – триггеры – тактируемые. Управление по входу синхронизации может быть статическим, динамическим и двухступенчатым. Для примера на рисунке 6.10 приведены ИМС реализующие функцию статического и динамического D – триггера.

а

б

а – статический

D

– триггер (К155ТМ7); б – динамический D

– триггер (К561ТМ2)

Рисунок 6.10 –

Синхронные D

- триггеры

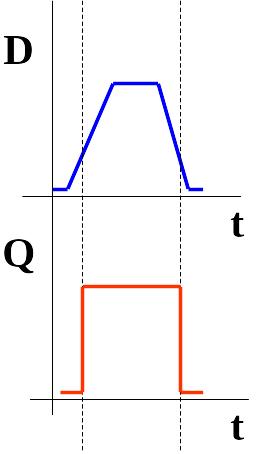

Т – триггеры – последовательностные устройства, изменяющие свое логическое состояние на противоположное по каждому активному сигналу на входе «Т».

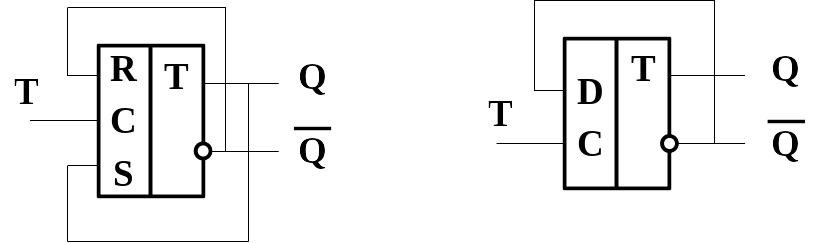

В сериях ИМС широкого применения Т – триггеры как таковые не используют, однако функционально Т – триггер находит применение как счетное устройство. Его легко получить из синхронного RS – триггера и D – триггера (см. рисунок 6.11).

Двухступенчатый Т – триггер строится на двух синхронных RS – триггерах (см. рисунок 6.12).

Т – триггер также легко получить из универсального JK – триггера. Для этого необходимо информационные входы J и K объединить вместе и использовать их, как вход разрешения, при этом счетные импульсы подаются на вход синхронизации «С», выполняющего в данном случае функцию счетного входа «Т» (см. таблицу 6.1).

а

б

а – Т – триггер

на базе синхронного RS

– триггера, б - Т – триггер на базе D

– триггера

Рисунок 6.11 –

Счетный Т - триггер

б

а

а – Т – триггер

на базе синхронного RS

– триггера, б – изображение двухступенчатого

Т – триггера на принципиальных схемах

Рисунок 6.12 –

Двухступенчатый счетный Т - триггер

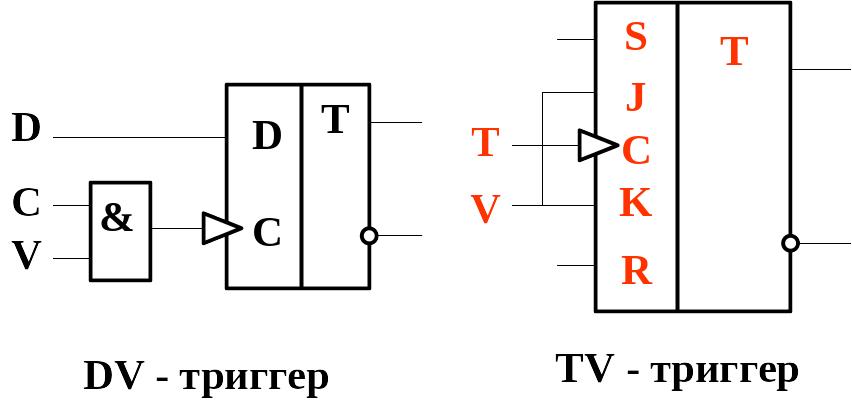

DV и TV – триггеры представляют собой модификацию соответственно D и T – триггеров. Дополнительный вход V используется как разрешающий – запрещающий. Наличие входа V расширяет функциональные возможности D и T - триггеров. На рисунке 6.13 приводятся функциональные схемы DV и TV – триггеров.

а

б

а – DV

– триггер на базе синхронного D

– триггера, б - TV

– триггер на базе JK

- триггера

Рисунок 6.13 – DV

и TV

– триггеры

Несимметричные триггеры Шмитта. Основу несимметричных триггеров, как и симметричных, составляет двухкаскадный усилитель, охваченный положительной обратной связью. Эти триггеры обладают двумя устойчивыми состояниями, смена которых происходит скачкообразно под действием входных сигналов. Для триггеров такого типа в отличии от симметричных характерны не идентичность обеих каскадов и видов связи между ними.

По функциональным характеристикам несимметричные триггеры ближе к импульсным устройствам, чем к цифровым.

Несимметричные триггеры входят в состав некоторых серий широкого применения, например К155ТЛ2 (шесть триггеров в одном корпусе), но чаще всего собираются из отдельных дискретных элементов.

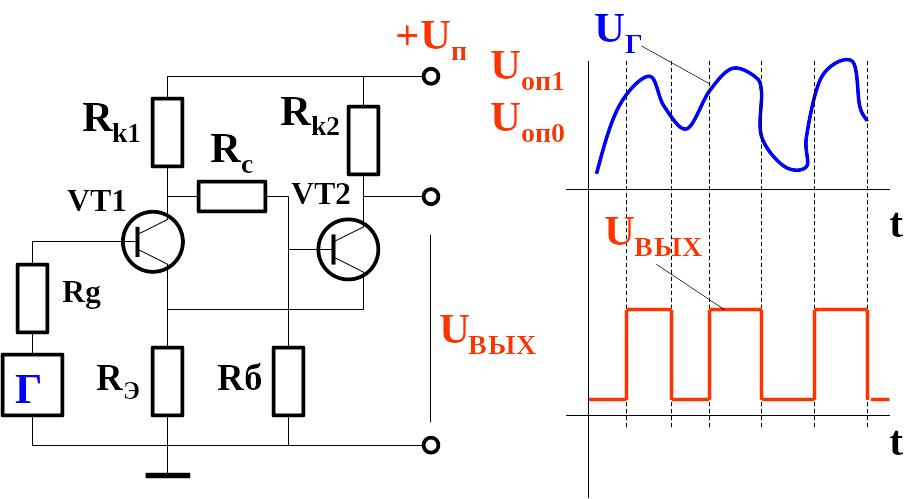

На рисунке 6.14 приведена базовая схема транзисторного несимметричного триггера с эмиттерной связью. Этот вид триггера был впервые описан в 1938 году О. Г. Шмиттом, отчего его второго название – триггер Шмитта.

Согласно приведенной схеме транзистор VT1 при малом входном сигнале находится в закрытом состоянии, а VT2 – в открытом (выходным уровнем коллекторного напряжения первого каскада). При открытии первого транзистора, за счет закрытия второго каскада и резистора RЭ , играющего роль элемента положительной обратной связи опрокидывание триггера происходить лавинообразно. В первоначальное состояние триггер возвращается обратным путем.

а

б

а – принципиальная

схема триггера Шмитта, б – временные

диаграммы работы триггера Шмита

Рисунок 6.14 –

Несимметричный триггер Шмитта

Счетчики импульсов

Счетчиком называется последовательностное устройство, предназначенное для счета входных импульсов и фиксации их числа в соответствующем коде. Основной параметр счетчика – модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком. В обозначении счетчика применяют буквы «СТ» (от англ. counter).

Счетчики классифицируют:

По модулю счета:

- двоично-десятичные;

- двоичные;

- с произвольным постоянным модулем счета;

- с переменным модулем счета.

По направлению счета:

- суммирующие;

- вычитающие;

- реверсивные.

По способу внутренних связей (тип структурной схемы):

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- кольцевые.

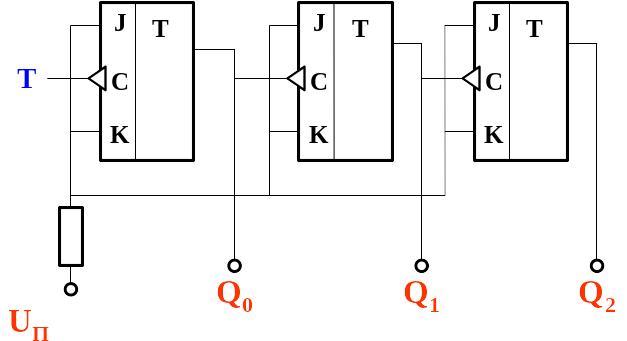

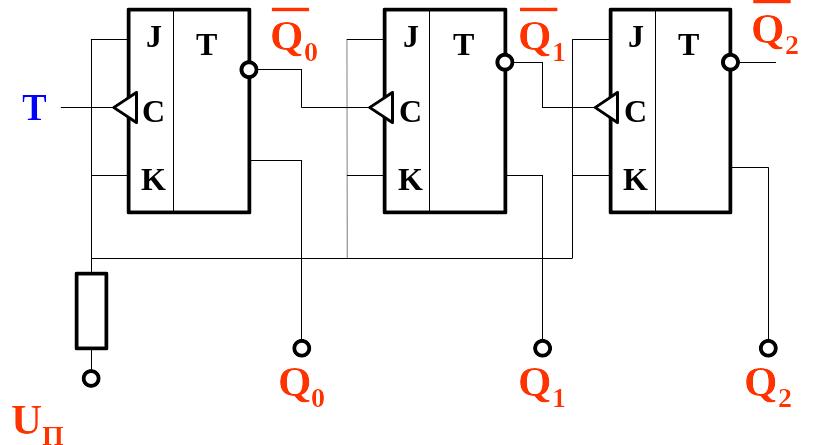

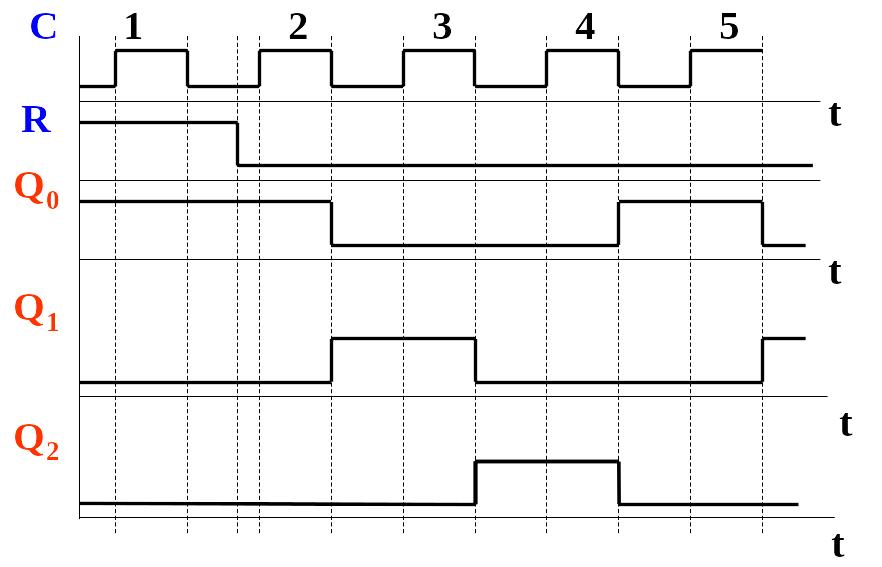

На рисунке 6.15 представлен счетчик импульсов, построенный на основе трех JK –триггеров, включенных каждый по схеме счетного Т – триггера.

Рисунок 6.15 –

Счетчик импульсов

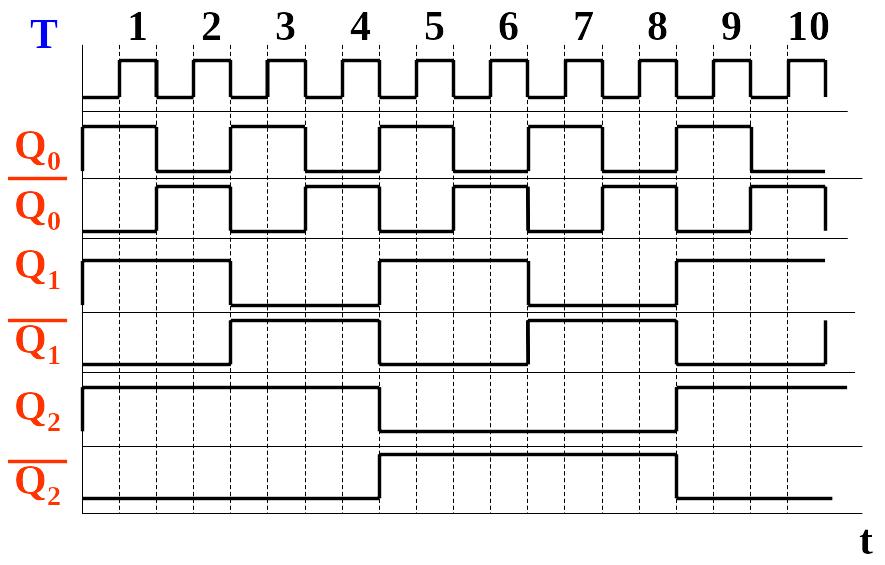

Временные диаграммы работы данного трехразрядного двоичного счетчика приведены на рисунке 6.16.

t

t

t

Рисунок 6.16 –

Временные диаграммы работы трехразрядного

суммирующего счетчика

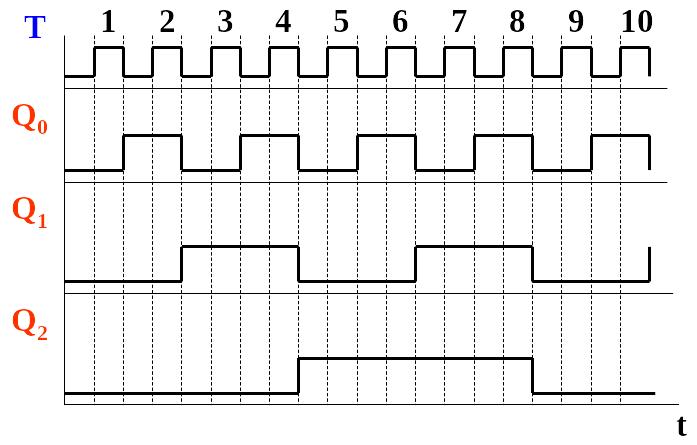

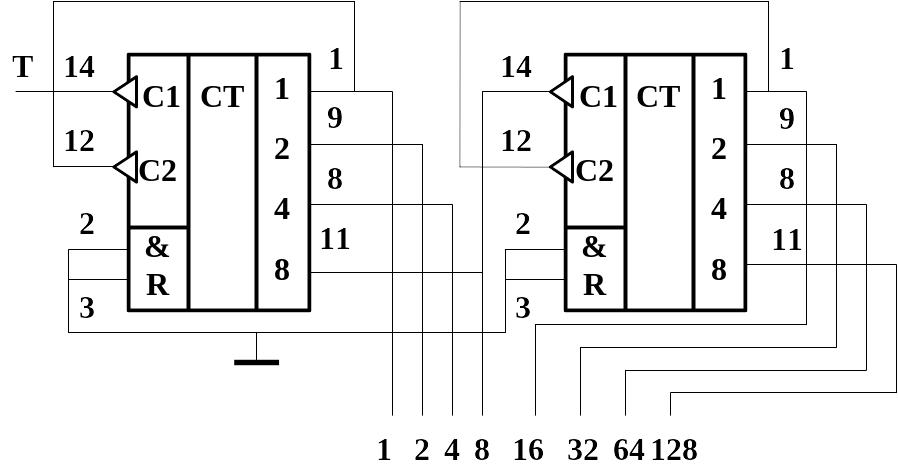

Микросхема К155ИЕ5 является суммирующим счетчиком с последовательным переносом (см. рисунок 6.17).

2

2

3

Рисунок 6.17 -

Структура микросхемы К155ИЕ5 и ее

графическое

изображение

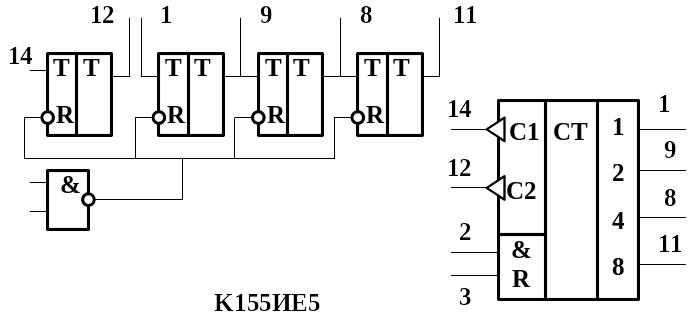

Для наращивания разрядности счетчиков их соединение в каскад осуществляют путем подачи сигнала старшего разряда предыдущей ИМС на счетный «Т» вход следующей (см. рисунок 6.18).

Рисунок 6.18 -

Каскадное включение счетчиков для

наращивания

разрядности

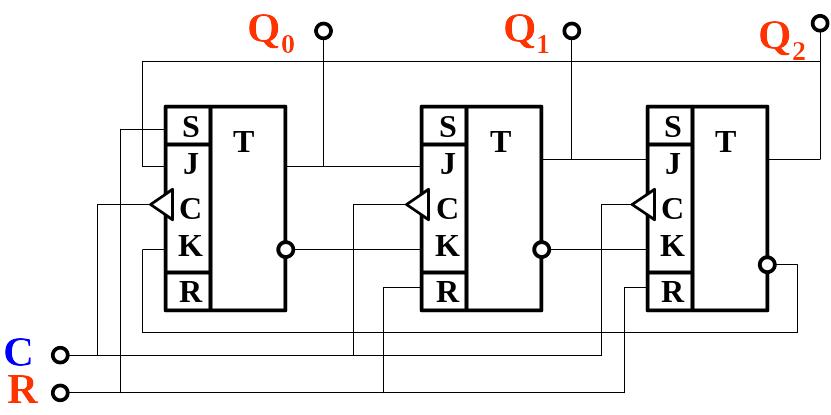

Вычитающий счетчик с последовательным переносом строится на основе тех же счетных триггеров (см. рисунок 6.19) с той лишь разницей, что передача информации от триггера к триггеру производится с применением инверсных выходов, а выходными разрядами являются выходы прямые.

На рисунке 6.20 изображена временная диаграмма состояний выходных разрядов вычитающего счетчика при подаче на вход «Т» цифрового сигнала в виде меандра.

Рисунок 6.19 -

Функциональная схема вычитающего

трехразрядного

счетчика

Если принять состояние выходных разрядов Q0 = Q1 = Q2 = 1 (соответствует десятичному числу 7), каждый последующий спад импульса на входе «Т» будет уменьшать итоговое значение выходного двоичного числа.

Рисунок 6.20 -

Временная диаграмма работы вычитающего

счетчика

Кроме счетчиков с последовательным переносом (импульсы с выхода одного счетного триггера поступают на вход следующего) существуют счетчики с параллельным переносом. Для этого переносимый со входа на выход двоичный код необходимо первоначально сформировать и только затем осуществить перенос по сигналу синхронизации.

Счетчики с параллельным переносом комплектуются дополнительными комбинационными ЛЭ, позволяющими реализовать данную функцию. Счетчики с параллельным переносом экономят время преобразования (счета).

На рисунке 6.21 приведены ИМС комбинированного типа. Структура последовательного счета реализуется подачей на входы суммирования «+1» (вход «-1» = 0) или вычитания «-1» (вход «+1» = 0) счетных импульсов. Для параллельного счета на входы D1-D8 предварительно необходимо подать соответствующий двоичный код, который по инверсному уровню входа «С» переносится на выходные разряды.

Рисунок 6.21 -

Реверсивные счетчики с комбинированным

переносом

Во всех предыдущих примерах информация на выходе счетчиков представляется в двоичном коде. Однако, в некоторых случаях требуется получить на выходных разрядах десятичный код, т.е. чтобы каждому счетному импульсу на входе соответствовал бы импульс на определенном выходе устройства (десятичный код). Реализация подобной задачи, в принципе уже рассматривалась, для этого необходимо выходные разряды двоичного счетчика подать на дешифратор. Но гораздо проще эта задача решается при использовании кольцевого счетчика (см. рисунок 8.8).

Временные диаграммы, поясняющие работу кольцевого счетчика, приведены на рисунке 8.9. Название счетчика определяется кольцом информации, подаваемой с выхода последнего счетного триггера на соответствующий вход устройства.

Рисунок 8.8 -

Кольцевой счетчик

Рисунок 8.9 -

Временные диаграммы работы кольцевого

счетчика