- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.6.2.2. Схемна реалізація зсуваючого регістру

Зсуваючі регістри призначені для виконання операції зсуву коду слова, тобто для переміщення цифр слова в напрямку від старших до молодших розрядів (зсув вправо) або від молодших до старших розрядів (зсув вліво). Зсув коду слова вліво на один розряд відповідає множенню коду числа на основу системи числення, а зсув вправо – діленню.

В регістрах, як правило, зсув числа на k розрядів здійснюється за k тактів або за k мікрооперацій зсуву. Мікрооперація зсуву – зсув числа на один розряд вправо або вліво відносно прийнятої розрядної сітки. Розряди, що вийшли при цьому із розрядної сітки регістра вліво або вправо, втрачаються, а в звільнені при зсуві розряди заносяться нулі. Можлива операція так званого циклічного зсуву, коли при зсуві вліво значення розряду, що вийшов із розрядної сітки не втрачається, а заноситься в наймолодший розряд регістру і при зсуві вправо значення розряду, що вийшов із розрядної сітки не втрачається, а заноситься в найстарший розряд регістру, тобто зсув відбувається по колу.

Регістри за способом виконання операції зсуву можна розділити на два основних типи:

з одночасною передачею інформації;

з парафазною передачею інформації.

За напрямком зсуву регістри прийнято розділяти на три види:

регістри, що зсувають код слова вправо (в сторону молодших розрядів);

регістри, що зсувають код слова вліво (в сторону старших розрядів);

реверсивні зсуваючі регістри, що здійснюють зсув інформації вправо або вліво в залежності від керуючих сигналів.

В залежності від способів прийому і видачі інформації зсуваючі регістри можна поділити на:

регістри з послідовним входом і послідовним виходом;

регістри з послідовним входом і послідовно-паралельними виходами;

регістри з послідовно-паралельними входами і виходами.

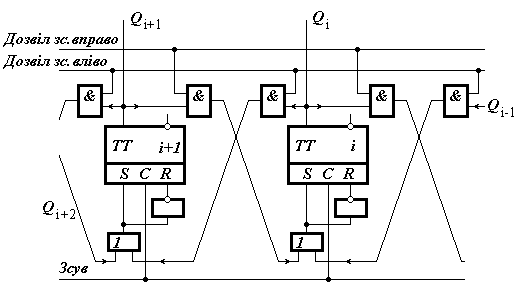

Рис. 4.62.

Зсуваючий регістр має такі ж вхідні і вихідні схеми, як і регістри прийому і видачі інформації, але вихід i-го розряду з’єднаний з встановлюючими входами сусіднього розряду ліворуч для реалізації зсуву вліво, або сусіднього розряду праворуч для реалізації зсуву вправо. Тригери зсуваючих регістрів повинні бути складними з проміжним внутрішнім запам’ятовуванням (як правило, двотактні). Якщо в зсуваючому регістрі використовуються прості тригери, наприклад RS-тригери, то необхідно використовувати ще один додатковий регістр для проміжного запам’ятовування слова в процесі зсуву. Фактично це призводить до того, що кожний розряд регістра буде складатись з двох тригерів (рис. 4.62).

На рис. 4.63 показані схеми зсуваючих регістрів, побудованих на інтегральних JK-тригерах.

Тут використовується один JK-тригер на кожний розряд зсуваючого регістра, оскільки інтегральний JK-тригер уявляє собою каскадне з’єднання двох однотактних тригерів з автоматичною передачею інформації від вхідного тригера до вихідного. З’єднав входи J і K JK-тригера i-го розряду з виходами Q і JK-тригера (i+1)–го розряду відповідно (рис. 4.63), отримаємо послідовність JK-тригерів, кожний з яких виконує функції D-тригера. Зсув здійснюється вправо.

Рис. 4.63.

Схема реверсивного зсуваючого регістра на JK–тригерах показана на рис. 4.64. Схема функціонує під дією пари сигналів, що надходять по шині «Зсув» і по одній із шин керування реверсом («Дозвіл зсуву вправо» / «Дозвіл зсуву вліво»), і має ту особливість, що передача інформації, яка зсувається на сусідній тригер, здійснюється не парафазним кодом, а по одній лінії зв’язку. Парафазний код утворюється вже безпосередньо на вході тригера за допомогою інвертора, який розташований перед входом R. Одночасна подача одиничних сигналів на шини «Дозвіл зсуву вправо» і «Дозвіл зсуву вліво» заборонена, оскільки в цьому випадку інформація в регістрі під дією сигналу «Зсув» буде зіпсована. При нульових сигналах на цих шинах сигнал «Зсув» здійснить погашення регістра (встановить 0 на всіх тригерах регістру).

Рис. 4.64.

Зсуваючі регістри можна використовувати не тільки для зсуву коду, але і для перетворення паралельного коду, прийнятого в регістр, в послідовний. Для цього достатньо прийнятий код зсувати до тих пір, поки він не буде висунутий з регістру. Вихід з крайнього розряду використовується як вихідна шина послідовного коду. Зсуваючі регістри може виконувати також функцію перетворення послідовного коду в паралельний.