- •Структурно-функціональна організація апаратного та програмного забезпечення обчислювачів.

- •1.4 Структура аом

- •1.5 Структура гом

- •Системи машинних команд процесорів, формати даних і способи кодування команд і даних.

- •Способи організації доступу до даних та методи адресування команд і даних.

- •1.4 Організація підсистеми пам’яті комп’ютера.

- •1.5 Способи організації взаємодії апаратного забезпечення із системним програмним забезпеченням.

- •1.6 Взаємодія комп’ютера із зовнішніми пристроями.

- •Елементна база комп’ютерів.

- •2.2 Архітектура мп 80486, Pentium, мп adsp.

- •Базовая архитектура процессоров adsp-21xx

- •2.3 Архітектура процесора 80с51.

- •2.4 Risc-процесори ті їх архітектура.

- •2.5 Адресний простір. Способи адресації операндів.

- •2.6 Оперативна пам’ять: архітектура та принципи управління.

- •2.7 Система переривань та їх характеристики.

- •2.8 Динамічний розподіл пам’яті. Організація віртуальної пам’яті.

- •3.1 Склад системного програмного забезпечення.

- •3.2 Класифікація операційних систем.

- •Особенности алгоритмов управления ресурсами

- •Особенности аппаратных платформ

- •Особенности областей использования

- •Особенности методов построения

- •3.3 Різновиди мультизадачності в операційних системах.

- •3.4 Процеси та потоки в операційних системах.

- •Реальний та захищений режими адресації.

- •Особенности процессора 80286

- •Особенности процессоров 80386 — 80486

- •Страничная организация памяти

- •Описание

- •Использование

- •Структура адресного пространства ibm pc в реальном режиме Основная область памяти

- •Дополнительная область памяти

- •3.6 Оперативна пам’ять в мультизадачному режимі.

- •Алгоритми заміщення сегментів та сторінок у віртуальній пам’яті.

- •Структура жорсткого диску.

- •Vfat и длинные имена файлов

- •Файлова система hpfs.

- •Файлова система ntfs.

- •Керування процесами у операційних системах, їх стани та переходи. Управление процессами

- •Состояние процессов

- •Контекст и дескриптор процесса

- •Алгоритмы планирования процессов

- •Вытесняющие и невытесняющие алгоритмы планирования

- •3.11 Основні режими введення-виведення.

- •3.12 Оптимізація роботи з жорстким диском.

- •4.1 Структура системних областей пам’яті (ms-dos).

- •4.2 Програмування дискової підсистеми комп’ютера (mbr, Partition Table, fat12/16/32).

- •4.3 Програмування відеосистеми комп’ютера (cga, ega, vga).

- •4.4 Особливості програмування текстового та графічного режимів відеоадаптера.

- •4.5 Робота з маніпулятором миші (ms-dos, ms-Windows).

- •4.6 Обробка переривань.

- •4.1. Таблица векторов прерываний

- •4.2. Маскирование прерываний

- •4.4. Особенности обработки аппаратных прерываний

- •4.8 Ініціалізація dll-бібліотек, динамічний експорт та імпорт функцій у середовищі Microsoft Windows. Бібліотеки динамічної компоновки. Ініціалізація dll.

- •2.23.1. Статическая и динамическая компоновка

- •Експорт та імпорт функцій при використанні dll-бібліотек.

- •5.1 Системні та локальні шини, основні характеристики.

- •5.2 Шини з комутацією ланцюгів та комутацією пакетів. Розщеплення транзакцій.

- •5.3 Шини Firewire (ieee 1394), pci, pci-e, основні характеристики.

- •Особенности ieee - 1394

- •Шини pci основні характеристики.

- •ШиниPci-е, основні характеристики.

- •5.4 Стандарт ieee 1284 – 1994, фізичний та електричний інтерфейси.

- •5.6 Характеристики сучасних жорстких дисків.

- •5.7 Інтерфейси жорстких дисків в ibm pc, їх особливості.

- •5.8 Характеристики сучасних принтерів, сканерів.

- •5.9 Структура та принцип роботи сучасних модемів.

- •5.10 Основні характеристики джерел безперервного живлення.

- •6.1 Архітектура і стандартизація комп’ютерних мереж.

- •6.2 Лінії зв’язку: класифікація, характеристики, типи кабелів.

- •6.3 Методи кодування даних у комп’ютерних мережах.

- •6.4 Технології канального рівня tcp/ip та їх специфікації. Стек протоколов tcp/ip История и перспективы стека tcp/ip

- •Структура стека tcp/ip. Краткая характеристика протоколов

- •6.5 Мережеве обладнання: класифікація, функції.

- •Параметры сетевого адаптера

- •Функции и характеристики сетевых адаптеров

- •Классификация сетевых адаптеров

- •6.6 Протоколи локальних мереж: tcp, udp, iPv4, iPv6 та ін.

- •36. Протоколи транспортного рівня tcp и udp (загальна характеристика, порти)

- •37. Протокол транспортного рівня udp

- •Адресация iPv4

- •Синтаксис адреса iPv4

- •Типы адресов iPv4

- •Индивидуальные адреса iPv4

- •Групповые адреса iPv4

- •Широковещательные адреса iPv4

- •История создания

- •Исчерпание iPv4 адресов в 2011 году

- •Тестирование протокола

- •Внедрение протокола

- •Сравнение с iPv4

- •Автоконфигурация

- •Метки потоков

- •Механизмы безопасности

- •Основы адресации iPv6

- •Типы Unicast адресов

- •Формат пакета

- •Нотация

- •Зарезервированные адреса iPv6

- •6.7 Адресація в комп’ютерних мережах.

- •Ip адресация, классы ip адресов и значение маски подсети

- •Для чего нужны ip адреса?

- •Структура ip адреса

- •Разделение ip адреса на сетевую и узловую части

- •Классы ip адресов и маски подсети по умолчанию

- •Классовая и бесклассовая адресация

- •Назначение маски подсети

- •Публичные и частные ip-адреса

- •Адреса одноадресных, широковещательных и многоадресных рассылок

- •Одноадресная рассылка

- •Широковещательная рассылка

- •Многоадресная рассылка

- •Сравнение протоколов ip версии 4 (iPv4) и ip версии 6 (iPv6)

- •6.8 Об’єктивні характеристики комп’ютерних мереж.

- •6.9 Схема ip-маршрутизації.

- •6.10 Фрагментація ip-пакетів. Фрагментация ip-пакетов

- •6.11 Служби dns та dhcp.

- •Ключевые характеристики dns

- •Дополнительные возможности

- •Терминология и принципы работы

- •Рекурсия

- •Обратный dns-запрос

- •Записи dns

- •6.12 Протоколи маршрутизації. Протоколы маршрутизации

- •Віртуальні приватні мережі.

- •Уровни реализации

- •Структура vpn

- •Классификация vpn

- •По степени защищенности используемой среды

- •По способу реализации

- •По назначению

- •По типу протокола

- •По уровню сетевого протокола

- •6.14 Засоби забезпечення надійності функціонування та захисту комп’ютерних мереж.

- •7.1 Основи мови програмування Java.

- •7.2 Проміжне програмне забезпечення розподілених комп’ютерних систем. Архітектура rpc (Remote Procedure Calls).

- •7.3 Технологія rmi (Remote Method Invocation).

- •24. Java rmi Достоинства и недостатки Java rmi

- •7.4 Технологія corba .

- •7.5 Сервлет-технологія Java.

- •7.6 Сторінки jsp. Теги та вбудовані об’єкти jsp.

- •26. Теги и встроенные объекты jsp:

- •7.7 Технологія jms. Моделі jms-повідомлень.

- •Введение

- •Архитектура jms

- •Первое знакомство

- •Модель сообщений jms

- •Поля заголовка

- •Свойства (properties) сообщений

- •Уведомления сообщений

- •Интерфейс Message

- •Выборка сообщений

- •Доступ к отправленным сообщениям

- •Изменение полученного сообщения

- •Тело сообщения

- •7.8 Основи мови xml.

- •7.9 Протокол soap. Структура soap – документа.

- •1.4. Операторы

- •1.4.1. Оператор выражение

- •1.4.2. Пустой оператор

- •1.4.3. Составной оператор

- •1.4.4. Оператор if

- •1.4.5. Оператор switch

- •1.4.6. Оператор break

- •1.4.7. Оператор for

- •1.4.8. Оператор while

- •1.4.9. Оператор do while

- •1.4.10. Оператор continue

- •1.4.11. Оператор return

- •1.4.12. Оператор goto

- •8.2 Одновимірні та багатовимірні масиви. Покажчики. Масиви динамічної пам’яті.

- •8.3 Структури, об’єднання, бітові поля структур та об’єднань.

- •Объявление битовых полей

- •Доступ к элементам структур с битовыми полями

- •Размещение битовых полей в памяти

- •Призначення функції. Опис, визначення, виклик функції. Передача даних за значенням та за покажчиком.

- •Функції з параметрами, що замовчуються, зі зміними параметрами

- •8.5 Перевантаження функцій. Шаблони функцій. Покажчики на функції. Перевантажені функції, шаблони функцій.

- •8.6 Функції роботи з файлами. Введення/виведення даних різного типу у файл/з файлу.

- •Int fprintf(file *fp, char *format [,аргумент]…);

- •Int fscanf(file *fp, char *format [,указатель]…);

- •Визначення класу. Конструктор, перевантажені конструктори, деструктор.

- •8.8 Статичні члени класу. Дружні функції класу. Перевантаження операцій.

- •18 Ооп. Поняття дружніх функціїй. Різниця між дружньою функцією - членом класу та не членом класу.

- •19 Ооп. Поняття перевантаження операцій. Правила її використання.

- •8.9 Успадкування класів. Множинне успадкування.

- •9.1 Векторні, паралельні, конвеєрні системи.

- •9.2 Основні характеристики паралельних алгоритмів: ступінь паралелізму, прискорення, ефективність. Закон Амдала.

- •Математическое выражение

- •Иллюстрация

- •Идейное значение

- •9.3 Метод логарифмічного здвоєння та рекурсивного подвоєння.

- •9.4 Методи паралельного множення матриць. §34. Алгоритм умножения матриц

- •9.5 Стандарт mpi, основні функції для організації паралельних програм: ініціалізації та завершення паралельної програми, визначення рангу процесу, визначення загального числа процесів.

- •9.6 Функції двохточкового обміну.

- •9.7 Функції колективного обміну: розподілення, широкомовної розсилки, збору, зведення, сканування.

- •10.1 Архітектура субд. Функції субд.

- •2.1. Основные функции субд

- •2.1.1. Непосредственное управление данными во внешней памяти

- •2.1.2. Управление буферами оперативной памяти

- •2.1.3. Управление транзакциями

- •2.1.4. Журнализация

- •2.1.5. Поддержка языков бд

- •10.2 Реляційна модель та її характеристики.

- •10.3 Потенційні, первинні та зовнішні ключі.

- •10.4 Цілісність реляційних даних. Целостность реляционных данных

- •10.5 Операції реляційної алгебри.

- •10.6 Основні поняття sql: прості запити, склеювання таблиць; умови відбору рядків таблиць; агрегатні функції, запити з групуванням, складні запити. Sql. Простые запросы

- •Агрегатные функции, группировка данных

- •Запрос с группировкой

- •Пояснения

- •Сложные запросы

- •Объединение таблиц

- •Имена таблиц и столбцов

- •Создание обьединения

- •Объединение таблиц через справочную целостность

- •Объединения таблиц по равенству значений в столбцах и другие виды объединений

- •Объединение более двух таблиц

- •Объединение таблицы с собой псевдонимы

- •10.7 Інфологічна, логічна або концептуальна модель даних. Основные этапы проектирования баз данных Концептуальное (инфологическое) проектирование

- •Логическое (даталогическое) проектирование

- •Физическое проектирование

- •10.8 Функціональні залежності. 1, 2 та 3 нормальні форми відношень.

- •8 Нормалізація відношень. 1 та 2 нормальні форми.

- •9 Нормалізація відношень. 3 нормальна форма та нормальна форма Бойса-Кодда. Навести приклади

- •Нормальные формы er-диаграмм

- •Первая нормальная форма er-диаграммы

- •Вторая нормальная форма er-диаграммы

- •Третья нормальная форма er-диаграммы

- •Семантическая модель Entity-Relationship (Сущность-Связь)

- •Основные понятия er-модели

- •Уникальные идентификаторы типов сущности

- •Нормальные формы er-диаграмм

- •Первая нормальная форма er-диаграммы

- •Вторая нормальная форма er-диаграммы

- •Третья нормальная форма er-диаграммы

- •10.9 Багатозначні залежності та залежності з’єднання. 4 та 5 нормальні форми відношень.

- •9.3. Зависимости проекции/соединения и пятая нормальная форма

- •9.3.2. Зависимость проекции/соединения

- •9.3.3. Аномалии, вызываемые наличием зависимости проекции/соединения

- •9.3.4. Устранение аномалий обновления в 3-декомпозиции

- •2.5.5. Пятая нормальная форма

- •4.5. Нормальные формы

- •10.10 Проектування бд методом сутність-зв’язок. Er-діаграми. Моделирование методом "сущность-связь" Основные понятия модели "сущность-связь"

- •Графическая нотация модели: диаграммы "сущность-связь"

- •Нормализация модели "сущность-связь"

- •11.1 Властивості інформації. Класифікація загроз інформації.

- •11.2 Рівні захисту інформації в комп’ютерних мережах.

- •11.3 Законодавчий рівень захисту інформації.

- •11.4 Криптографічний захист інформації.

- •11.5 Стандарти симетричного шифрування даних.

- •11.6 Системи ідентифікації та аутентифікації користувачів.

- •11.7 Парольна система. Вимоги до паролів.

- •11.8 Методи та засоби захисту від віддалених мережевих атак.

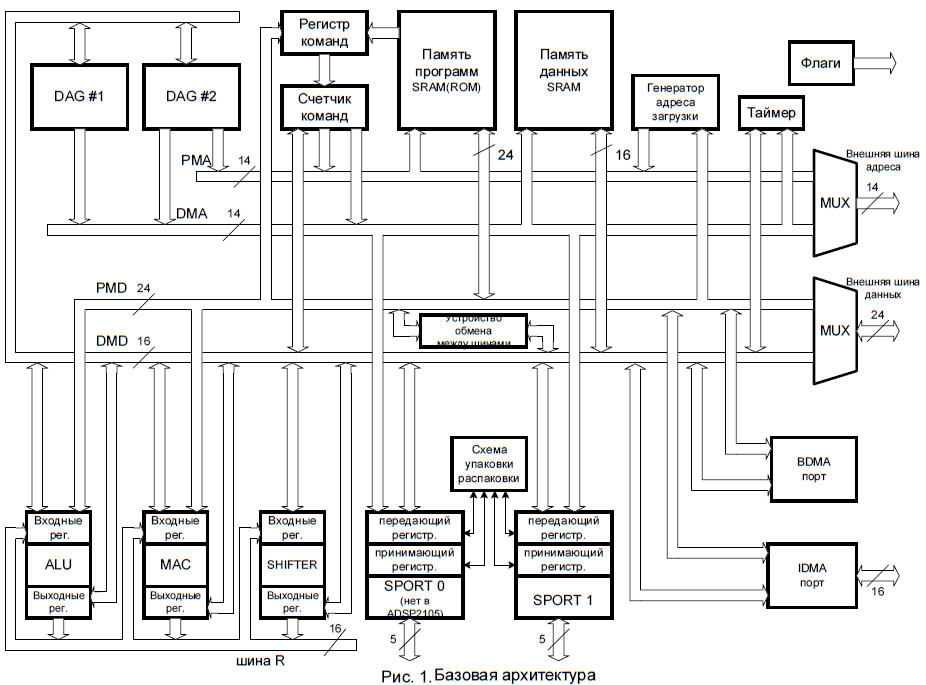

Базовая архитектура процессоров adsp-21xx

Базовая архитектура процессоров семейства представлена на рис. 1. Ее основные компоненты имеют следующее функциональное назначение. Три независимых вычислительных устройства арифметико-логическое (АЛУ), умножитель/аккумулятор (MAC) и устройство циклического сдвига (SHIFTER) реализуют функционально полный набор вычислительных операций с 1 6-битовыми данными и аппаратную поддержку операций с числами повышенной точности. Они организованы так, что результаты работы любого устройства могут быть операндами другого устройства в следующем цикле процессора. Два специальных устройства генерации адресов данных DAG (Data Address Generator) генерируют адреса памяти данных, пересылаемых из входных или выходных регистров вычислительных устройств. Наличие двух генераторов адреса данных позволяет выполнять процессору две адресные инструкции за один цикл.

Программный автомат процессора, называемый также генератором адресов инструкций, управляет выполнением программы. На блок-схеме базовой архитектуры он упрощенно представлен счетчиком команд, формирующим адреса инструкций для памяти программ. С ним связан также регистр команд, содержащий исполняемую в данный момент инструкцию и буферизующий исполнение программы.

Устройство памяти процессора включает раздельную память программ (PM) типа ОЗУ или ПЗУ, где могут храниться также и данные, и память данных (DM) типа ОЗУ.

Внутренние устройства процессора связаны 14-разрядными шинами адреса памяти данных DMA (Data Memory Address) и адреса памяти программ PMA (Program Memory Address), 16-разрядной шиной данных памяти данных DMD (Data Memory Data) и 24-разрядной шиной данных памяти программ PMD (Program Memory Data). Они мультиплексированы в две выводимые наружу внешние шины, шину адреса и шину данных. По шине внутренних результатов R осуществляется прямой обмен данными между вычислительными устройствами.

Устройство обмена данными между шинами PMD - DMD аппаратно поддерживает двунаправленную передачу данных между памятью программ и вычислительными устройствами процессора.

Два двунаправленных последовательных порта (SPORT) с широким разнообразием аппаратно-реализуемых режимов передачи и приема данных обеспечивают полный синхронный последовательный интерфейс процессора.

Программируемый интервальный таймер выполняет периодическую генерацию внутренних прерываний.

Параллельный интерфейс представлен портами прямого доступа к памяти BDMA и IDMA.

2.3 Архітектура процесора 80с51.

Intel 8051 — это однокристальный микроконтроллер (не путать с процессором) гарвардской архитектуры, который был впервые произведен Intel в 1980 году, для использования во встраиваемых системах. В течение 1980-х и начале 1990-х годов был чрезвычайно популярен. Однако, в настоящее время устарел и вытеснен более современными устройствами, с 8051-совместимыми ядрами, производимыми более чем 20 независимыми производителями, такими как Atmel, Maxim IC (дочерняя компания Dallas Semiconductor), NXP (ранее Philips Semiconductor), Winbond, Silicon Laboratories, Texas Instruments и Cypress Semiconductor. Существует также советский клон данной микросхемы, КР1816ВЕ51. Официальное название 8051-семейства микроконтроллеров Intel — MCS 51.

Первые из 8051-семейства Intel производились с использованием n-МОП технологии, но следующие версии, содержащие символ «C» в названии, такие как 80C51, использовали КМОП-технологию и потребляли меньшую мощность, чем n-МОП предшественники (это облегчало их применение для устройств с питанием от батарей).

Состоит из процессорного ядра (CPU), ОЗУ, ПЗУ, последовательного порта, параллельного порта, логики управления прерываниями, таймер и т. д.

Шина данных — 8-ми битная шина данных. Возможность обработки 8 бит данных за одну операцию. Обуславливает название 8-битный микропроцессор

Шина адреса — 16 битная адресная шина. Возможность доступа к 216 адресам памяти, то есть 64 кБ адресное пространство в ОЗУ и ПЗУ

Встроенное ОЗУ — 128 байт (Памяти данных)

Встроенное ПЗУ — 4 КБ (Памяти программ)

Четыре порта ввода/вывода: один двунаправленный и три квазидвунаправленных

Последовательный интерфейс UART (Универсальный асинхронный приёмопередатчик)

Два 16-битных таймера

Два уровня приоритета прерываний

Энергосберегающий режим

Общей особенностью в современных 8051-совместимых микроконтроллерах стало встраивание улучшенных и дополнительных схем, таких как: автоматический сброс по падению питающего напряжения; встроенные тактовые генераторы; внутрисхемное программирование памяти программ; автозагрузчики долговременной памяти данных на основе EEPROM; I²C ; SPI (стандарт 3-проводной последовательной шины); USB хост-интерфейс; ШИМ-генераторы; аналоговых компараторов; АЦП и ЦАП преобразователей; часов реального времени; дополнительных таймеров и счетчиков; внутрисхемных отладчиков, дополнительных источников прерываний; расширенных энергосберегающих режимов.

8051-совместимые микроконтроллеры обычно имеют один или два УАПП (UART), два или три таймера, 128 или 256 байт встроенной ОЗУ (16 байт которой имеют побитовую адресацию), от 512 байт до 128 Кбайт встроенной памяти программ (ПЗУ), и иногда встречается использование EEPROM, адресуемой через «регистры специального назначения» (SFR = special function register). УАПП/UART может быть настроен для использования в режиме 9-бит данных, что делает возможным адресную приёмопередачу в многоточечном подключении на основе RS-485 аппаратного протокола.

Один машинный цикл оригинального 8051-ядра занимает 12 временных тактов, а большинство инструкций выполняется за один или два машинных цикла. При частоте тактового генератора, равной 12 МГц, 8051-ядро может выполнять 1 миллион операций в секунду, выполняемых за один цикл, или 500 тысяч операций в секунду, выполняемых за два цикла. Улучшенное 8051-совместимое ядро, которое в настоящее время распространено, выполняет машинный цикл за шесть, четыре, два, или даже за один временной такт, и позволяет использовать тактовые генераторы с частотой до 100 МГц, что позволило увеличить количество выполняемых операций в секунду.

Еще более быстрые 8051-ядра, с 1 тактом на машинный цикл, организуются с использованием ПЛИС, таких как FPGA (скорость в диапазоне 130—150 МГц) или ASIC (скорость в диапазоне нескольких сотен МГц), при помощи специальной прошивки[1]. Все 8051-совместимые устройства, производимые SILabs, некоторые из производимых Dallas и немногие из производимых Atmel имеют ядро с 1 тактом на машинный цикл.

Чрезвычайно полезной особенностью 8051-ядра является обработка булевых данных, что позволило ввести бинарную логику, оперирующую напрямую с битами внутренней ОЗУ (области из 128 прямо-адресуемых битов) и регистров. Данная особенность была востребована в приложениях промышленной автоматики. Еще одна ценная особенность состояла в 4 независимых наборах регистров, которые значительно уменьшали задержки при обработке прерываний, в сравнении с классическим использованием стека, применявшимся ранее.

Предшественником контроллера 8051 был Intel 8048, который был применён в клавиатуре первого компьютера IBM PC — он конвертировал сигналы о нажатиях клавиш в поток данных, передававшийся по последовательной линии в системный блок компьютера. Контроллер 8048, а также контроллеры, спроектированные на его базе, всё ещё применяются в клавиатурах.

Контроллер 8031 является урезанной версией Intel 8051: у него отсутствует встроенная память для хранения программы.

Контроллер 8052 является расширенной версией оригинального Intel 8051: он оснащён 256 байтами внутреннего ОЗУ (вместо 128 байт 8051), 8 КБ ПЗУ (вместо 4 КБ), также ему добавлен третий 16-разрядный таймер.

Контроллер 8032 аналогичен 8052, но не имеет встроенной памяти для хранения программы. Контроллеры 8052 и 8032 считаются устаревшими, так как почти все современные варианты 8051 оснащены теми расширениями, которыми обладает 8052.

Для 8051 доступно несколько компиляторов с языка программирования Си, большинство из которых поддерживает расширения языка для более эффективного использования особенностей 8051. Например, программист может указать, в каком из шести типов памяти 8051 необходимо хранить переменную; компилятору можно указать, каким образом использовать переключаемые регистровые блоки и инструкции для манипулирования отдельными разрядами регистров.

Для программирования 8051 используются и другие языки высокого уровня: Форт, Бейсик, Паскаль, PL/M и Modula-2, однако они не получили такого широкого распространения как Си и ассемблер.