- •Блоки питания ат и атх. Выходные напряжения. Принципиальные отличия блоков ат и атх

- •Стандарт usb On the Go.

- •Интерфейс 1394 Fire Wire. Устройство интерфейсного кабеля. Game-порт компьютера.

- •Устройство и структура cd-r диска и cd-rw дисков. Считывание информации с cd-r диска. Технологии clv, cav, pcav

- •Технологии clv, cav, pcav???????????????????????????????????

- •Уровни кеша

- •Характеристика кеша.

- •Материнские платы Hub-архитектуры

- •Классификация памяти компьютера.

- •Существует несколько типов памяти:

- •Sdram и ddr память. Способы повышения производительности памяти.

- •Способы повышения производительности памяти.

- •Устройство и принцип работы клавиатуры.

- •Устройство и принцип работы манипулятора мышь.

- •Устройство и принцип работы накопителя на жестких дисках.

Уровни кеша

Разделение кеш-памяти на несколько уровней (до 3 для универсальных процессоров по состоянию на начало 2007 года). Кеш-память уровня N+1 всегда больше по размеру и медленнее по скорости обращения, чем кеш-память уровня N.

Самой быстрой памятью является кеш-память первого уровня (она же L1-cache), по сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков, без неё процессор не сможет функционировать. Память L1 работает на частоте процессора, и в общем случае обращение к ней может производится каждый такт (зачастую является возможным выполнять даже несколько чтений/записей одновременно), латентность доступа обычно равна 2—4 такта ядра, объём этой памяти обычно невелик — не более 64 Кб. Второй по быстродействию является L2 (в отличие от L1 её можно отключить с сохранением работоспособности процессора), кеш второго уровня, она обычно расположена либо на кристалле, как и L1, либо в непосредственной близости от ядра, например, в процессорном картридже (только в слотовых процессорах), в старых процессорах её располагали на системной плате. Объём L2 побольше — от 128 Кб до 1—4 Мб. Обычно латентность L2 расположенной на кристалле ядра составляет от 8 до 20 тактов ядра. Кеш третьего уровня наименее быстродействующий и обычно расположен отдельно от ядра ЦП, но он может быть очень внушительного размера и всё равно значительно быстрее чем оперативная память.

Характеристика кеша.

Одна из фундаментальных характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию. Дело в том, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жёстко привязываются к строкамкэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска.

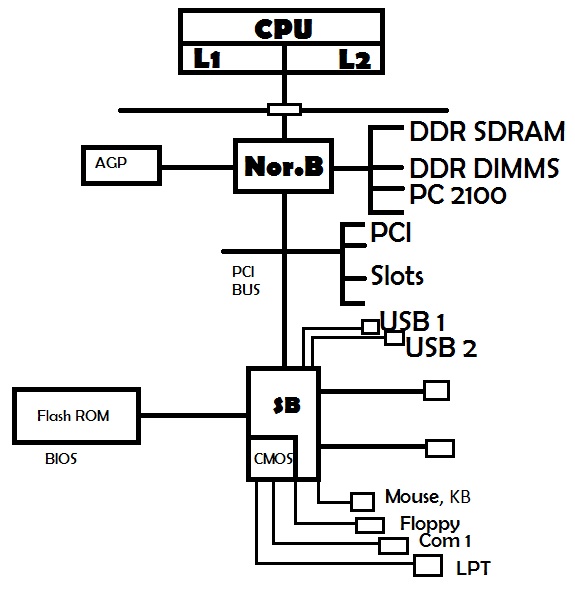

Архитектура материнской платы North-South Bridge/

Большинство наборов микросхем системной логики имеют двухуровневую архитектуру и состоящую из двух блоков: North Bridge и South Bridge, северный и южный мост.

Основным блоком набора микросхем системной логики является North Bridge , в него включен интерфейс между процессором и остальной частью ситемной платы.

North Bridge содержит

1 контролер кэш-памяти

2 контролер оперативной памяти

3 интерфейс между быстродействующей шиной процессора (33, 50, 66, 100, 133, 200 МГц), шиной PCI ( Peripheral Component Interconnect , 33МГц) и шиной ускоренного графического порта AGP ( Accelerated Graphics Port , 66МГц).

North Bridge , по существу, главный компонент системной платы; она работает на частоте шины системной платы. В большинстве современных плат North Bridgeреализован в виде одного кристалла.

South Bridge – компонент в наборе микросхем системной логики с более низким быстродействием; он всегда находиться на отдельной микросхеме. South Bridgeподключается к шине PCI (33МГц) и содержит интерфейс шины ISA (8МГц). Также содержит интерфейс контроллера жесткого диска IDE и интерфейс USB ( Universal serialBus – универсальная последовательная шина), а также схемы, реализующие функции памяти CMOS и часов.

В новых материнских платах, мосты соединяются HUB шиной.