- •Вопрос 1

- •Вопрос 2

- •Алгоритм работы управляющего автомата

- •Inta - признак начала работы в режиме прерывания.

- •Вопрос 3

- •Способы адресации

- •Спецкоманды

- •Псевдокоманды

- •2.4. Способы адресации

- •2.5. Форматы команд 16-разрядного мп

- •2.6. Система команд 16-разрядного мп

- •2.6.1. Команды передачи данных

- •2.6.2. Команды обработки данных

- •2.6.3. Команды управления

- •2.6.4. Команды условного перехода

- •2.6.5. Команды обработки цепочек данных

- •Вопрос 4

- •Вопрос 5

- •Организация шин микроЭвм.

- •Увеличение нагрузочной способности шин мп

- •Шинные формирователи

- •Системный контроллер

- •Вопрос 6

- •Вопрос 7

- •Инициализация.

- •2 Разряда

- •Г Сброс раф работы первичного автомата

- •Вопрос 8

- •Структурная схема.

- •Режимы работы.

- •Управляющие слова, инициализация (уси).

- •Каскадная схема включения.

- •Вопрос 10

- •3.4. Обработка прерываний

- •3.5. Организация прямого доступа к памяти

- •3.6. Запуск и сброс микропроцессора

- •Вопрос 11

- •Вопрос 12

- •Вопрос 13

- •Вопрос 14

- •Вопрос 15

- •Сторожевые таймеры

- •Организация таймеров/счетчиков.

Вопрос 12

Микроконтроллеры с архитектурой AVR

Использована AVR расширенная RFSC архитектура

Мощный набор из 121 команды, большинство которых выполняется за один машинный цикл

Емкость внутри системно программируемой Flash памяти 128 Кбайт (АТmega103), 1000 циклов стирания/записи

SPI интерфейс внутрисистемного программирования

Емкость встроенной EEPROM 4 Кбайт ATmega103, 100000 циклов стирания/записи

Встроенная RAM емкостью 4 Кбайт

32 8-разрядных регистра общего назначения, набор регистров управления периферией

32 программируемых линии I/O, 8 линий выхода, 8 линий входа

Программируемые последовательные UART и SPI интерфейсы

Диапазон напряжений питания от 4,0 В до 6,0 В АТmega103

Диапазон тактовых частот от 0 до 6 МГц АТmega103

Производительность до 6 MIPS при частоте 6 МГц

Встроенная система реального времени с отдельным генератором

Два 8-разрядных таймера/счетчика с отдельным предделителем и ШИМ

1б-разрядный таймер/счетчик с отдельным предделителем, режимами захвата/ Сравнения и двойным ШИМ с разрядностью 8, 9 или 10 разрядов

Программируемый сторожевой таймер с встроенным генератором

Встроенный аналоговый компаратор

8-канальный 10-разрядный аналого-цифровой преобразователь

Режимы энергосбережения Idle, Power Save и Power Down

Программная установка тактовой частоты

Программная блокировка защиты программных средств

Вопрос 13

Методы адресации и система команд

1. регистровый способ адресации с одним регистром Rd

Данные, над которыми осуществляется операция (или используются при выполнении операции), находятся в регистре d (Rd).

Прямая регистровая адресация с двумя регистрами — Rd и Rr

Данные, над которыми осуществляется операция, находятся в регистрах г (Rr) и d (Rd). Результат операции сохраняется в регистре d (Rd).

INC

RD ADD

RD

Rr

INC

RD ADD

RD

Rr

2.непосредственная адресация к области ввода/вывода

OUT P,RR

n — адрес регистра, используемого в операции, находится непосредственно в коде команды, в битах 0...5.

3.Прямая адресация к памяти данных

1 6-разрядный

адрес ячейки памяти данных находится

в коде команды,

состоящей из двух слов. Rr/Rd

определяет регистр, используемый

при работе с памятью данных (т. е. регистр,

куда записываются

результаты операции либо откуда они

берутся для выполнения операции).

6-разрядный

адрес ячейки памяти данных находится

в коде команды,

состоящей из двух слов. Rr/Rd

определяет регистр, используемый

при работе с памятью данных (т. е. регистр,

куда записываются

результаты операции либо откуда они

берутся для выполнения операции).

4.Косвенная адресация к памяти данных со смещением

Адрес операнда определяется как сумма содержимого Z или Y регистра и бит 0...5 кода команды.

STD Y+q,RR

[RR]->M( [Y+q])

5.Косвенная адресация к памяти данных без смещения

Адрес операнда находится в Х-, Y- или Z-регистре.

ST Х,RR

[RR]->M([Х])

6.Косвенная

адресация к памяти данных с предварительным

декрементом

6.Косвенная

адресация к памяти данных с предварительным

декрементом

Адрес операнда находится в Х-, Y- или Z-регистре. Однако перед выполнением операции соответствующий индексный регистр Х-, Y-или Z уменьшается на единицу.

ST – Х,RR

[Х] -1 -> Х

[RR] ->M([Х])

7.Косвенная адресация к памяти данных с постинкрементом

А

ST Х+,RR

8.Адресация с использованием команд LPM и ELPM

А

ELPM

(M[Z]) ->RO

9.Косвенная адресация памяти программ IJMP и ICALL

П осле

операций IJMP или ICALL выполнение программы

продолжается с адреса, записанного

в Z-регистре (т. е. в PC счетчик команд

микроконтроллера записывается содержимое

Z-регистра).

осле

операций IJMP или ICALL выполнение программы

продолжается с адреса, записанного

в Z-регистре (т. е. в PC счетчик команд

микроконтроллера записывается содержимое

Z-регистра).

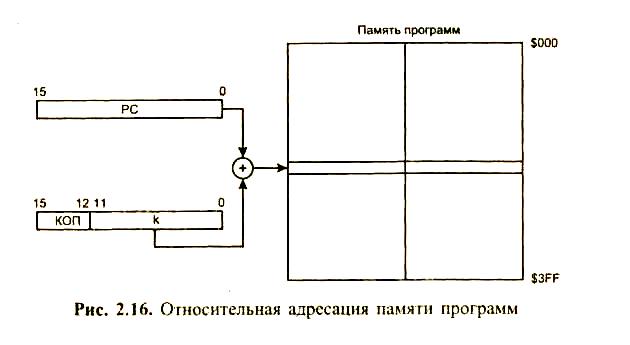

10.Относительная адресация памяти программ

После операций RJMP или RCALL выполнение программы продолжается с адреса PC+k+l. Относительный адрес к может составлять от-2048 до 2047.

PC +k

PC+k+1 ->PC

Система команд AVR

Арифметические и логические команды

Мнемоника |

Описание |

Действие |

Флаги |

Циклы |

ADD Rd.Rr |

Сложить два регистра |

Rd<Rd+Rr |

Z,C,N,V,H |

1 |

ADC Rd.Rr |

Сложить с переносом |

Rd<Rd+Rr+C |

Z,C,N,V,H |

1 |

ADIW Rdl.K |

Сложить слово с константой |

Rdh,KRdh,l+K |

Z,C,N,V,S |

2 |

SUB Rd.Rr |

Вычесть два регистра |

Rd<Rd-Rr |

Z,C,N,V,H |

1 |

SUBI Rd,K |

Вычесть константу |

Rd<Rd-K |

Z,C,N,V,H |

1 |

SBIW Rdl.K |

Вычесть слово с константой |

Rdh.KRdh.l-K |

Z,C,N,V,S |

2 |

SBC Rd.Rr |

Вычесть с переносом |

Rd<Rd-Rr-C |

Z,C,N,V,H |

1 |

SBCI Rd,K |

Вычесть с переносом |

Rd<Rd-K-C |

Z,CSN,V,H |

1 |

AND Rd,Rr |

Логическое И |

Rd<RdANDRr |

Z,N,V |

1 |

ANDI Rd.K |

Логическое И |

Rd<RdANDK |

Z.N.V |

1 |

OR Rd,Rr |

Логическое ИЛИ |

Rd<Rd OR Rr |

Z.N.V |

1 |

ORI Rd.K |

Логическое ИЛИ |

Rd<RdORK |

Z.N.V |

1 |

EOR Rd.Rr |

Исключающее ИЛИ |

Rd<RdXORRr |

Z,N,V |

1 |

COMRd |

Дополнение до 1 |

Rd<$FF-Rd |

Z,C,N,V |

1 |

NEGRd |

Дополнение до 2 |

Rd<$00 - Rd |

Z,C,N,V,H |

1 |

SBR Rd,K |

Установить бит(ы) в регистре |

Rd<Rd OR К |

Z,N,V |

1 |

CBR Rd.K |

Сбросить бит(ы) в регистре |

Rd<RdAND(FFh-K) |

Z,N,V |

1 |

INCRd |

Увеличить на 1 |

Rd<Rd+1 |

Z,N,V |

1 |

DECRd |

Уменьшить на 1 |

Rd<Rd-1 |

Z,N,V |

1 |

TSTRd |

Проверить на 0 или |

Rd<RdANDRd |

Z,N,V |

1 |

CLRRd |

Очистить регистр |

Rd<RdXORRd |

Z,N,V |

1 |

SERRd |

Установить регистр |

Rd<$FF |

None |

1 |

Команды ветвления

Мнемоник |

Описание |

Действие |

Флаги |

Циклы |

RJMPk |

Относительный переход |

РС<РС+к+1 |

None |

2 |

LJMP |

Переход по адресу (Z) |

PC<Z |

None |

2 |

RCALLk |

Относительный вызов подпрограммы |

РС<РС+к+1 |

None |

3 |

ICALL |

Вызов подпрограммы по адресу (Z) |

PC<Z |

None |

3 |

RET |

Выход из подпрограммы |

PC<STACK |

None |

4 |

REfl |

Выход из прерывания |

PC<STACK |

S |

4 |

CPSERd.Rr |

Сравнить, пропуск, если равно |

if(Rd=Rr) PC<PC+2 или З |

None |

1/2 |

CP Rd,Rr |

Сравнить |

Rd-Rr |

Z.N.V.C.H |

1 |

CPC Rd.Rr |

Сравнить с переносом |

Rd-Rr-C |

Z,N,V,C,H |

1 |

CPI Rd,K |

Сравнить с константой |

Rd-K |

Z,N,V,C,H |

1 |

BREQk |

Переход, если равно |

if(Z=1)PC<PC+k+1 |

None |

1/2 |

BRNEk |

Переход, если неравно |

if(Z=0)PC<PC+k+1 |

None |

1/2 |

BRCSk |

Переход, если установлен перенос |

if(C=1)PC<PC+k+1 |

None |

1/2 |

BRCCk |

Переход, если сброшен перенос |

if(C=O) PC<PC+k+1 |

None |

1/2 |

BRSHk |

Переход, если равно или больше |

if(C=O) PC<PC+k+1 |

None |

1/2 |

BRLO к |

Переход, если меньше |

if(C=1)PC<PC+k+1 |

None |

1/2 |

BRMIk |

Переход, если минус |

if(N=1)PC<PC+k+1 |

None |

1/2 |

BRPLk |

Переход, если плюс |

if(N=O) PC<PC+k+1 |

None |

1/2 |

BRGEk |

Переход, если больше или равно со знаком |

if(NXORV=0)PC<PC+k+1 |

None |

1/2 |

BRLTk |

Переход, если меньше нуля со знаком |

if(NXORV=1)PC<PC+k+1 |

None |

1/2 |

Команды пересылки

Мнемони |

Описание |

Действие |

Флаги |

Циклы |

MOVRd.Rr |

Пересылка между регистрами |

Rd<Rr |

None |

1 |

LDI Rd,K |

Загрузить константу |

Rd<K |

None |

1 |

LDRd,X |

Загрузить регистр непосредственно |

Rd<(X) |

None |

2 |

LD Rd,X+ |

Загрузить регистр непосредственно с постинкрементом |

Rd<(X),X<X+1 |

None |

2 |

ID Rd,-X |

Загрузить регистр непосредственно с предварительным декрементом |

X<X-1,Rd<(X) |

None |

2 |

LDRd.Y |

Загрузить регистр непосредственно |

Rd<(Y) |

None |

2 |

LD Rd,Y+ |

Загрузить регистр непосредственно с постинкремент. |

Rd<(Y),Y<Y+1 |

None |

2 |

LD Rd,-Y |

Загрузить регистр непосредственно с предварительным декрементом |

Y<Y-1,Rd<(Y) |

None |

2 |

LDD Rd,Y+q |

Загрузить регистр непосредственно со смещением |

Rd<(Y+q) |

None |

2 |

U)Rd,Z |

Загрузить регистр непосредственно |

Rd<(Z) |

None |

2 |

LD Rd,Z+ |

Загрузить регистр непосредственно с постинкрементом |

Rd<(Z),Z<Z+1 |

None |

2 |

LD Rd,-Z |

Загрузить регистр непосредственно с предварительным декрементом |

Z<Z-1,Rd<(Z) |

None |

2 |

LDD Rd,Z+q |

Загрузить регистр непосредственно со смещением |

Rd<(Z+q) |

None |

2 |

LDS Rd,k |

Загрузить из ОЗУ |

Rd<(k) |

None |

3 |

STX,Rr |

Записать регистр непосредственно |

(X)<Rr |

None |

2 |

STX+,Rr |

Записать регистр непосредственно с постинкрементом |

(X)<Rr,X<X+1 |

None |

2 |

ST -X,Rr |

Записать регистр непосредственно с предварительным декрементом |

X<X-1,(X)<Rr |

None |

2 |

STY,Rr |

Записать регистр непосредственно |

(Y)<Rr |

None |

2 |

STY+.Rr |

Записать регистр непосредственно с постинкрементом |

(Y)<Rr,Y<Y+1 |

None |

2 |

ST -Y.Rr |

Записать регистр непосредственно с пред.декрементом |

Y<Y-1,(Y)<Rr |

None |

2 |

STDY+q.Rr |

Записать регистр непосредственно со смещением |

(Y+q)<Rr |

None |

2 |

STZ,Rr |

Записать регистр непосредственно |

(Z)<Rr |

None |

2 |

STZ+.Rr |

Записать регистр непосредственно с постинкрементом |

(Z)<Rr,Z<Z+1 |

None |

2 |

ST-Z,Rr |

Записать регистр непосредственно с предварительным декрементом |

Z<Z-1,(Z)<Rr |

None |

2 |

STDY+q.Rr |

Запись регистра непосредственно со смещением |

(Y+q)<Rr |

None |

2 |

STSk.Rr |

Записать в ОЗУ |

(k)<Rr |

None |

3 |

LPM |

Загрузка из памяти программ |

R0<(Z) |

None |

3 |

IN Rd, P |

Ввод из порта |

Rd<P |

None |

1 |

OUTP.Rr |

Вывод в порт |

P<Rr |

None |

1 |

PUSH Rr |

Записать в стек |

STACK<Rr |

None |

2 |

POPRr |

Прочитать из стека |

Rr<STACK |

None |

2 |

Команды работы с битами

Мнемоника |

Описание |

Действие |

Флаги |

Циклы |

SBI Р,Ь |

Установить бит в регистре ввода/вывода |

1/О(Р,Ь)<1 |

None |

2 |

CBI Р,Ь |

Сбросить бит в регистре ввода/вывода |

l/O(P,b)<0 |

None |

2 |

LSLRd |

Логический сдвиг влево |

Rd(n+1)<Rd(n),Rd(0)<0 |

Z,C,N,V |

1 |

LSRRd |

Логический сдвиг вправо |

Rd(n)<Rd(n+1),Rd(7)<0 |

Z.C.N.V |

1 |

ROLRd |

Сдвиг влево через С |

Rd(0)<C,Rd(n+1)<Rd(n), C<Rd(7) |

Z.C.N.V |

1 |

RORRd |

Сдвиг вправо через С |

Rd(7)<C, Rd(n)<Rd(n+1), C<Rd(0) |

Z,C,N,V |

1 |

ASRRd |

Арифметический сдвиг вправо |

Rd(n)<Rd(n+1),n=0...6 |

Z,C,N,V |

1 |

SWAP Rd |

Обмен нибблов |

Rd(3-0)<Rd(7-4) Rd(7-4)<Rd(3-0) |

None |

1 |

BSETs |

Установить флаг |

SREG(s)<1 |

SREG(s) |

1 |

BCLRs |

Сбросить флаг |

SREG(s)<0 |

SREG(s) |

1 |

BST Rr,b |

Запомнить бит в Т |

T<Rr(b) |

T |

1 |

ВLD Rd,b |

Прочитать бит из Г |

Rd(b)<T |

None |

1 |

SEC |

Установить перенос |

C<1 |

С |

1 |

CLC |

Сбросить перенос |

C<0 |

С |

1 |

SEN |

Установить флаг N |

N<1 |

N |

1 |

CLN |

Сбросить флаг N |

N<0 |

N |

1 |

SEZ |

Установить флаг Z |

Z<1 |

Z |

1 |

CLZ |

Сбросить флаг Z |

Z<0 |

Z |

1 |

SEI |

Разрешить прерывания |

K1 |

I |

1 |

CU |

Запретить прерывания |

КО |

1 |

1 |

SES |

Установить флаг S |

S<1 |

S |

1 |

CLS |

Сбросить флаг S |

S<0 |

S |

1 |

SEV |

Установить флаг V |

V<1 |

V |

1 |

CLV |

Сбросить флаг V |

V<0 |

V |

1 |

SET |

Установить флаг Т |

T<1 |

T |

1 |

CLT |

Сбросить флаг Т |

T<0 |

T |

1 |

SEH |

Установить флаг Н |

H<1 |

H |

1 |

CLH |

Сбросить флаг Н |

H<0 |

H |

1 |

NOP |

Нет операции |

|

None |

1 |

SLEEP |

Останов |

|

None |

3 |

WDR |

Сброс сторожевого таймера |

|

None |

1 |