Индикаторы двоичных чисел

Шестнадцатиричное представление чисел

Дешифратор

Дешифратор

(декодер) — комбинационное

устройство,

преобразующее n-разрядный двоичный,

троичный или k-ичный код в ![]() -ичный

одноединичный код, где

-ичный

одноединичный код, где ![]() —

основание системы

счисления.

Логический сигнал появляется на том

выходе, порядковый номер которого

соответствует двоичному, троичному или

k-ичному коду.

Дешифраторы

являются устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции(операции).

—

основание системы

счисления.

Логический сигнал появляется на том

выходе, порядковый номер которого

соответствует двоичному, троичному или

k-ичному коду.

Дешифраторы

являются устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции(операции).

Синтез линейного дешифратора

Прямоугольный дешифратор

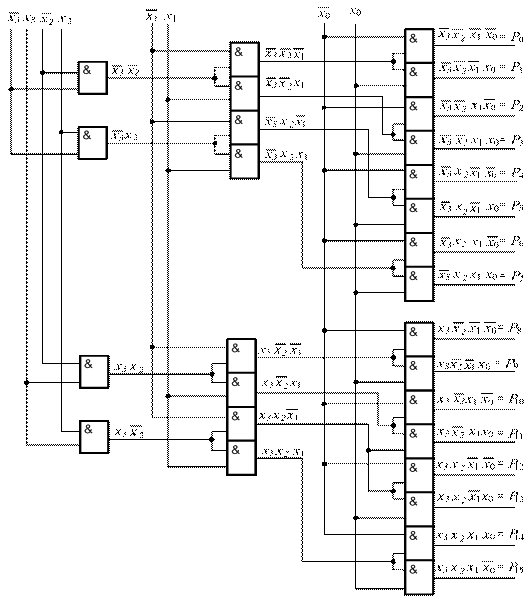

В прямоугольных дешифраторах n его входов разбиваются на две группы по n/2 переменных в каждой группе при четном n, при нечетном п группы должны содержать по (n+1)/2 и (п-1)/2 переменных (рисунок 3.9). Для каждой из двух групп строится линейный дешифратор. Эти дешифраторы составляют первую ступень дешифрации. Затем по матричной схеме с помощью элементов И на два входа каждая выходная шина одного дешифратора объединяется с каждой выходной шиной другого и таким образом получается вторая ступень дешифрации.

Пирамидальный дешифратор

Пирамидальные

дешифраторы, так же как и прямоугольные,

относятся к разряду многоступенчатых

дешифраторов, особенностью которых

является применение во всех ступенях

дешифрации двухвходовых

элементов И

с обязательным подключение выхода

элемента i-ой ступени ко входам только

двух элементов (i+1)-ой группы. Число

ступеней N в таком дешифраторе на единицу

меньше разрядности n дешифрируемого

слова, т.е. N = n – 1, а число элементов И в

каждой из ступеней определяется из

выражения B = 2i+1,

где ![]() –

номер ступени пирамидального дешифратора.

–

номер ступени пирамидального дешифратора.

Пирамидальные

дешифраторы строятся следующим образом.

В начале получаются все произведения

двух аргументов: ![]() ,

, ![]() ,

, ![]() и

и ![]() .

Затем получаются все конъюнкции 3-х

аргументов путем умножения каждого из

полученных произведений 2-х аргументов

на

.

Затем получаются все конъюнкции 3-х

аргументов путем умножения каждого из

полученных произведений 2-х аргументов

на ![]() и

и ![]() ,

затем все конъюнкции 4-х аргументов.

Другими словами, каждая функция системы

(11.1) формируется поэтапно. Это соответствует

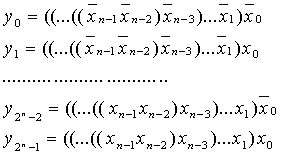

записи системы (11.1) в следующем виде:

,

затем все конъюнкции 4-х аргументов.

Другими словами, каждая функция системы

(11.1) формируется поэтапно. Это соответствует

записи системы (11.1) в следующем виде:

Рис. (11.3)

Принцип построения пирамидального дешифратора наглядно виден из примера построения такого дешифратора на 16 выходов (рис.11.6).

Рис.11.6

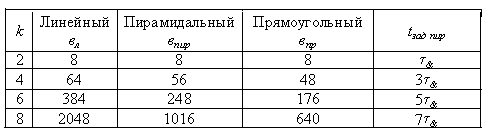

Быстродействие прямоугольного дешифратора определяется временем задержки, равным (n – 1)t&, а общее число входов у элементов равно:

![]()

Недостатком пирамидального дешифратора следует считать большое число ступеней, снижающих быстродействие дешифратора. Сравним по числу входов у элементов И и по быстродействию рассмотренных дешифраторы:

При n®¥

![]()

т.е. при больших значениях n прямоугольный дешифратор почти в 2 раза экономичнее пирамидального и в тоже время имеет большее быстродействие:

![]()

Преимущественное развитие получили прямоугольные дешифраторы.

Построение дешифраторов на большее число входов

Области применения дешифраторов

Шифраторы

Шифратор (фр. chiffre < ар. цифра):

Шифратор (электроника) — логическое устройство, выполняющее преобразование позиционного кода в n-разрядный двоичный код. Таким образом, шифратор - это комбинационное устройство, реализующее обратную дешифратору функцию.

Шифратор (криптография)

Шифратор (радиотехника) — устройство в системах радионавигации, активной радиолокации и телемеханики

Декадный шифратор имеет 10 входов и 4 выхода. Шифратор предназначен для преобразования десятичных чисел от 0 до 9 в двоичный код. Такой шифратор имеет 10 входов и 4 выхода. Декадный шифратор является неполным так как 2m≠n

Мультиплексоры

Мультиплексор:

Мультиплексор в оптике — устройство в ВОЛС, позволяющее, с помощью пучков света с разными длинами волн и дифракционной решетки (фазовой, амплитудной), передавать по одной коммуникационной линии одновременно несколько различных потоков данных.

Мультиплексор в телекоммуникациях — устройство или программа, позволяющая передавать по одной коммуникационной линии или каналу передачи одновременно несколько различных потоков данных.

Мультиплексор в электронике — компонент, который подключает одну из нескольких входных линий к единичной выходной линии с помощью цифровой команды, называемой адресом.

Демультиплексоры

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DMX или DMS.

Сумматоры

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.[1]

Построение четырехразрядного АЛУ на сумматорах

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление...). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ...). Операции над битами обычно подразумевают сдвиги.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Программируемые логические структуры

Назначение и классификация триггеров

Триггер — электронная логическая схема с положительной обратной связью, имеющая два устойчивых состояния - единичное и нулевое, которые обозначаются соответственно 1 и 0. Такое устройство может сохранять своё состояние теоретически бесконечно долго (при наличии питания). Любой триггер является схемой с памятью или автоматом. Переключение триггера происходит по входному сигналу извне.

Триггеры классифицируют по следующим признакам:

- способу приёма информации;

- принципу построения;

- функциональным возможностям.

По способу синхронизации различают синхронные и асинхронные и смешанные триггерные схемы.

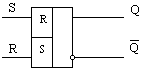

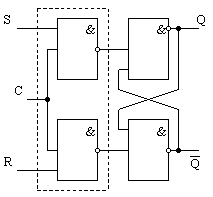

Асинхронный r-s триггер

RS-триггер:

(Асинхронный)

R |

S |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

x |

1 |

1 |

1 |

x |

Алгоритм:

Если R=0 и S=0, то триггер работает в режиме хранения информации: Q n+1=Qn.

Если R=0 и S=1, то на прямом выходе устанавливается в единицу: Q n+1=1.

Если R=1 и S=0, то на прямом выходе устанавливается ноль (режим сброса): Q n+1=0.

Комбинация R=1 и S=1 – запрещенная комбинация и значения триггера на прямом и инверсном выходах не определены.

Оптимизация логических выражений, описывающих работу триггера:

Q n+1

|

R |

|

|

|

S |

x |

x |

1 |

1 |

|

|

|

1 |

|

|

|

Q |

|

|

Логическое уравнение RS-триггера:

![]()

Синхронный R-S триггер

с

(с управлением по входам)

Д – триггер

D-триггер (D от англ. delay — задержка[13][14][15] либо от data[16] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимноинверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

J–K – триггер

K-триггер[18][19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход Kвыходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход Jвыходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[20].

Алгоритм функционирования JK-триггера можно представить формулой

![]()

JK-триггер двухступенчатый со сложной логикой

Счетный триггер

Двухступенчатый триггер

Регистры

Регистры относятся к последовательностным схемам, то есть к схемам с памятью.

Функции регистров:

1) Хранение информации. 2) Прием информации. 3) Выдача информации. 4) Сдвиг информации. 5) Преобразование кодов. 6) Установление в ноль или в единицу нужного числа. 7) Поразрядные логические операции: дизъюнкция, конъюнкция, Сложение по модулю 2.

Счетчики

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Счётчики классифицируют:

по числу устойчивых состояний триггеров

на двоичных триггерах

на троичных триггерах[1]

на n-ичных триггерах

по модулю счёта:

двоично-десятичные (декада);

двоичные;

с произвольным постоянным модулем счёта;

с переменным модулем счёта;

по направлению счёта:

суммирующие;

вычитающие;

реверсивные;

по способу формирования внутренних связей:

с последовательным переносом;

с ускоренным переносом;

с параллельным ускоренным переносом;

со сквозным ускоренным переносом;

с комбинированным переносом;

кольцевые;

по способу переключения триггера:

синхронные;

асинхронные;

Счётчик Джонсона[2]

Двоичный счетчик

Двоичный счётчик, это такое устройство, которое подсчитывает количество приходящих на его вход импульсов. Результат подсчёта выводится в двоичном коде на выходе. Простейшим счётчиком, который считает до двух, является триггер. Чтобы подсчитать бОльшее количество импульсов, нужно использовать бОльшее количество триггеров. Два триггера смогут подсчитать до 4 импульсов, 3 триггера - до 8 импульсов, 4 - до 16 импульсов и так далее.

Двоично-десятичный счетчик

Счетчик в интегральном исполнении (К155 ИЕ6)

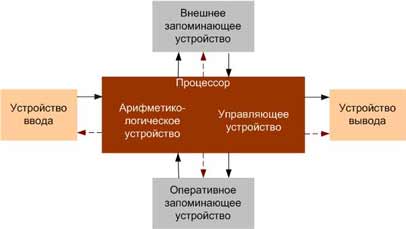

Архитектура построения ЭВМ

Архитектура ЭВМ включает в себя как структуру, отражающую состав ПК, так и программно – математическое обеспечение. Структура ЭВМ - совокупность элементов и связей между ними. Основным принципом построения всех современных ЭВМ является программное управление. Основы учения об архитектуре вычислительных машин были заложены Джон фон Нейманом. Совокупность этих принципов породила классическую (фон-неймановскую) архитектуру ЭВМ. Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и предложил ее структуру, представленную на рисунке.

Организация устройств управления

Внутренняя и внешняя память вычислительных систем

Внутренняя и внешняя память используются существенно различными способами. Внутренняя (оперативная и постоянная) память является хранилищем программного кода, который непосредственно может быть исполнен процессором. В ней же хранятся и данные, также непосредственно доступные процессору (а следовательно, и исполняемой программе). Внешняя память обычно используется для хранения файлов, содержимое которых может быть произвольным. Процессор (программа) имеет доступ к содержимому файлов только опосредованно, через отображение их (полное или частичное) на некоторую область оперативной памяти. Исполнить программный код или обратиться к данным непосредственно на диске процессор не может в принципе. То же относится, естественно, и к ленточной памяти.

Классификация микросхем памяти

Характеристики и режимы работы статических БИС ЗУ

Приведены классификация и справочные данные выпускаемых промышленностью больших интегральных схем запоминающих устройств широкого применения. Проанализированы режимы работы, особенности эксплуатации и даны рекомендации по их применению. Для инженерно-технических работников, связанных с разработкой и применением электронной вычислительной аппаратуры.

Организация статических ЗУ

Организация динамических ЗУ

В них запоминающий элементом является паразитная ёмкость МОП транзистора. Матрица запоминающих элементов - в общем случае это матрица транзисторов. Такая организация обеспечивает считывание целиком строки. Статические ЗУ имеют емкость до 64 Кбит (максимум 256 Кбит). Динамические - 1,4,8 Мбит в одном кристалле.

В отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при этом для хранения одного бита в ДОЗУ нужны всего 1-2 транзистора и накопительный конденсатор (рис). Такие схемы более компактны.