3. Классы процессоров

CISC (complex instruction set computer) есть традиционная архитектура, в которой ЦП использует микропрограммы для выполнения исчерпывающего набора команд. В течение долгих лет производители компьютеров разрабатывали и воплощали в изделиях все более сложные и полные схемы команд. Однако анализ работы процессоров показал, что примерно 80% времени выполняется лишь 20% большего набора команд. Поэтому была поставлена задача оптимизации выполнения небольшого по числу, но часто используемых команд.

RISC (Redused Instuction Set Computer) – архитектура, согласно которой процессор использует сокращенные наборы команд. Так, в процессоре CISC для выполнения одной команды необходимо в большинстве случаев 10 и более тактов. Что же касается процессоров RISC, то они близки к тому, чтобы выполнять по одной команде в каждом такте.

Современные процессоры RISC имеют следующие характеристики:

- упрощенный набор команд, имеющих одинаковую длину;

- большинство команд выполняются за один такт процессора;

- отсутствуют макрокоманды, усложняющие структуру процессора и уменьшающие скорость его работы;

- взаимодействие с оперативной памятью ограничивается операциями пересылки данных;

- уменьшено число способов адресации памяти;

- создан конвейер команд, позволяющий обрабатывать несколько из них одновременно;

- используется высокоскоростная память.

Процессор VLIW (very long instruction word — «очень длинная машинная команда») – процессор, работающий с системой команд сверхбольшой разрядности. Создается специальный компилятор планирования, который перед выполнением прикладной программы проводит ее анализ и по множеству ветвей последовательности операций определяет группу команд, которые могут выполняться параллельно.

VLIW— архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

В суперскалярных процессорах также есть несколько вычислительных модулей, но задача распределения между ними работы решается аппаратно. Это сильно усложняет дизайн процессора, и может быть чревато ошибками. В процессорах VLIW задача распределения решается во время компиляции и в инструкциях явно указано, какое вычислительное устройство должно выполнять какую команду.

VLIW можно считать логическим продолжением идеологии RISC, расширяющей её на архитектуры с несколькими вычислительными модулями. Так же, как в RISC, в инструкции явно указывается, что именно должен делать каждый модуль процессора. Из-за этого длина инструкции может достигать 128 или даже 256 бит.

Пример

Рассмотрим работу модельного VLIW-процессора с двумя арифметическо-логическими устройствами (АЛУ). Пусть нам надо сложить четыре числа, находящиеся в регистрах R1, R2, R3 и R4. Тогда псевдокод может выглядеть так:

R5=R1+R2, R6=R3+R4 ; каждое АЛУ складывает свою пару чисел

R0=R5+R6, NOP ; первое АЛУ находит сумму, второе простаивает

Преимущества и недостатки VLIW

Подход VLIW сильно упрощает архитектуру процессора, перекладывая задачу распределения вычислительных устройств на компилятор. Поскольку отсутствуют большие и сложные узлы, сильно снижается энергопотребление.

В то же время, код для VLIW обладает невысокой плотностью. Из-за большого количества пустых инструкций для простаивающих устройств программы для VLIW-процессоров могут быть гораздо длиннее, чем аналогичные программы для традиционных архитектур.

Архитектура VLIW выглядит довольно экзотической и непривычной для программиста. Из-за сложных внутренних зависимостей кода, программирование на уровне машинных кодов для VLIW-архитектур человеком вручную является достаточно сложным. Приходится полагаться на оптимизацию компилятора.

Реализации VLIW

Одни из первых VLIW-процессоры появились в конце 1980-х и были разработаны компанией Cydrome.[источник не указан 243 дня]

В чистом виде архитектуру VLIW имеют процессоры TriMedia фирмы Philips и семейство DSP C6000 фирмы Texas Instruments.[источник не указан 243 дня]

Микропроцессор Transmeta Crusoe содержит слой двоичной совместимости с архитектурой x86, который компилирует инструкции во внутренний формат процессора (code morphing). Ядро Crusoe является VLIW-процессором.[источник не указан 243 дня]

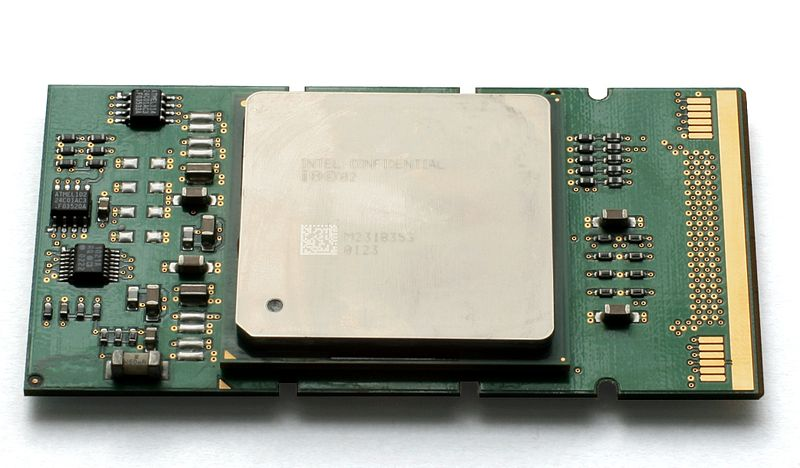

Микропроцессор Intel Itanium имеет 64-битную систему команд «с явным параллелизмом» (англ. explicitly parallel instruction computing, EPIC), которая является одним из вариантов VLIW.

Рис. 1. Процессор Itanium 2 в корпусе PAC — один из представителей VLIW-архитектур.

МВК «Эльбрус-3» и микропроцессоры серии «Эльбрус» («Эльбрус 2000», «Эльбрус S») являются VLIW-процессорами.

Процессоры, выпускаемые фирмой Tilera, также имеют VLIW-архитектуру.

VLIW также получила распространение на рынке GPU, так, видеопроцессоры AMD/ATI Radeon начиная с R600 и до современных имеют VLIW архитектуру. В последнем поколении (Southern Islands) компания AMD/ATI отошла от подхода VLIW.

Процессор MISC – MISC processor – работающий с минимальным набором длинных команд.

Увеличение разрядности процессоров привело к идее укладки нескольких команд в одно слово (связку, bound) размером 128 бит. Оперируя с одним словом, процессор получил возможность обрабатывать сразу несколько команд. Это позволило использовать возросшую производительность компьютера и его возможность обрабатывать одновременно несколько потоков данных.

Векторный процессор - процессор, обеспечивающий параллельное выполнение операции над массивами данных (векторами). Векторный процессор характеризуется специальной архитектурой, построенной на группе параллельно работающих процессорных элементов. Векторный процессор предназначен для обработки изображений, матриц и массивов данных.

Коммуникационный процессор (Фронтальный процессор; Внешний процессор; Препроцессор FEP Front end processor (FEP) - процессор:

- специализирующийся на передаче данных через каналы;

- управляющий группой терминалов; и

- обеспечивающий форматирование и предварительную обработку данных.

Масштабируемая процессорная архитектура (Scalable Processor ARChitecture - SPARC) - разработанная корпорацией Sun 32-разрядная архитектура семейства чипов, базирующаяся на концепции вычислений с сокращенным набором команд (RISC).