- •1.6. Структура памяти и программ

- •Векторы прерываний

- •Загружаемые драйверы

- •Свободная память

- •2. Управление памятью и многозадачной средой в микропроцессорах Intel 80386,80486 и Pentium

- •Дисплей

- •5. Программирование win32

- •6. Архитектура вычислительных систем

- •Гибридная архитектура numa

- •Организация когерентности многоуровневой иерархической памяти

- •Типы кластеров

- •Проблемы выполнения сети связи процессоров в кластерной системе

- •Эволюция средств вычислительной техники

- •2. Управление памятью и многозадачной средой в микропроцессорах Intel 80386,80486 и Pentium

- •4. Современные операционные системы

- •Объектно-ориентированный подход

2. Управление памятью и многозадачной средой в микропроцессорах Intel 80386,80486 и Pentium

Процессоры Intel 80386, 80486 и Pentium с точки зрения рассматриваемых в данном разделе вопросов имеют аналогичные средства, поэтому для краткости в тексте используется термин "процессор i386", хотя вся информация этого раздела в равной степени относится к трем моделям процессоров фирмы Intel.

Процессор i386 имеет два режима работы - реальный (real mode) и защищенный (protected mode). В реальном режиме процессор i386 работает как быстрый процессор 8086 с несколько расширенным набором команд. В защищенном режиме процессор i386 может использовать все механизмы 32-х разрядной организации памяти, в том числе механизмы поддержки виртуальной памяти и механизмы переключения задач. Кроме этого, в защищенном режиме для каждой задачи процессор i386 может эмулировать 86 и 286 процессоры, которые в этом случае называются виртуальными процессорами. Таким образом, при многозадачной работе в защищенном режиме процессор i386 работает как несколько виртуальных процессоров, имеющих общую память. В отличие от реального режима, режим виртуального процессора i86, который называется в этом случае режимом V86, поддерживает страничную организацию памяти и средства многозадачности. Поэтому задачи, выполняющиеся в режиме V86, используют те же средства межзадачной защиты и защиты ОС от пользовательских задач, что и задачи, работающие в защищенном режиме i386. Однако максимальный размер виртуального адресного пространства составляет 1 Мб, как и у процессора i86.

Переключение процессора i386 из реального режима в защищенный и обратно осуществляется просто путем выполнения команды MOV, которая изменяет бит режима в одном из управляющих регистров процессора. Переход процессора в режим V86 происходит похожим образом путем изменения значения определенного бита в другом регистре процессора.

2.1. Программная модель микропроцессоров Intel 80386,80486 и Pentium

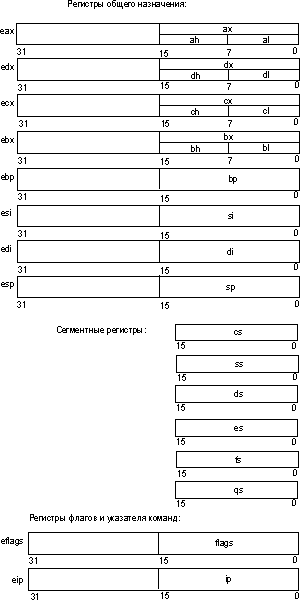

Рассмотрим программную модель микропроцессоров Intel 80386,80486 и Pentium, которая содержит 32 регистра в той или иной мере доступных для использования программистом. Данные регистры можно разделить на две большие группы:

16 пользовательских регистров;

16 системных регистров.

В программах на языке ассемблера регистры используются очень интенсивно. Большинство регистров имеют определенное функциональное назначение. Пользовательские регистры

Как следует из названия, пользовательскими регистры называются потому, что программист может использовать их при написании своих программ. К этим регистрам относятся восемь 32-битных регистров, которые могут использоваться программистами для хранения данных и адресов (их еще называют регистрами общего назначения (РОН)):

eax/ax/ah/al;

ebx/bx/bh/bl;

edx/dx/dh/dl;

ecx/cx/ch/cl;

ebp/bp;

esi/si;

edi/di;

esp/sp.

шесть регистров сегментов: cs, ds, ss, es, fs, gs;

регистры состояния и управления:

регистр флагов eflags/flags;

регистр указателя команды eip/ip.

Рис. 2.1. Пользовательские регистры микропроцессоров i386,i486 и Pentium

Для обеспечения работоспособности программ, написанных для младших 16-разрядных моделей микропроцессоров фирмы Intel, начиная c i8086 регистры можно использоа=вать как 16-ти разрядные.

Регистры общего назначения:

Все регистры этой группы позволяют обращаться к своим “младшим” частям. Заметьте, что использовать для самостоятельной адресации можно только младшие 16 и 8-битные части этих регистров. Старшие 16 бит этих регистров как самостоятельные объекты недоступны. Это сделано, как мы отметили выше, для совместимости с младшими 16-разрядными моделями микропроцессоров фирмы Intel.

Перечислим регистры, относящиеся к группе регистров общего назначения. Так как эти регистры физически находятся в микропроцессоре внутри арифметико-логического устройства (АЛУ), то их еще называют регистрами АЛУ:

eax/ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно;

ebx/bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти;

ecx/cx/ch/cl (Count register) — регистр-счетчик. Применяется в командах, производящих некоторые повторяющиеся действия. Его использование зачастую неявно и скрыто в алгоритме работы соответствующей команды. К примеру, команда организации цикла loop кроме передачи управления команде, находящейся по некоторому адресу, анализирует и уменьшает на единицу значение регистра ecx/cx;

edx/dx/dh/dl (Data register) — регистр данных. Так же, как и регистр eax/ax/ah/al, он хранит промежуточные данные. В екоторых командах его использование обязательно; для некоторых команд это происходит неявно. Следующие два регистра используются для поддержки так называемых цепочечных операций, то есть операций, производящих последовательную обработку цепочек элементов, каждый из которых может иметь длину 32, 16 или 8 бит:

esi/si (Source Index register) — индекс источника. Этот регистр в цепочечных операциях содержит текущий адрес элемента в епочке-источнике;

edi/di (Destination Index register) — индекс приемника (получателя). Этот регистр в цепочечных операциях содержит текущий адрес в цепочке-приемнике. В архитектуре микропроцессора на программно-аппаратном уровне поддерживается такая структура данных, как стек. Для работы со стеком в системе команд микропроцессора есть специальные команды, а в программной модели микропроцессора для этого существуют специальные регистры:

esp/sp (Stack Pointer register) — регистр указателя стека. Содержит указатель вершины стека в текущем сегменте стека.

ebp/bp (Base Pointer register) — регистр указателя базы кадра стека. Предназначен для организации произвольного доступа к данным внутри стека.

Не спешите пугаться столь жесткого функционального назначения регистров АЛУ. На самом деле, большинство из них могут использоваться при программировании для хранения операндов практически в любых сочетаниях. Но, как мы отметили выше, некоторые команды используют фиксированные регистры для выполнения своих действий. Это нужно обязательно учитывать. Использование жесткого закрепления регистров для некоторых команд позволяет более компактно кодировать их машинное представление. Знание этих особенностей позволит вам при необходимости хотя бы на несколько байт сэкономить память, занимаемую кодом программы.

Сегментные регистры.

В программной модели микропроцессора имеется шесть сегментных регистров:

cs, ss, ds, es, gs, fs. Их существование обусловлено спецификой организации и использования оперативной памяти микропроцессорами Intel. Логика обработки машинной команды построена так, что при выборке команды, доступе к данным программы или к стеку неявно используются адреса во вполне определенных сегментных регистрах. Микропроцессор поддерживает следующие типы сегментов:

Сегмент кода. Содержит команды программы. Для доступа к этому сегменту служит регистр cs (code segment register) — сегментный регистр кода. Он содержит адрес сегмента с машинными командами, к которому имеет доступ микропроцессор (то есть эти команды загружаются в конвейер микропроцессора).

Сегмент данных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data segment register) — сегментный регистр данных, который хранит адрес сегмента данных текущей программы.

Сегмент стека. Этот сегмент представляет собой область памяти, называемую стеком. Для доступа к этому сегменту служит регистр ss (stack segment register) — сегментный регистр стека, содержащий адрес сегмента стека.

Дополнительный сегмент данных. Неявно алгоритмы выполнения большинства машинных команд предполагают, что обрабатываемые ими данные расположены в сегменте данных, адрес которого находится в сегментном регистре ds. Если программе недостаточно одного сегмента данных, то она имеет возможность использовать еще три дополнительных сегмента данных. Но в отличие от основного сегмента данных, адрес которого содержится в сегментном регистре ds, при использовании дополнительных сегментов данных их адреса требуется указывать явно с помощью специальных префиксов переопределения сегментов в команде. Адреса дополнительных сегментов данных должны содержаться в регистрах es, gs, fs (extension data segment registers).

Регистры состояния и управления.

В микропроцессор включены несколько регистров, которые постоянно содержат информацию о состоянии как самого микропроцессора, так и программы, команды которой в данный момент загружены на конвейер. К этим регистрам относятся:

Регистр флагов eflags/flags; регистр указателя команды eip/ip.

Используя эти регистры, можно получать информацию о результатах выполнения команд и влиять на состояние самого микропроцессора. Рассмотрим подробнее назначение и содержимое этих регистров:

eflags/flags (flag register) — регистр флагов. Разрядность eflags/flags — 32/16 бит. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть этого регистра полностью аналогична регистру flags для i8086. На рис. 2.3 показано содержимое регистра eflags.

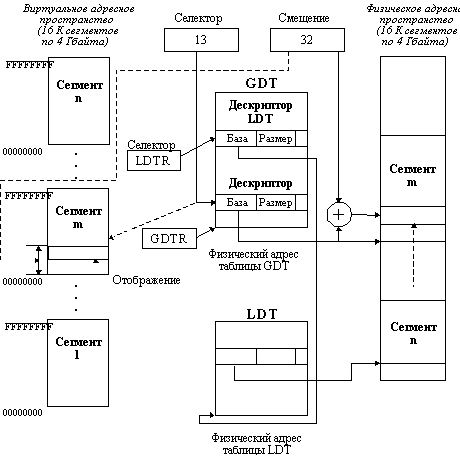

2.2. Средства поддержки сегментации памяти

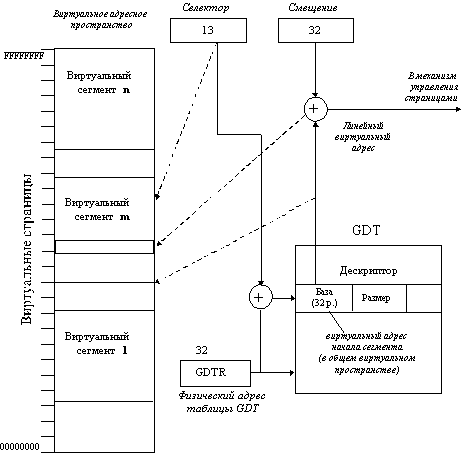

Физическое адресное пространство процессора i386 составляет 4 Гбайта, что определяется 32-разрядной шиной адреса. Физическая память является линейной с адресами от 00000000 до FFFFFFFF в шестнадцатиричном представлении. Виртуальный адрес, используемый в программе, представляет собой пару - номер сегмента и смещение внутри сегмента. Смещение хранится в соответствующем поле команды, а номер сегмента - в одном из шести сегментных регистров процессора (CS, SS, DS, ES, FS или GS), каждый из которых является 16-битным. Средства сегментации образуют верхний уровень средств управления виртуальной памятью процессора i386, а средства страничной организации - нижний уровень.

Средства страничной организации могут быть как включены, так и выключены (за счет установки определенного бита в управляющем регистре процессора), и в зависимости от этого изменяется смысл преобразования виртуального адреса, которое выполняют средства сегментации. Сначала рассмотрим случай работы средств сегментации при отключенном механизме управления страницами. На рисунке 1.7 показано виртуальное адресное пространство процессора i386 при отключенном механизме управления страницами. 32-битное смещение определяет размер виртуального сегмента в 2^32=4 Гбайта, а количество сегментов определяется размером поля, отведенного в сегментном регистре под номер сегмента.

Рис. 2.2. Поддержка сегментов

На рисунке 1. 8, а) показана структура данных в сегментном регистре. Эта структура называется селектором, так как предназначена для выбора дескриптора определенного сегмента из таблиц дескрипторов сегментов. Дескриптор сегмента описывает все характеристики сегмента, необходимые для проверки правильности доступа к нему и нахождения его в физическом адресном пространстве. Процессор i386 поддерживает две таблицы дескрипторов сегментов - глобальную (GlobalDescriptor Table, GDT) и локальную (Local Descriptor Table, LDT). Глобальная таблица предназначена для описания сегментов операционной системы и сегментов межзадачного взаимодействия, то есть сегментов, которые в принципе могут использоваться всеми процессами, а локальная таблица - для сегментов отдельных задач.

Таблица GDT одна, а таблиц LDT должно быть столько, сколько в системе выполняется задач. При этом активной в каждый момент времени может быть только одна из таблиц LDT. Из рисунка 1.8 а) видно, что селектор состоит из трех полей - 13-битного поля индекса (номера сегмента) в таблицах GDT и LDT, 1-битного поля - указателя типа используемой таблицы дескрипторов и двухбитного поля текущих прав доступа задачи - CPL.

Разрядность поля индекса определяет максимальное число глобальных и локальных сегментов задачи - по 8К. (2^13) сегментов каждого типа, всего 16 К. С учетом максимального размера сегмента - 4 Гбайта - каждая задача при чисто сегментной организации виртуальной памяти работает в виртуальном адресном пространстве в 64 Тбайта. Теперь проследим, как виртуальное пространство отображается на физическое пространство размером в 4 Гбайта при чисто сегментном механизме отображения. Итак, когда задаче необходимо получить доступ к ячейке физической памяти, то для выбора дескриптора виртуального сегмента используется значение селектора из соответствующего (в зависимости от команды и стадии ее выполнения - выборка кода команды иди данных) сегментного регистра процессора. Значение поля типа таблицы указывает на то, какую таблицу нужно использовать - GDT или LDT.

Рис. 2.3 Форматы селектора и дескриптора данных и кода

Рассмотрим сначала случай использования таблицы GDT. Для хранения таблиц GDT и LDT используется оперативная память. Для того, чтобы процессор смог найти в физической памяти таблицу GDT, ее полный 32-битный физический адрес (адрес начала таблицы), а также размер (поле в 16 бит) хранятся в специальном регистре процессора GDTR (рисунок 1.8, б). Каждый дескриптор в таблицах GDT и LDT имеет размер 8 байт, поэтому максимальный размер этих таблиц - 64 К (8х8 К дескрипторов). Для извлечения нужного дескриптора из таблицы процессор складывает базовый адрес таблицы GDT из регистра GDTR со сдвинутым на 3 разряда влево (умножение на 8, в соответствии с числом байтов в элементе таблицы GDT) значением поля индекса из сегментного регистра и получает физический линейный адрес нужного дескриптора в физической памяти. Таблица GDT постоянно присутствует в физической памяти, поэтому процессор извлекает по этому адресу нужный дескриптор сегмента и помещает его во внутренний (программно недоступный) регистр процессора. (Таких регистров шесть и каждый из них соответствует определенному сегментному регистру, что значительно ускоряет работу процессора).

Дескриптор виртуального сегмента (рисунок 1.8 в) состоит из нескольких полей, основными из которых являются поле базы - базового 32-разрядного физического адреса начала сегмента, поле размера сегмента и поле прав доступа к сегменту - DPL (Descriptor Privilege Level). Сначала процессор определяет правильность адреса, сравнивая смещение и размер сегмента (в случае выхода за границы сегмента происходит прерывание типа исключение - exception). Потом процессор проверяет права доступа задачи к данному сегменту, сравнивая значения полей CPL селектора и DPL дескриптора сегмента. В процессоре i386 мандатный способ определения прав доступа (называемый также механизмом колец защиты), при котором имеется несколько уровней прав доступа, и объекты какого-либо уровня имеют доступ ко всем объектам равного уровня или более низких уровней, но не имеет доступа к объектам более высоких уровней. В процессоре i386 существует четыре уровня прав доступа - от 0-го, который является самым высоким, до 3-го - самого низкого. Очевидно, что операционная система может использовать механизм уровней защиты по своему усмотрению. Однако предполагается, что нулевой уровень будет использован для ядра операционной системы, а третий уровень - для прикладных программ, промежуточные уровни - для утилит и подсистем операционной системы, менее привилегированных, чем ядро.

Таким образом, доступ к виртуальному сегменту считается законным, если уровень прав селектора CPL выше или равен уровню прав сегмента DPL (CPL <= DPL). При нарушении прав доступа происходит прерывание, как и в случае несоблюдения границ сегмента. Далее проверяется наличие сегмента в физической памяти по значению бита Р дескриптора, и если сегмент отсутствует в физической памяти, то происходит прерывание. При наличии сегмента в памяти вычисляется физический линейный адрес путем сложения базы сегмента и смещения и производится доступ к элементу физической памяти по этому адресу.

В случае, когда селектор указывает на таблицу LDT, виртуальный адрес преобразуется в физический аналогичным образом, но для доступа к самой таблице LDT добавляется еще один этап, так как в процессоре регистр LDTR указывает на размещение таблицы LDT не прямо, а косвенно. Сам регистр LDTR имеет размер 16 бит и содержит селектор дескриптора таблицы GDT, который описывает расположение этой таблицы в физической памяти. Поэтому при доступе к элементу физической памяти через таблицу LDT происходит дву-

кратное преобразование виртуального адреса в физический, причем оба раза по описанной выше схеме. Сначала по значению селектора LDTR определяется физический адрес дескриптора из таблицы GDT, описывающего начало расположения таблицы LDT в физической памяти, а затем с по- мощью селектора задачи вычисляется смещение к таблице LDT и определяется физический адрес нужного дескриптора. Далее процесс аналогичен преобразованию виртуального адреса с помощью таблицы GDT.

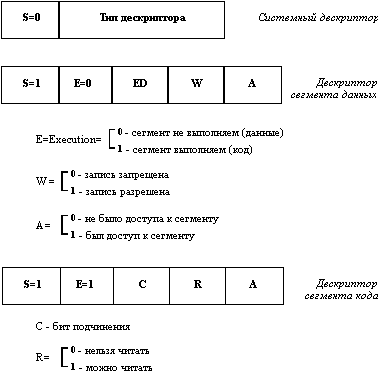

Рис. 1.9. Типы дескрипторов

Д ескриптор

сегмента содержит еще несколько полей.

Однобитное поле G

определяет единицу измерения размера

сегмента, при G=0

размер определяется в байтах, и тогда

сегмент не может быть больше 64 К, а при

G

=

1 размер определяется в 4Кбайтных

страницах, при этом максимальный размер

сегмента достигает указанных 4 Гбайт.

Поле D

определяет тип адресации сегмента: при

D

= О сегмент является 16-битным (для режима

эмуляции 16-битных процессоров i86

и i286),

а при D

= 1 сегмент является 32-битным. Кроме

этого в дескрипторе имеется поле типа

сегмента, которое в свою очередь делится

на несколько полей (рисунок 1.9). Поле S

определяет, является ли сегмент

системным (S

=

1) или пользовательским (S

= 0). В свою очередь пользовательские

сегменты делятся на сегменты данных

(Е=0) и сегменты кода (Е=1). Для сегмента

данных определяются однобитные поля:

ескриптор

сегмента содержит еще несколько полей.

Однобитное поле G

определяет единицу измерения размера

сегмента, при G=0

размер определяется в байтах, и тогда

сегмент не может быть больше 64 К, а при

G

=

1 размер определяется в 4Кбайтных

страницах, при этом максимальный размер

сегмента достигает указанных 4 Гбайт.

Поле D

определяет тип адресации сегмента: при

D

= О сегмент является 16-битным (для режима

эмуляции 16-битных процессоров i86

и i286),

а при D

= 1 сегмент является 32-битным. Кроме

этого в дескрипторе имеется поле типа

сегмента, которое в свою очередь делится

на несколько полей (рисунок 1.9). Поле S

определяет, является ли сегмент

системным (S

=

1) или пользовательским (S

= 0). В свою очередь пользовательские

сегменты делятся на сегменты данных

(Е=0) и сегменты кода (Е=1). Для сегмента

данных определяются однобитные поля:

ED - направления распространения сегмента (ED = 0 для обычного сегмента данных, распространяющегося в сторону увеличения адресов, ED = 1 для стекового сегмента данных, распространяющегося в сторону уменьшения адресов),

W - поле разрешения записи в сегмент (при W=1 запись разрешена, при W=0 -запрещена),

А - поле доступа к сегменту (1 означает, что после очистки этого поля к сегменту было обращение по чтению или записи, это поле может использоваться операционной системой в ее стратегии замены страниц в оперативной памяти).

Для сегмента кода используются однобитные признаки:

А - имеет смысл, аналогичный полю А сегмента данных, R - разрешает или запрещает чтение из кодового сегмента,

С - бит подчинения, разрешает или запрещает вызов данного кодового сегмента из другого кодового сегмента с более низкими правами доступа.

В процессоре i386 существует большое количество системных сегментов, к которым в частности относятся системные сегменты типа LDT, шлюзы вызова подпрограмм и задач и сегменты состояния задачи TSS.

Таким образом, для использования чисто сегментного механизма процессора i386 операционной системе необходимо сформировать таблицы GUT и LDT, загрузить их в память (для начала достаточно загрузить только таблицу GDT), загрузить указатели на эти таблицы в регистры GDTR и LDTR и выключить страничную поддержку. Если же операционная система не хочет использовать сегментную организацию виртуальной памяти, то ей достаточно создать таблицу дескрипторов из одного входа (дескриптора) и загрузить базовые значения сегмента в дескриптор. Виртуальное адресное пространство задачи будет состоять из одного сегмента длиной максимум в 4 Гбайта.

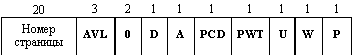

2.3. Сегментно-страничный механизм

При включенной системе управления страницами работает как описанный выше сегментный механизм, так и механизм управления страницами, однако при этом смысл работы сегментного механизма меняется. В этом случае виртуальное адресное пространство задачи имеет размер в 4 Гбайта, в котором размещаются все сегменты (рисунок 5.4). По прежнему селектор задачи определяет номер виртуального сегмента, а смещение в команде задачи - смещение внутри этого сегмента. Так как теперь все сегменты разделяют одно адресное пространство, то возможно их наложение, по процессор не контролирует такие ситуации, оставляя эту проблему операционной системе. Первый этап преобразования виртуального адреса, связанный с преобразованием смещения и селектора с использованием таблиц GDT и LDT, содержащих дескрипторы сегментов, в точности совпадает с этапом преобразования этих данных при отключенном механизме управления страницами. Все структуры данных этих таблиц такие же. Однако, если раньше дескриптор сегмента содержал его базовый адрес в физическом адресном пространстве, и при сложении его со смещением из команды программы получался линейный искомый адрес в физической памяти, то теперь дескриптор содержит базовый адрес сегмента в виртуальном адресном пространстве. Поэтому в результате его сложения со смещением получается линейный виртуальный адрес, который на втором этапе (страничном) преобразуется в номер физической страницы. Для реализации механизма управления страницами как физическое, так и виртуальное адресное пространства, разбиты на страницы размером 4 К. Всего в этих адресных пространствах насчитывается 1 М страниц. Несмотря на наличие нескольких виртуальных сегментов, все виртуальное адресное пространство задачи имеет общее разбиение на страницы, так что нумерация виртуальных страниц сквозная. Линейный виртуальный адрес содержит в своих старших 20 разрядах номер виртуальной страницы, а в младших 12 разрядах смещение внутри страницы. Для отображения виртуальной страницы в физическую достаточно построить таблицу страниц, каждый элемент которой (дескриптор виртуальной стр.) содержал бы номер соответствующей ей физической страницы и ее атрибуты. В процессоре i386 так и сделано, и структура дескриптора страницы показана на рисунке (1.11.) 20-ти разрядов номера страницы достаточно для определения физического адреса начала страницы, так как при её фиксированном размере 4 К младшие 12 разрядив этого адреса всегда равны нулю. Дескриптор страницы также содержит следующие поля, близкие по смыслу соответствующим полям дескриптора сегмента :

Р - бит присутствия страницы в физической памяти,

W - бит разрешения записи в страницу,

U - бит пользователь/супервизор

А - признак того, был ли доступ к странице,

D - признак модификации содержимого страницы,

PWT и PCD - управляют механизмом кэширования страниц (введены, начиная с процессора i486),

AVL - резерв для нужд операционной системы (available for use).

Рис. 2.5. Сегментно – страничный механизм

Рис. 2.6. Формат дескриптора страницы

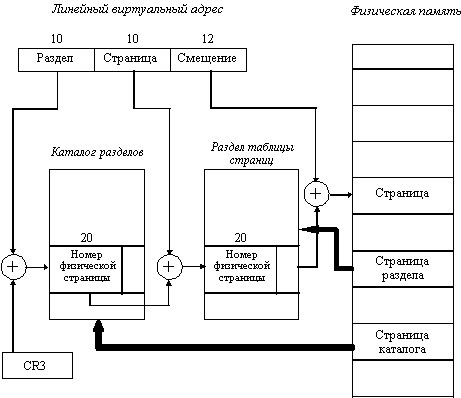

При небольшом размере страницы процессора i386 относительно размеров адресных пространств, таблица страниц должна занимать в памяти весьма значительное место - 4 байта х 1М = 4 Мбайта. Это слишком много для нынешних моделей персональных компьютеров, поэтому в процессоре i386 используется деление всей таблицы страниц на разделы по 1024 дескриптора. Размер раздела выбран так, чтобы один раздел занимал одну физическую страницу (1024 х 4 байта = 4 Кбайта). Всего получается 1024 раздела (1024 х 1024 = 1М). Для того, чтобы не хранить все разделы таблицы страниц одновременно в физической памяти, используется катало! разделов таблицы страниц, который использует такие же по структуре дескрипторы страниц, что и в таблице страниц. Поэтому для хранения информации о дескрипторах 1024 разделов необходима память 4 К, т.е. одна физическая страница. Совокупность дескрипторов, описывающих состояние и характеристики виртуальных страниц разделов таблицы страниц, называется каталогом разделов или таблиц. Виртуальная страница, хранящая содержимое каталога, всегда находится в физической памяти, и номер ее физической страницы указан в специальном управляющем регистре CR3 процессора (точнее, в одном из полей этого регистра).

Преобразование линейного виртуального адреса в физический происходит следующим образом (рисунок 1.12). Поле номера виртуальной страницы (старшие 20 разрядов) делится на две равные части по 10 разрядов - поле номера раздела и поле номера страницы в разделе. С помощью номера физической страницы, хранящей каталог и смещения в этой странице, задаваемого полем номера раздела, процессор находит дескриптор виртуальной страницы раздела. В соответствии с атрибутами этого дескриптора определяются права доступа к этой странице, а также наличие ее в физической памяти. В случае ее отсутствия происходит страничное прерывание, и операционная система должна в этом случае переместить ее в память. После того, как нужная страница находится в памяти, для определения адреса элемента данных используется смещение, определяемое полем номера страницы линейного виртуального адреса.

Таким

образом, при доступе к странице в

процессоре используется двухуровневая

схема адресации страниц, что замедляет

преобразование, но позволяет использовать

страничный механизм и для хранения

самой таблицы страниц, и существенно

уменьшить объем физической памяти

для ее хранения. Для ускорения страничных

преобразований в блоке управления

страницами используется ассоциативная

память, в которой кэшируется 32 комбинации

"номер виртуальной страницы - номер

физической страницы".

Рис 2. 7. Преобразование линейного виртуального адреса

в физический адрес

Эта специальная кэш-память (дополнительная по отношению к 8 Кбайтному кэшу данных процессоров i486 и Pentium) значительно ускоряет преобразование адресов, так как в случае попадания в кэш длительный процесс, описанный выше, исключается.

Организация виртуальной памяти в процессоре i386 позволяет защитить адресный пространства различных процессов за счет двух механизмов:

1) Изоляции адресных пространств процессов в физической памяти за счет назначения им различных физических страниц или сегментов (если страничный механизм отключен).

2) Защита сегментов от несанкционированного доступа с помощью привилегий четырех уровней.

Эволюция процессоров INTEL

На сегодняшний день наибольший интерес представляют процессоры пятого, шестого и седьмого поколений, границы между которыми несколько размыты. Появившийся в 1993 году процессор Pentium ознаменовал собой новый этап в развитии архитектуры x86, связанный с адаптацией многих свойств процессоров с архитектурой RISC. Именно с процессоров Pentium фирмы Intel началось пятое поколение процессоров семейства x86. Он изготовлен по 0.8-микронной КМОП технологии и содержит 3.1 миллиона транзисторов. Первоначальная реализация была рассчитана на работу с тактовой частотой 60 и 66 МГц. Затем были выпущены процессоры, работающие с тактовой частотой 75, 90, 100, 120, 133, 150 и 200 МГц. По базовой регистровой архитектуре и системе команд процессоры Pentium являются 32-разрядными процессорами, но имеют 64-битную шину данных, шина адреса позволяет адресовать 4 Гбайт физической памяти. Процессор Pentium по сравнению со своими предшественниками обладает целым рядом улучшенных характеристик. Главными его особенностями являются:

двухпотоковая суперскалярная организация, допускающая параллельное выполнение пары простых команд;

наличие двух независимых двухканальных множественно-ассоциативных кэшей для команд и для данных, обеспечивающих выборку данных для двух операций в каждом такте;

динамическое прогнозирование переходов;

конвейерная организация устройства плавающей точки с 8 ступенями;

двоичная совместимость с существующими процессорами семейства 80x86.

Прежде всего новая микроархитектура процессора Pentium базируется на идее суперскалярной обработки (правда с некоторыми ограничениями). Основные команды распределяются по двум независимым исполнительным устройствам (конвейерам U и V). Конвейер U может выполнять любые команды семейства x86, включая целочисленные команды и команды с плавающей точкой. Конвейер V предназначен для выполнения простых целочисленных команд и некоторых команд с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, причем при выдаче устройством управления в одном такте пары команд более сложная команда поступает в конвейер U, а менее сложная - в конвейер V. Такая попарная выдача команд возможна правда только для ограниченного подмножества целочисленных команд. Команды арифметики с плавающей точкой не могут запускаться в паре с целочисленными командами. Одновременная выдача двух команд возможна только при отсутствии зависимостей по регистрам.

По интерфейсу шина процессора Pentium стала развитием шины процессора i486. Если шина i486 ориентирована на максимальную гибкость и простоту подключения устройств с различной разрядностью, то шина Pentium - на достижение максимальной производительности. Интерфейс рассчитан на применение внешнего вторичного кэша и внутреннего первичного с возможностью работы как со сквозной (write-through), так и с обратной (write-back) записью. Интерфейс позволяет объединять до 2 процессоров на одной шине для реализации SMP (симметричные мультипроцессорные системы) или FRC (системы с избыточным контролем функциональности).

Процессор Pentium MMX - последний из процессоров пятого поколения Pentium. Он дополнен расширением MMX, ориентированное на приложения мультимедиа, 2D/3D-графику и коммуникации, (основная идея заключается в одновременной обработке нескольких элементов данных за одну инструкцию), и ряд усовершенствований, повышающих производительность на обычных операциях.

К шестому поколению процессоров Intel относятся Pentium Pro, все разновидности процессоров Pentium II/III, а также Celeron. Процессоры этого поколения имеют обобщенное название P6. С точки зрения принципа организации вычислений, главное отличие этого поколения заключается в динамическом исполнении, при котором внутри процессора инструкции могут исполняться не в том порядке, который предполагает программный код. Это решение призвано повысить производительность процессора за счет улучшения архитектуры, а не повышения тактовой частоты. Динамическое исполнение резко повышает частоту запросов процессорного ядра к шине за данными и инструкциями, поскольку ядро одновременно обрабатывает несколько инструкций. Для обхода узкого места - внешней шины - в P6 применена архитектура двойной независимой шины DIB (Dual Independent Bus), реализующая, по сути, две отдельные шины. Одна из этих шин используется только для связи с кристаллом вторичного кэша, расположенным в том же корпусе микросхемы, что и процессор(Работает на частоте ядра). Вторая шина процессорного кристалла выходит на внешние выводы микросхемы, она и является системной, или "фасадной" шиной FSB (Front-Side Bus) процессора Р6. Эта шина работает на внешней частоте независимо от внутренней шины.

Процессоры Pentium Pro появились в 1995 году, выполнялись по технологии 0,5 мкм, впоследствии 0,35 мкм. Они выпускались с частотами ядра 150, 166, 180 и 200 МГц и объемом вторичного кэша 256 и 512 Кбайт (1024 Кбайт в специальных моделях). Раздельный первичный кэш инструкций и данных имеет объем 8+8 Кбайт. Вторичный кэш работает на частоте ядре. Частота системной шины - 60 или 66 МГц. Достоверность данных вторичного кэша в некоторых модификациях контролируется с помощью ЕСС. Процессоры могут работать в симметричных мультипроцессорных системах (SMP) - до четырех процессоров на общей шине. Объединяемые процессоры должны иметь одинаковые коэффициенты умножения частоты и единые тактовые частоты шин. Для этих процессоров был введен сокет 8.

Процессоры Pentium II сочетают архитектуру Pentium Pro с технологией MMX. По сравнению с Pentium Pro удвоен размер первичного кэша (16+16 Кбайт), размер вторичного кэша варьируется от 0,5 до 2 Мбайт. В процессоре используется новая технология корпусов - картридж с печатным краевым разъемом, на который выведена системная шина (Single Edge Contact Cartridge - SECC). На картридже размером 14х6,2х1,6см установлена микросхема ядра процессора (CPU Core), несколько микросхем, реализующих вторичный кэш, и вспомогательные дискретные элементы (резисторы и конденсаторы). Снятие вторичного кэша с микросхемы процессора позволяет использовать для кэш-памяти сторонних производителей, специализирующихся на выпуске сверхбыстродействующей памяти. Объем вторичного кэша определяется емкостью и числом установленных микросхем памяти. В то же время сохраняется независимость шины вторичной кэш-памяти, которая тесно связана с ядром процессора собственной локальной шиной.

Первые процессоры Pentium II (до выпуска имели кодовое название Klamath), появившиеся весной 1997 года, насчитывали около 7,5 млн транзисторов только в процессорном ядре и выполнялись по технологии 0,35 мкм, питание 2,8 В. Они имели тактовые частоты ядра 233, 266 и 300 МГц при частоте системной шины 66,6 МГц. При этом вторичный кэш работал на половине частоты ядра и кэшировал только первые 512 Мбайт оперативной памяти. Для этих процессоров был разработан слот 1, по составу сигналов сильно напоминающий сокет 8 для Pentium Pro. Однако слот 1 позволяет объединять только пару процессоров для реализации симметричной мультипроцессорной системы либо системы с избыточным контролем функциональности. Таким образом, этот процессор представляет собой более быстрый Pentium Pro с поддержкой MMX, но урезанными возвожностями построения мультипроцессорных систем.

Следующее поколение Pentium II, имевшие кодовое название Deshutes, появилось в 1998 году и выполнялось уже по технологии 0,25 мкм, питание 2,0 В. Это позволило поднять тактовую частоту, так как чем мельче элементы, тем меньше они рассеивают мощность, что особенно критично на высоких частотах. Процессор на 333 МГц имеет частоту шины 66,6 МГц, а процессоры на 350, 400 и 450 МГц уже имеют частоту системной шины 100 МГц. Для работы на такой частоте эффективна оперативная память на микросхемах SDRAM (синхронная динамическая память). Эти процессоры также устанавливаются в слот 1 и опять-таки не более двух в системе. Начиная с процессоров 350 МГц, объем памяти, кэшируемой на L2, увеличили до 4 Гбайт.

Процессоры Pentium III появились в 1999 году и являются дальнейшим развитием Pentium II. Кодовое название до выхода - Katmai. Их главное отличие - раширение набора SIMD-инструкций SSE (Streaming SIMD Extensions, другое название - KNI - Katmai New Insructions), основанное на новом блоке 128-разрядных регистров ХММ. Этот блок позволяет одной инструкцией выполнять операции сразу над четырьмя комплектами 32-разрядных операндов в формате с плавающей точкой (одинарная точность). При выполнении новых инструкций оборудование традиционного FPU/MMX не используется, что позволяет эффективно смешивать инструкции ММХ с инструкциями над операндами с плавающей точкой. Инструкции с регистрами ММХ могут работать и в скалярном режиме (с одним комплектом операндов). Кроме арифметических, есть и логические инструкции. Появились и новые возможности управления кэшированием. По возможностям мультипроцессорных конфигураций эти процессоры аналогичны своим предшественникам Pentium II и Pentium II Xeon. Возможность избыточных конфигураций есть только у Pentium III Xeon. Частота ядра начинается с 500 МГц, частота системной шины - 100 и 133 МГц. Вторичный кэш в первых моделях Pentium III - 512 Кбайт с ЕСС-контролем - работает на половине частоты ядра, расположен на картридже в виде отдельных микросхем .

Процессоры с ядром Coppermine тоже называются Pentium III. Несмотря на слово copper (Cu - медь) в названии, медные проводники в них не используются. Технология 0,18 мкм, 28 млн транзисторов, площадь кристалла 106 мм². Первичный кэш 32 Кбайт (16+16), на кристалле ядра расположен улучшенный вторичный кэш (Advanced Transfer Cache) размером 256 Кбайт с ЕСС-контролем, который работает на частоте ядра. Вторичный кэш связан с ядром шиной разрядностью 256 бит (у предыдущих Р6 с отдельно расположенным кэшем и процессоров Celeron с интегрированным кэшем разрядность шины данных кэша составляла 64 бит). По сравнению с Celeron и первыми моделями Pentium III, вторичный кэш Coppermine имеет меньшую латентность (задержку от запроса до начала пересылки данных), а пропускная способность его шины выросла в 4 раза. Набор инструкций включает SSE и выдачу серийного номера процессора. Частота системной шины 100 и 133 МГц. Коэффициенты умножения фиксированы изготовителем. Анонсированы модели с частотами 500 (100х5), 533 (133х4), 550 (100х5,5), 600 (100х6 или 133х4,5), 650 (100х6,5), 667 (133х5), 700 (100х7), 733 (133х5,5), 750 (100х7,5), 800, 850, 866, 933, 1000 МГц. В обозначении процессора, например Pentium III-533ЕВ, буква Е означает улучшенный кэш, буква В - частоту шины 133 МГц (без буквы В - 100 МГц).

Летом 1998 года вышла модель Celeron, известная также под названием Mendocino. Сюда относятся процессоры Celeron 300А (с частотой 300 МГц) и Celeron 333-533 МГц. Процессоры имеют небольшой (128 Кбайт) вторичный кэш, установленный на кристалле ядра и работающий на полной частоте ядра (как у Pentium Pro, но несколько с большой латентностью). Процессоры с частотами 300-433 МГц выпускались под слот 1 по технологии 0,25 мкм, питание 2,0 В.

Весной 2000 года появились процессоры Celeron на ядре Coppermine (технология 0,18 мкм, питание 1,5 В). Как и у всех последних процессоров подсемейства Celeron, вторичный кэш имеет размер 128 Кбайт, а частота шины равна 66 МГц. Главное отличие - поддержка инструкций SSE. Частота ядра - начиная с 533 МГц (Celeron 533А). Начиная с частоты 800 МГц поднята частота шины до 100 МГц.

Кроме широко известных особенностей вторичного кэша (либо его нет, либо есть размером 128 Кбайт), процессор Celeron от Pentium II имеет следующие отличия:

разрядность шины адреса сокращена с 36 до 32 бит (адресуемая память - 4 Гбайт);

контроль паритета шины адреса и шины запроса, ЕСС-контроль шины данных и контроль неисправимых ошибок шины отсутствует, как и сигнал инициализации шины;

процессоры предназначены только для одиночных конфигураций: из сигналов запросов шины официально остался только BR0#, что не позволяет реализовать симметричные двухпроцессорные конфигурации. Реально сигнал BR1# в некоторых моделях присутствует, что позволяет использовать Celeron в двухпроцессорных SMP-системах;

коэффициенты умножения частоты фиксированы. Внешняя частота - 66 МГц.

Для мощных компьютеров (серверов) предназначено семейство Xeon - "утяжеленные" варианты процессоров Pentium II и Pentium III. Для них ввели новый слот 2, который (вместе с интерфейсом процессора) позволяет строить как избыточные системы с FRC, так и симметричные 1-, 2-, 4- и даже 8-процессорные системы. Вторичный кэш, как и в Pentium Pro, работает на частоте ядра. Объем вторичного кэша - 512 Кбайт, 1 или 2 Мбайт при кэшировании до 64 Гбайт (все адресное пространство при 36-битной адресации). Процессоры Xeon отличаются не только большей мощностью, но и большими размерами - 15,2х12,7х1,9 см.

Процессоры Xeon имеют новые средства хранения системной информации. Постоянная (только для чтения) память процессорной информации PIROM (Processor Information ROM) хранит такие данные, как электрические спецификации ядра процессора и кэш-памяти (диапазоны частот и питающих напряжений), S-спецификацию и серийный 64-битный номер процессора. Энергозависимая память Scratch EEPROM предназначена для занесения системной инфомации поставщиком процессора (или компьютера с этим процессором) и может быть защищена от последующей записи. Процессор оборудован термодатчиком (термодиод на кристалле ядра) с программируемым устройством контроля температуры. Это устройство имеет аналого-цифровой преобразователь, калибруемый по термодиоду конкретного процессора на этапе тестирования картриджа. Константа настройки термометра заносится в PIROM. Устройство термоконтроля программируется - задается частота преобразования и пороги температуры, по достижении которых вырабатывается сигнал прерывания. Для взаимодействия с PIROM, Scratch EEPROM и устройством термоконтроля процессор имеет дополнительную последовательную шину SMBus (System Management Bus).

Процессоры Pentium II Xeon на ядре Deshutes (технология 0,25 мкм) имеют частоту шины 100 МГц, частота ядра - 400-500 МГц. Набор инструкций - Р6+ММХ.

Процессоры Pentium III Xeon под кодовым названием Tanner (технология 0,25 мкм) имеют частоту шины 100 МГц, частота ядра - от 500 МГц. Вторичный кэш - 512 Кбайт, 1 или 2 Мбайт (для 550 МГц только 512 Кбайт), кэш работает на частоте ядра. Набор инструкций - Р6+ММХ+SSE. Этот процессор позиционируется как серверный (поддерживает 4/8 процессорные кофигурации SMP).

Процессоры Pentium III Xeon под кодовым названием Cascades (технология 0,18 мкм) имеют частоту шины 133 МГц, частота ядра - от 600 МГц. Вторичный кэш - 256 Кбайт, расположен на кристалле ядра, работает на частоте ядра. Первые модели работают только в двухпроцессорных конфигурациях. Вышли системы с вторичным кэш до 2 Мбайт и более высокими частотами (Ю866 МГц). Эти процессоры позиционируются для мощных рабочих станций.

Мобильные процессоры семейства Р6 предназначены для установки в блокнотные персональные компьютеры и другие малогабаритные системы с автономным питанием. Эти процессоры выпускаются в нескольких конструктивных исполнениях: миниатюрный корпус BGA1 и BGA2 с выводами для припаивания, Micro-PGA2 со штырьковыми выводами, мини-картридж с 240-штырьковым разъемом и модули с коннекторами MMC-1 и MMC-2. В этих исполнениях могут быть процессоры четырех типов: мобильный Pentium III, мобильный Pentium II с внешним вторичным кэшем, мобильный Celeron с кэшем 128 Кбайт и мобильный Pentium II со встроенным кэшем 256 Кбайт. Мобильные процессоры имеют ряд отличий от обычных Pentium II/III:

не поддерживается функционально-избыточный контроль (FRC) и двухпроцессорные конфигурации;

понижено напряжение питания, на некоторых процессорах напряжение питания ядра уже ниже 1 В;

понижена нагрузочная способность интерфейсных схем;

введено новое состояние пониженного потребления Quick Start, которое отличается от состояния Stop Grant тем, что в нем не отслеживаются транзакции симметричных агентов (другого процессора), слежение ведется только за приоритетными агентами шины, поэтому потребление в состоянии Quick Start существенно меньше, чем Stop Grant.

Процессор Pentium 4 является 32-разрядным представителем семейства х86, по микроархитектуре принадлежащей к новому, седьмому (по классификации Intel) поколению. С программной точки зрения он представляет собой процессор х86 с очередным расширением системы команд - SSE2. По набору программно-доступных регистров Pentium 4 повторяет процессор Pentium III. С внешней аппаратной точки зрения это процессор с системной шиной нового типа, в которой кроме повышения тактовой частоты применили ставшие уже привычными принципы двойной (2х) и четырехкратной (4х) синхронизации, а также предпринят ряд мер по обеспечению работоспособности на ранее немыслимых частотах. Микроархитектура процессора, получившая название NetBurst, разработана с учетом высоких частот как ядра (1,4 ГГц), так и системной шины (400 МГц). Название микроархитектуры указывает на сетевую направленность процессора - его мощь необходима для ресурсоемких мультимедийных Интернет-приложений. Расширение системы команд ориентировано на задачи, которые становятся доступными для обычных настольных компьютеров:

потоковые приложения, включая обработку видеоинформации в реальном времени, подразумевающую как декодирование сжатой информации, так и более сложные задачи кодирования;

редактирование видеоизображений;

трехмерная визуализация;

обработка видеосигнала в качестве источника данных;

связь с телевидением высокой четкости (HDTV);

распознавание речи;

Интернет-телефония.

Процессор Pentium 4 является по-настоящему однокристальным. На одном кристалле размещено около 42 млн транзисторов, выполненных по технологии с разрешением 0,18 мкм (в Pentium III Coppermine всего 28 млн транзисторов). Частота ядра первых моделей составляет 1,4 или 1,5 ГГц. Процессор кроме собственно вычислительного ядра имеет кэш-память двух уровней. Вторичный кэш, общий для инструкций и данных, имеет размер 256 Кбайт и разрядность шины 256 бита (32 байта), как и в последних процессорах Pentium III. Шина вторичного кэша работает на частоте ядра, что обеспечивает ее пропускную способность 32х1,4=44,8 Гбайт/сек на частоте 1,4 ГГц. Вторичный кэш имеет ЕСС-контроль, позволяющий обнаруживать и исправлять ошибки. Первичный кэш данных имеет такую же высокую пропускную способность (44,8 Гбайт/сек), но его объем сократился вдвое (8 Кбайт против 16 в Pentium III). Первичный кэш инструкций в привычном понимании отсутствует, его заменил кэш трассы (trace cache). В нем хранятся последовательности микроопераций, в которые декодированы инструкции. В этом кэше могут помещаться до 12К микроинструкций.

Интерфейс системной шины процессора рассчитан только на однопроцессорные конфигурации, отсутствует также возможность избыточного функционального контроля (FRC). Интерфейс во многом напоминает шину Р6 - протокол также ориентирован на одновременное выполнение нескольких транзакций. Принят ряд мер по обеспечению высокой пропускной способности. В первых процессорах Pentium 4 частота шины 400 - 800 МГц с "четырехкратной накачкой" (quad pumped) - тактовая частота системной шины составляет 100-200 МГц, но частота передачи адресов и данных выше.

Разрядность шины данных, как и в предыдущих двух поколениях процессоров, составляет 64 бита (8 байт), что в режиме 4х-кратной передачи дает максимальную пропускную способность (100-200)х4х8=3,2 Гбайт/сек. У процессоров Pentium III шина обеспечивала 133х8=1,06 Гбайт/сек, так что по этому параметру у Pentium 4 улучшение троекратное. Шина адреса имеет разрядность 36 бит, что позволяет адресовать те же 64 Гбайт памяти, из которых кэшируются только первые 4 Гбайт.

Внешний вид самого процессора вполне обычный, но он требует радиатора выдающегося размера и веса. Такой радиатор уже не повесить на корпус процесссора, и поэтому требуются специальные крепежные стойки, проходящие через системную плату и крепящиеся к металлическому шасси. Сверху кристалл покрыт металлической крышкой, к которой должен прилегать радиатор. Процессор требует мощного охлаждения - при напряжении питания 1,6 В он потребляет ток до 40,6 А (1,4 ГГц) или 43 А (1,5 ГГц), что соответствует рассеиваемой мощности 65-70 Вт. В режиме пониженного потребления (состояние stop grant) процессор потребляет 8,5 А, а в состоянии "глубого сна" (deep sleep) - 6,6 А. Но кроме того, что эту мощность нужно отводить от процессора и из корпуса компьютера, ее еще нужно получить от блока питания, который для нового процессора должен иметь мощность большую, чем привычные 250 Вт. Предельно допустимая температура корпуса - 70°С.

Как и предыдущие, Pentium 4 имеет встроенные срества термоконтроля, но с новыми функциями. Встроенные цепи термоконтроля TCC (Thermal Control Circuit) модулируют внутреннюю частоту синхронизации для снижения рассеиваемой мощности (и производительности). Предусмотрены два режима - автоматический, при котором ТСС включается, когда температура процессора подходит к критической, и программируемый. Схема термоконтроля управляется через регистры MSR. От BIOS требуется, чтобы по умолчанию был разрешен автоматический термоконтроль.

Микроархитектура NetBurst имеет максимальную производительность исполнения предсказуемых (линейных и циклических) участков программы, характерных для приложений, на которые ориентирован новый процессор. На непредсказуемо ветвящихся программах, к которым относятся, например, офисные приложения, длинный гиперконвейер оказывается менее эффективным, чем конвейер Р6, если бы удалось разогнать до частот 1,4 ГГц и выше.

С микроархитектурой NetBurst (и тем же набором команд) выпускается и серверный вариант процессора Xeon (Foster), способный работать в симметричных мультипроцессорных конфигурациях (SMP). Процессор также имеет встроенный вторичный кэш 256 Кбайт, первые модели (1,4, 1,5 и 1,7 МГц) поддерживают 2хSMP, в будущем планируется поддержка до 4 и 8 процессоров.

Сравнительные характеристики процессоров фирмы Intel представлены в таблице.

Процессор |

Год вып. |

Разрядность: РОН/ШД/ША |

Частота системной шины, МГц |

Частота ядра, МГц |

Встроенный кэш* (инструкции/данные) |

Доп.возм.** |

|

8086 8088 |

1978 1979 |

16/16/20 16/8/20 |

4.77-8 |

- |

- |

|

|

80286 |

1982 |

16/16/24 |

8-20 |

- |

- |

|

|

80386DX 80386SX 80386SL |

1985 1988 1991 |

32/32/32 32/16/24 32/16/24 |

16, 20, 33 |

- |

- - SMM |

|

|

i486DXn i486SXn i486SL |

1989 1991 1992 |

32/32/32 |

20, 25, 33 |

20-100 |

L1: 8K (4K/4K) |

FPU - SMM |

|

Pentium |

1993 |

32/64/32 |

50, 60, 66 |

60-200 |

L1: 16K (8K/8K) |

SMM, FPU |

|

Pentium MMX |

1995 |

32/64/32 |

66 |

166, 200, 233 |

L1: 32K (16K/16K) |

SMM, FPU, MMX |

|

Pentium Pro |

1995 |

32/64/36 |

50, 60, 66 |

150-200 |

L1: 16K (8K/8K) L2: 256K, 512K |

SMM, FPU |

|

Pentium II, Pentium II Xeon |

1997 |

32/64/36 |

66,100 |

233-450 |

L1: 32K (16K/16K) L2: 512K |

SMM, FPU, MMX |

|

Celeron (Covington) |

1998 |

32/64/32 |

66 |

266, 300 |

L1: 32K (16K/16K) |

SMM, FPU, MMX |

|

Celeron (Mendocino) |

1998 |

32/64/32 |

66 |

300-533 |

L1: 32K (16K/16K) L2: 128K |

SMM, FPU, MMX |

|

Pentium III, PIII-Coppermine |

1999 |

32/64/36 |

100,133 |

450-600, 500-1130 |

L1: 32K (16K/16K) L2: 256K |

SMM, FPU, MMX, SSE |

|

Celeron (Coppermine) |

2000 |

32/64/32 |

66,100 |

533-900 |

L1: 32K (16K/16K) L2: 128K |

SMM, FPU, MMX, SSE |

|

Pentium III Xeon |

1999 |

32/64/36 |

100, 133 |

500-866 |

L1: 32K (16K/16K) L2: 256K-2M |

SMM, FPU, MMX, SSE |

|

Pentium 4 |

2000 |

32/64/36 |

4x100-200 |

1400+ |

L1: 20K (12К/8K) L2: 256K |

SMM, FPU, MMX, SSE2 |

|

Примечание: * Pentium II/III Xeon выпускаются с L2 кэшем до 2M У Pentium 4: вместо кэша команд - кэш микроопераций ** SMM - процессор поддерживает режим системного управления FPU - процессор содержит встроенный блок вещественной арифметики MMX - процессор поддерживает команды параллельной обработки пакетов целочисленных данных SSE - процессор поддерживает команды параллельной обработки пакетов вещественных данных SSE2 - процессор поддерживает дополнительный набор команд SSE |

|||||||

Начиная с 2004г. Все процессоры INTEL Все последующие модели Pentium 4 будут обладать поддержкой технологии Hyper-Threading, обеспечивающая работу процессора в режиме SMP. Как работает классическая SMP(Symmetric Multi-Processor) - система с точки зрения обычной логики?

Представим, что у нас есть, к примеру, два процессора вместо одного. Что это дает?

В общем-то ничего. Потому что в дополнение к этому нужна еще и операционная система, умеющая задействовать эти два процессора. Эта система должна быть по определению многозадачной (иначе никакого смысла в наличии двух CPU просто быть не может), но кроме этого, ее ядро должно уметь распараллеливать вычисления на несколько CPU. Классическим примером многозадачной ОС, которая этого делать не умеет, являются все ОС “Windows 9x” — 95, 95OSR2, 98, 98SE, Me. Они просто-напросто не могут определить наличие более чем одного процессора в системе. Поддержкой SMP обладают ОС этого же производителя, построенные на ядре NT: Windows NT 4, Windows 2000, Windows XP. Также этой поддержкой обладают все ОС, основанные на идеологии Unix — всевозможные Free- Net- BSD, коммерческие Unix (такие как Solaris, HP-UX, AIX), и многочисленные разновидности Linux. Если же два процессора все же определились системой, то дальнейший механизм их задействования в общем довольно прост. Если в данный момент времени исполняется одно приложение — то все ресурсы одного процессора будут отданы ему, второй же будет просто простаивать. Если приложений стало два — второе будет отдано на исполнение второму CPU, так что по идее скорость выполнения первого не должна уменьшиться. Однако на самом деле все сложнее.

Исполняемое пользовательское приложение может быть запущено всего одно, но количество процессов (т. е. фрагментов машинного кода, предназначенных для выполнения некой задачи) в многозадачной ОС всегда намного больше. Поэтому на самом деле второй CPU способен немного “помочь” даже одиночной задаче, взяв на себя обслуживание процессов, порожденных операционной системой.

Кроме того, даже одно приложение может порождать потоки (threads), которые при наличии нескольких CPU могут исполняться на них по отдельности. Так, например, поступают почти все программы рендеринга — они специально писались с учетом возможности работы на многопроцессорных системах. Поэтому в случае использования потоков выигрыш от SMP иногда довольно весом даже в “однозадачной” ситуации. По сути, поток отличается от процесса только двумя вещами — он во-первых никогда не порождается пользователем (процесс может запустить как система, так и человек, в последнем случае процесс = приложение; появление потока инициируется исключительно запущенным процессом), и во-вторых — поток выгружается вместе с родительским процессом независимо от своего желания. Также не стоит забывать, что в классической SMP-системе оба процессора работают каждый со своим кэшем и набором регистров, но память у них общая. Поэтому если две задачи одновременно работают с ОЗУ, мешать они друг другу будут все равно, даже если CPU у каждой свой.

Ну и наконец последнее: в реальности пользователь имеет дело не с одним, не с двумя, и даже не с тремя процессами. При запуске “голая” Windows XP, сама по себе, не запустив еще ни одного приложения, может породить много процессов, причем многие из них к тому же еще и многопоточные.

Теперь, разобравшись с «физической» многопроцессорностью, перейдем к Hyper-Threading. Фактически — это тоже многопроцессорность, только виртуальная. Ибо процессор Pentium 4 на самом деле один. А процессоров ОС видит — два. Как это ?

Классическому “одноядерному” процессору добавили еще один блок AS — IA-32 Architectural State. Architectural State содержит состояние регистров (общего назначения, управляющих, APIC, служебных). Фактически, AS#1 плюс единственное физическое ядро (блоки предсказания ветвлений, ALU, FPU, SIMD-блоки и пр.) представляет из себя один логический процессор (LP1), а AS#2 плюс все то же физическое ядро — второй логический процессор (LP2). У каждого LP есть свой собственный контроллер прерываний (APIC — Advanced Programmable Interrupt Controller) и набор регистров. Для корректного использования регистров двумя LP существует специальная таблица — RAT (Register Alias Table), согласно данным в которой можно установить соответствие между регистрами общего назначения физического CPU. RAT у каждого LP своя. В результате получается схема, при которой на одном и том же ядре могут свободно выполняться два независимых фрагмента кода т. е. де-факто — многопроцессорную систему!

3.УСТРОЙСТВА ВВОДА-ВЫВОДА

3.1. Видеосистемы компьютера

Видеосистема персонального компьютера состоит из монитора (дисплея) и его видеоадаптера, осуществляющего формирование входных сигналов для монитора. Видеоадаптер либо выполняется на печатной плате, вставляемой в гнездо для дополнительных плат системного блока, либо он представляет собой несколько микросхем в составе основной платы ПЭВМ. Наиболее распространены следующие видеоадаптеры:

- EGA (Enhanced Graphics Adapter), цветной, улучшенной графики, 640*350 пикселов;

- VGA (Video Graphics Array), цветной, видеографический, 640*480 пикселов;

- SuperVGA, цветной, видеографический, 800*600 пикселов или 1024*768 пикселов.

В видеоадаптере ПК можно выделить шесть блоков (рис. 2.1):

- видеопамять;

- последовательный преобразователь;

- видеоконтроллер (контроллер ЭЛТ);

- графический контроллер;

контроллер атрибутов;

синхронизатор.

В работе видеоконтроллера следует различать два режима : текстовый и графический. В графическом режиме память используется для хранения цвета каждого пиксела. Распределение памяти по растровым точкам зависит от вида графического режима и размера памяти, установленного в видеоадаптере. Во всех режимах пикселы размещаются слева направо и сверху вниз в соответствие

Первый графический видеоадаптер для ПЭВМ был разработан в 1981 году и использовался в моделях IBM PC/XT. Емкость видеопамяти CGA - 16 кбайт, что достаточно для поддержки 4 цветов из 16 возможных при разрешении 320*200 пикселов и 2 цветов (монохромный режим) при разрешения 640*200 пикселов. Затем был создан адаптер HGC (1982 год) и позднее - HGC+ (1986 год).

Оба адаптера могут работать только в монохромном графическом режиме с различными оттенками. Емкость памяти – 64 кбайт. Основная особенность этих

позволяют

работать с более эргономическими

шрифтами.

Рис 3.1. Структура видеосистемы ПК

В сентябре 1984 года фирма IBM объявила о выпуске усовершенствованного графического адаптера - EGA. При объеме памяти 256 кбайт такой адаптер предоставляет возможность работать в 12 режимах отображения (поддерживая, в том числе, режимы и записи. Затем был разработан видеоадаптер VGA, который позволяет работать с аналоговыми мониторами, тогда как EGA использует дисплеи цифрового типа. Так же как и EGA, VGA поддерживает работу в монохромном и CGA-совместимом режимах. Разрешение на экране дисплея и количество цветов определяется размером видеопамяти и режимом в котором работает видеосистема ПК .

В концу 1987 г. был разработан адаптер SuperVGA, который поддерживал разрешение 800*600 пикселов при 256-цветовой палитре и 1024*768 пикселов с палитрой из 16 цветов.

Видеопамять EGA и VGA организована в виде четырех цветовых плоскостей (слоев) - областей видеопамяти, имеющих одно и тоже адресное пространство Применение такой архитектуры увеличивает скорость записи в память, поскольку одно обращение к памяти позволяет модифицировать 8 битов цветовой плоскости, а также сократить в четыре раза размер видеобуфера в ОП.

Рассмотрим работу видеоадаптера в некоторых графическом режимах, с размером видеопамяти - 64 Кб. Режим 13h имеет разрешение 320*200. Один пиксел в этом режиме определяется одним байтом и это делает возможным работу с 256 цветами. Начальный адрес видеобуфера в ОП - A000:0000h. Все элементы изображения расположены в нем в такой же последовательности, в которой они выводятся на экран. Для режима 12h адрес видеопамяти A000:0000h - A000:FFFFh. Каждому биту поставлен в соответствие один пиксел, то есть каждый байт позволяет описать 8 пикселов поэтому разрешение экрана будет - 640* 480 в черно-белом цвете.

При визуализации графических объектов на экране дисплея информацию на экран можно выводить тремя способами :

- используя графические модули языков высокого уровня;

- используя функции BIOS (Basic Input Output System);

-напрямую обращаясь к видеопамяти и программируя регистры видеоадаптера. Во всех случаях есть свои преимущества и недостатки. Первые два способа просты и легко "переносимы" на другие ПЭВМ.

Однако, несмотря на универсальность графические модули языков высокого уровня и функции BIOS обладают невысоким быстродействием при выводе сложных графических изображений, при формировании изображений движущихся объектов, поэтому их использование является ограничивающим фактором для синтеза изображений в реальном времени. Кроме того, не все задачи, возникающие при визуализации изображений решаемы с использованием первых двух способов. Если необходимо выводить информацию на экран непосредственно через видеопамять, то необходимо определять биты, управляющие пикселами изображения. По координатам конкретного пиксела можно вычислить адрес байта видеопамяти и номера битов в нем, которые управляют данным пикселом. Формулы, позволяющие определить смещение байта от начала страницы видеопамяти и номера битов в нем, управляющие пикселом с координатами (x,y) для каждого режима различны. Так для режима 10h смещение байта и номер первого бита определяются по формулам :

смещение байта= 50h*y+x/8;

номер бита = 7-mod(x/8).

Доступ в видеопамять адаптера (запись и чтение) ЦП получает через четыре восьмиразрядных буферных регистра - защелки. Каждому буферному регистру ставится в соответствие плоскость битов - рис 3. Эти регистры содержат данные для четырех битовых плоскостей в той позиции, к которой было последнее обращение. Kогда процессор посылает данные по определенному адресу, то эти данные могут изменить или полностью сменить данные регистра защелки, а впоследствии именно данные из регистра защелки записываются в видеобуфер.

Регистр битовой маски графического контроллера и регистр маски записи в видеопамять синхронизатора воздействуют на регистры защелки, защищая определенные биты или битовые плоскости от изменения под действием данных, поступающих от процессора. Таким образом данные процессора влияют на регистр защелки и зависят от установки этих регистров и от используемого режима записи (нулевого, первого или второго). При чтении адреса из видеобуфера регистры защелки заполняются четырьмя байтами из четырех битовых плоскостей по данному адресу. Регистрами защелки легко манипулировать, производя над их содержимым различные логические операции.

Преобразователь последовательности запоминает данные, читаемые из видеопамяти в течение цикла регенерации, преобразует их в последовательный поток битов и затем передает контроллеру атрибутов.

Контроллеры - специальная логика, выполняющая те или иные функции по интерпретации данных и управлению видеосистемой. Они имеют набор регистров, почти все из которых доступны для программирования через соответствующие порты. Программирование видеоадаптеров на уровне регистров позволяет увеличить скорость работы программ и решить задачи не решаемые при помощи функций BIOS. Однако, полученные программы не всегда будут "переносимы" на другие машины. Видеоконтроллер генерирует основные сигналы синхронизации, необходимые для формирования растра, определяет формат данных на экране, управляет счетчиком адреса, синхронизируя его увеличение со скоростью считывания, декодирования и вывода информации на экран, определяет адрес, начиная с которого информация из видеобуфера отображается на экране, контролирует размеры и положение курсора на экране и т.д. Регистры видеоконтроллера загружаются BIOS значениями, зависящими от типа дисплея, видеоадаптера и текущего режима работы. Видеоконтроллер имеет адресный регистр, доступный через порт 3D4h, регистр статуса, доступный через порт 3DAh и 25 регистров данных, доступ к которым осуществляется через порт 3D5h.

Контроллер атрибутов управляет распределением цветов по соответствующим номерам цветов, сканированием рамки и цветом фона. Он содержит 21 регистр, каждый из которых доступны через порт 3С0h. В графических режимах данные из видеопамяти передаются в контроллер атрибутов в виде четырех последовательных битовых потоков (по одному потоку на каждую битовую матрицу). Последовательный преобразователь пропускает при каждом такте по одному биту из одного такого потока. Контроллер атрибута использует 4-ех битовое значение для определения цвета выводимого на экран пиксела (в VGA добавляются 4 постоянных бита и полученное 8-ми битовое значение передается в ЦАП). Синхронизатор обеспечивает процессы записи/считывания видеопамяти, то есть позволяет ЦП обращаться к видеопамяти только во время активных циклов вывода информации на экран, а также разрешает или запрещает доступ к отдельным плоскостям видеопамяти . Синхронизатор также имеет адресный регистр, доступный через порт 3C4h, и 5 регистров данных, доступных через порт 3C5h.

3

3