- •Типы шин.

- •Компьютерная шиина (англ. computer bus) в архитектуре компьютера — подсистема, служащая для передачи

- •Используемые в настоящее время шины отличаются по разрядности, способу передачи сигнала (последовательные или

- •Шинная архитектура

- •Разрядность шины адреса определяет адресное пространство процессора, т.е. количество ячеек оперативной памяти, которые

- •Шина управления

- •Система шин ЭВМ

- •Шинауправле

- •Шинауправле

- •Шинауправле

- •Типичная структура микропроцессорной системы

- •Архитектура компьютера определяет принцип действия, информационные связи и взаимное соединение основных логических узлов

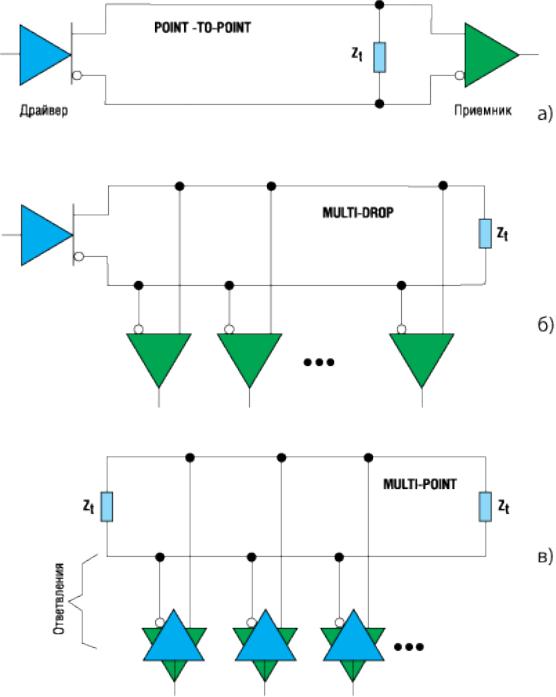

- •Типы обмена информацией по шинам

- •В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив

- •Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки

- •Системная

- •Back side bus (BSB) — шина кэш- памяти второго уровня в процессорах с

- •Front Side Bus (FSB, системная шина) — шина, обеспечивающая соединение между x86- и

- •Частоты, на которых работают центральный процессор и FSB, имеют общую опорную частоту, и

- •Direct Media Interface, сокр. DMI — последовательная шина, разработанная фирмой Intel для соединения

- •HyperTransport (ранее известная как Lightning Data Transport (LDT)) —

- •Шина HyperTransport основана на передаче пакетов. Каждый пакет состоит из 32- разрядных слов,

- •Пакеты HyperTransport передаются по шине последовательно. Увеличение пропускной способности влечёт за собой увеличение

- •Intel QuickPath Interconnect или просто QuickPath, сокр. QPI (ранее Common System Interface, CSI)

- •Каждое соединение шины QuickPath состоит из пары односторонних каналов, каждый из которых физически

- •MultiDrop шина (MDB) является компьютерной шиной, в которой все компоненты подсоединены в одной

- •Шина расширения — компьютерная шина, которая используется на системной карте компьютеров или промышленных

- •Локальная шина

- •Шина PCI

- •Создатели PCI отказались от традиционной концепции, введя еще одну шину между процессором и

- •Шина PCI добавляет к традиционной конфигурации шин еще один уровень. При этом обычная

- •В спецификации PCI определено три типа системных плат, каждая из которых разработана для

- •Обратите внимание, что универсальная плата PCI может устанавливаться в разъем, предназначенный для любой

- •PCI Express, или PCIe, или PCI-E (также известная как 3GIO for 3rd Generation

- •В течение 2001 года специалисты группы компаний, получившей название Arapahoe Work Group (изначально

- •Основные особенности PCI Express таковы:

- •Особенностью архитектуры шин предыдущих поколений является параллельная компоновка, при которой биты данных одновременно

- •В шине PCI Express используется разработанная IBM схема кодирования “8–10”, предусматривающая автосинхронизацию сигналов

- •PCI-Express пока не заменила полностью шину PCI и все остальные интерфейсы, и вряд

- •Гибкие удлинители и переходники для шин PCI Express x16,x8,x4,x1, PCI32, PCI64, PCI-

- •PCIEXP1-X1, PCIEXP4-X1, PCIEXP8-X1, PCIEXP16-X1, PCIEXP16-RX1, PCIEXP16-CE1, - Удлинители для шин PCI Express X1,

- •PCIEXP1-X2, PCIEXP4-X2, PCIEXP8-X2, PCIEXP16-X2, PCIEXP16-RX1, - Удлинители для шин PCI Express X1, X4,

- •PCIEXP1-X3, PCIEXP4-X3, PCIEXP8-X3 и PCIEXP16-X3 - Удлинителидля шин PCI Express X1, X4, X8

- •PCIEXP1-SX, PCIEXP4-SX, PCIEXP8-SX и PCIEXP16-SX- Удлинители для шин PCI Express X1, X4, X8

- •PCIEXP4-SX-4/1, PCIEXP8-SX-8/4,PCIEXP16-SX-16/8и PCIEXP16-SX-16/1 - Конвертеры для шин PCI Express, предназначенные для установки плат

- •PCIEXP16-SL057

- •Плата адаптер с PCI на PCI-Express 16x.

- •Угловой переходник для шины PCI-Express 16Х

- •Гибкий удлинитель слота PCI 32

- •Гибкий адаптер PCI-Express 8x на PCI-Express 16х

- •Райзер карта расширитель двух слотов PCI

- •Гибкий удлинитель слота PCI-X / PCI 64

- •Гибкий удлинитель слота PCI-X / PCI 64

- •Гибкий удлинитель для разъма AGP

- •Адаптер для тестирования плат PCI Express 16X

- •PCI-Express 4.0 обеспечит передачу 16 ГТ/с

Front Side Bus (FSB, системная шина) — шина, обеспечивающая соединение между x86- и x64-совместимым центральным процессором и внутренними устройствами.

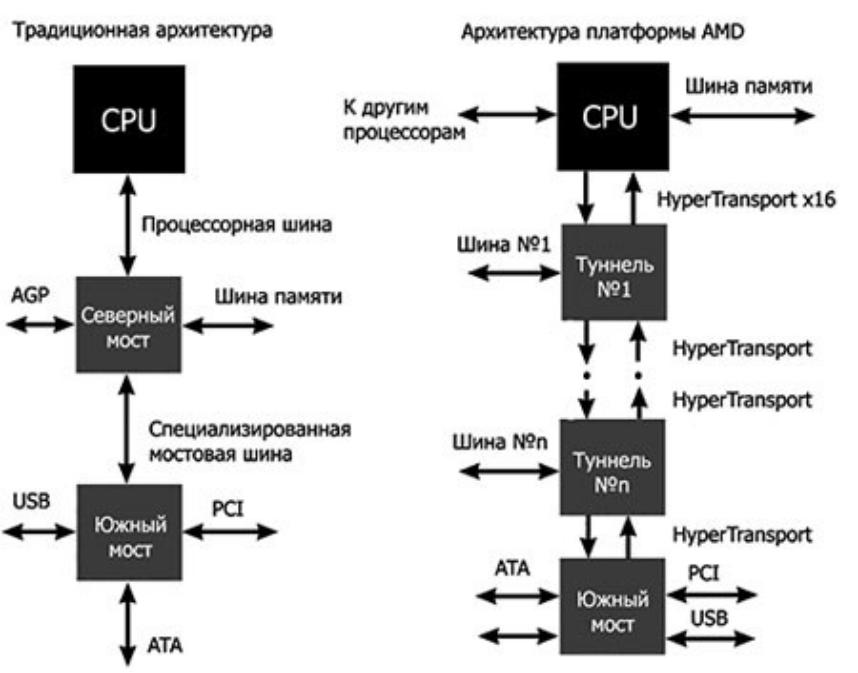

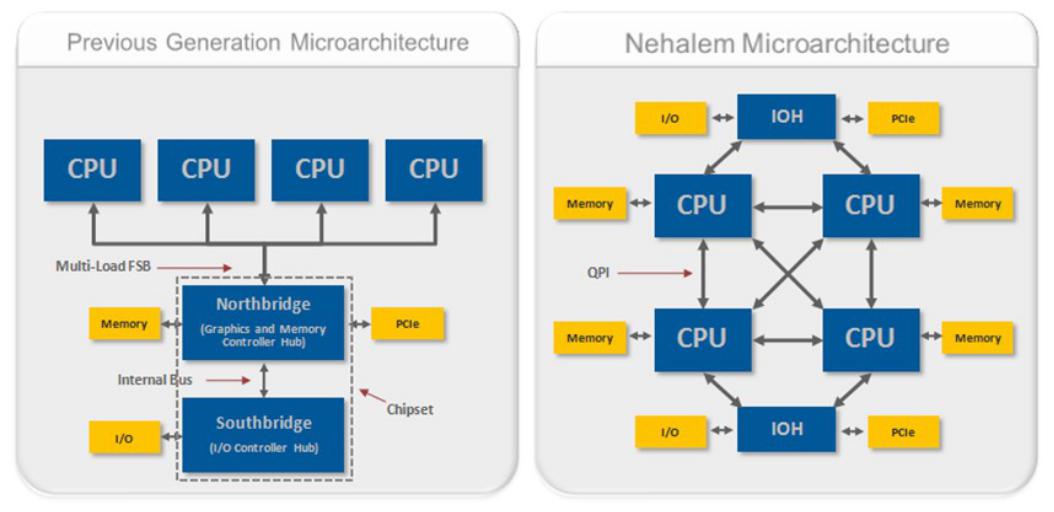

Как правило, современный персональный компьютер на базе x86- и x64-совместимого микропроцессора устроен следующим образом: микропроцессор через FSB подключается к системному контроллеру, который обычно называют «северным мостом», (англ. Northbridge). Системный контроллер имеет в своём составе контроллер ОЗУ (в некоторых современных персональных компьютерах контроллер ОЗУ встроен в микропроцессор), а также контроллеры шин, к которым подключаются периферийные устройства. Получил распространение подход, при котором к северному мосту подключаются наиболее производительные периферийные устройства, например, видеокарты с шиной PCI Express 16x, а менее производительные устройства (микросхема BIOS'а, устройства с шиной PCI) подключаются к т. н. «южному мосту» (англ. Southbridge), который соединяется с северным мостом специальной шиной. Набор из «южного» и «северного» мостов называют набором системной логики, но чаще применяется калька с английского языка «чипсет» (англ. chipset).

Таким образом, FSB работает в качестве магистрального канала между процессором и чипсетом.

Некоторые компьютеры имеют внешнюю кэш-память, подключенную через «заднюю» шину (англ. back side bus), которая быстрее, чем FSB, но работает только со специфичными устройствами.

Каждая из вторичных шин работает на своей частоте (которая может быть как выше, так и ниже частоты FSB). Иногда частота вторичной шины является производной от частоты FSB, иногда задаётся независимо.

Частоты, на которых работают центральный процессор и FSB, имеют общую опорную частоту, и в конечном счете определяются, исходя из их коэффициентов умножения (частота устройства = опорная частота * коэффициент умножения).

Современные процессоры имеют встроенный контроллер памяти, поэтому в них очень слабая зависимость производительности процессора от FSB.

Существуют системы, преимущественно старые, где FSB и периферийные шины ISA, PCI, AGP имеют общую опорную частоту, и попытка изменения частоты FSB не посредством её коэффициента умножения, а посредством изменения опорной частоты приведет к изменению частот периферийных шин, и даже внешних интерфейсов, таких, как Parallel ATA. На других системах, преимущественно новых, частоты периферийных шин не зависят от частоты FSB.

В системах с высокой интеграцией контроллеры памяти и периферийных шин могут быть встроены в процессор, и сама FSB в таких процессорах отсутствует принципиально. К таким системам можно отнести персональную платформу Intel LGA1156.

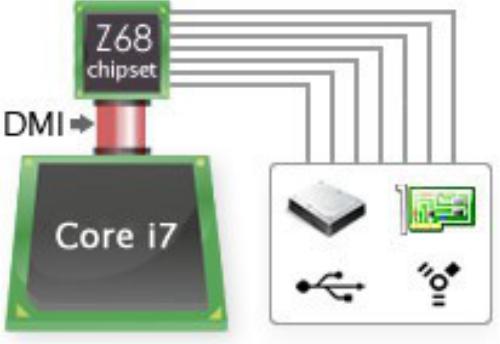

Direct Media Interface, сокр. DMI — последовательная шина, разработанная фирмой Intel для соединения южного моста (ICH) материнской платы c северным (MCH или GMCH). Впервые DMI использована в чипсетах семейства Intel 915 с южным мостом ICH6 в 2004 году. Серверные чипсеты используют похожий интерфейс, называемый Enterprise Southbridge Interface (ESI). Позже интерфейс DMI получил 2 обновления.

DMI 3.0 был представлен в августе 2015. В третьем поколении скорость обменов была увеличена до 8 GT/s (гигатранзакций в секунду) на каждой линии. Интерфейс с 4 линиями позволяет передавать данные со скоростью до 3,93 ГБ/с между процессором и PCH. Используется в процессорах с микроархитектурой Skylake (варианты с 2 чипами) и чипсетах Intel серии 100, например Z170

HyperTransport (ранее известная как Lightning Data Transport (LDT)) —

двунаправленная последовательно-параллельная компьютерная шина с высокой пропускной способностью и малыми задержками. Для разработки и продвижения данной шины был образован консорциум HyperTransport Technology.

HyperTransport работает на частотах от 200 МГц до 3,2 ГГц (у шины PCI — 33 и 66 МГц). Кроме того, она использует DDR, что означает, что данные посылаются как по фронту, так и по срезу сигнала синхронизации, что позволяет осуществлять до 5200 миллионов посылок в секунду при частоте сигнала синхронизации 2,6 ГГц; частота сигнала синхронизации настраивается автоматически.

HyperTransport поддерживает автоматическое определение ширины шины от 2 до 32 бит. Полноразмерная полноскоростная 32-битная шина в двунаправленном режиме способна обеспечить пропускную способность до 51 600 Мбайт/с = 2 (DDR) × 2 × 32/8 (байт) × 3200 (МГц) (максимум в одном направлении — 25 600 Мбайт/с), являясь, таким образом, самой быстрой шиной среди себе подобных. Шина может быть использована как в подсистемах с высокими требованиями к пропускной способности (оперативная память и ЦПУ), так и в подсистемах с низкими требованиями (периферийные устройства). Данная технология также способна обеспечить низкие задержки для других применений в других подсистемах.

Шина HyperTransport основана на передаче пакетов. Каждый пакет состоит из 32- разрядных слов, вне зависимости от физической ширины шины (количества информационных линий). Первое слово в пакете — всегда управляющее слово. Если пакет содержит адрес, то последние 8 бит управляющего слова сцеплены со следующим 32-битным словом, в результате образуя 40-битный адрес. Шина поддерживает 64-разрядную адресацию — в этом случае пакет начинается со специального 32-разрядного управляющего слова, указывающего на 64-разрядную адресацию, и содержащего разряды адреса с 40 по 63 (разряды адреса нумеруются начиная с 0). Остальные 32-битные слова пакета содержат непосредственно передаваемые данные. Данные всегда передаются 32-битными словами, вне зависимости от их реальной длины (например, в ответ на запрос на чтение одного байта по шине будет передан пакет, содержащий 32 бита данных и флагом-признаком того, что значимыми из этих 32 бит являются только 8).

Пакеты HyperTransport передаются по шине последовательно. Увеличение пропускной способности влечёт за собой увеличение ширины шины. HyperTransport может использоваться для передачи служебных сообщений системы, для передачи прерываний, для конфигурирования устройств, подключённых к шине, и для передачи данных.

Операция записи на шине бывает двух видов — posted и non-posted. Posted-операция записи заключается в передаче единственного пакета, содержащего адрес, по которому необходимо произвести запись, и данные. Эта операция обычно используется для обмена данными с высокоскоростными устройствами, например, для DMA-передачи. Non-posted операция записи состоит из посылки двух пакетов: устройство, инициирующее операцию записи, посылает устройству-адресату пакет, содержащий адрес и данные. Устройство-адресат, получив такой пакет, проводит операцию записи и отсылает устройству-инициатору пакет, содержащий информацию о том, успешно ли произведена запись. Таким образом, posted-запись позволяет получить максимальную скорость передачи данных (нет затрат на пересылку пакета-подтверждения), а non-posted-запись позволяет обеспечить надёжную передачу данных (приход пакета-подтверждения гарантирует, что данные дошли до адресата).

Шина HyperTransport поддерживает технологии энергосбережения, а именно ACPI. Это значит, что при изменении состояния процессора (C-state) на энергосберегающее изменяется также и состояние устройств (D-state). Например, при отключении процессора жёсткие диски также отключаются.

Электрический интерфейс HyperTransport/LDT — низковольтные дифференциальные сигналы с напряжением 1,2 В.

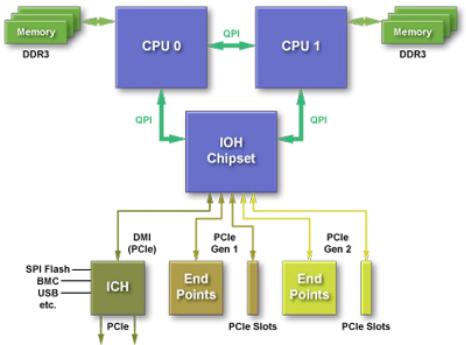

Intel QuickPath Interconnect или просто QuickPath, сокр. QPI (ранее Common System Interface, CSI) — последовательная кэш-когерентная шина типа точка-точка для соединения между процессорами и чипсетом, разработанная фирмой Intel. QPI создавалась в ответ на разработанную ранее консорциумом во главе с фирмой AMD шину HyperTransport.

Шина QuickPath была создана для замены применявшейся ранее шины Front Side Bus, которая осуществляла связь между центральным процессором и северным мостом материнской платы. По состоянию на начало 2010 года, внешний интерфейс QuickPath используется только в сериях процессоров Xeon и Core i7 с ядром Nehalem для разъема LGA 1366, а также будет использоваться в следующем поколении Itanium (ядро Tukwila). При этом чипсеты для разъёма LGA 1366 используют шину DMI для связи между северным и южным мостом. Процессоры для разъёма LGA 1156 не имеют внешнего интерфейса QuickPath, поскольку чипсеты для данного разъёма поддерживают только однопроцессорную конфигурацию, а функциональность северного моста встроена в сам процессор (и, следовательно, для связи процессора с аналогом южного моста используется шина DMI). Однако внутри процессора LGA 1156 связь между ядрами и встроенным контроллером PCIe осуществляется через встроенную шину QuickPath

Каждое соединение шины QuickPath состоит из пары односторонних каналов, каждый из которых физически реализован как 20 дифференциальных пар проводов. Данные передаются в виде пакетов (дейтаграмм). Пропускная способность одного канала составляет от 4,8 до 6,4 GT/s (гигатранзакций в секунду). Одна передача содержит 16 бит полезной нагрузки, следовательно, теоретическая суммарная пропускная способность одного соединения (в двух направлениях) — от 19,2 до 25,6 гигабайт в секунду (то есть от 9,6 до 12,8 гигабайт/с в каждую сторону); при этом один процессор может иметь несколько соединений.

MultiDrop шина (MDB) является компьютерной шиной, в которой все компоненты подсоединены в одной электрической цепи. Процесс арбитража определяет, какое устройство посылает информацию в любой точке. Другие устройства прослушивания данные по шине, которые им необходимо получить.

MultiDrop шина используется в торговых автоматах, контроллеры обмениваться данными с компонентами торгового автомата, таких как приемники денежных средств.