В конце документа есть примеры команды ветвления (bneg) и пример команды загрузки (ld).

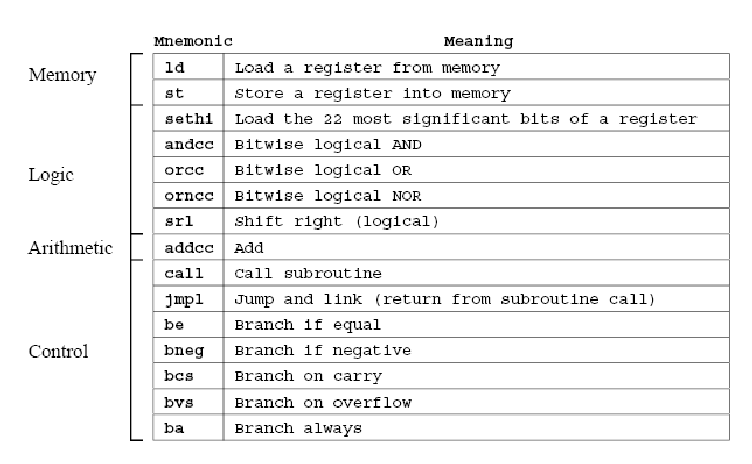

Группы команд ARC процессора

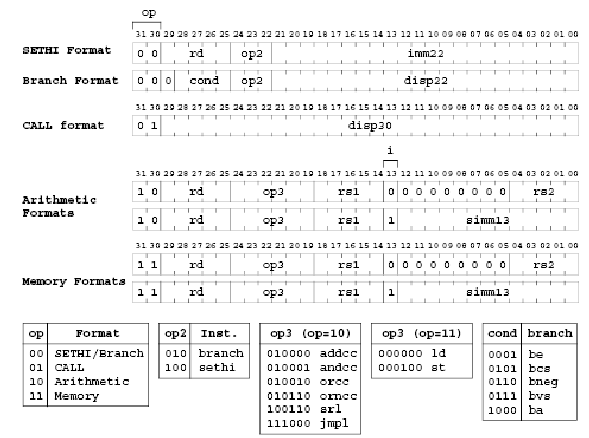

Формат команд процессора ARC

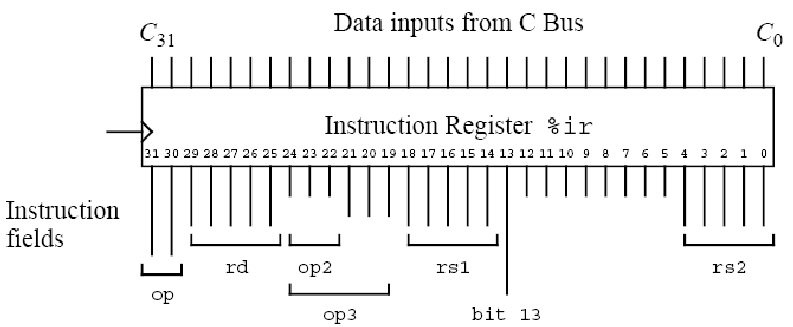

Поля регистра команд (IR)

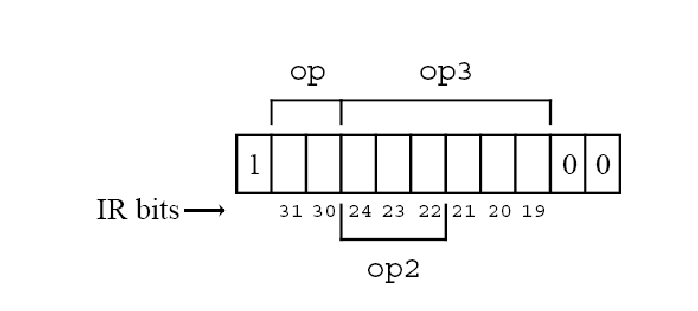

Формат декодирования адреса микрокоманды

К примеру, декодируем команду сложения, то op=10 (т.к. это арифметическая команда), а поле op3=010000 (код самой команды addcc). Т.е.

В блок декодирования идут следующие биты(код команды): 10010000 [op, op3]. А при декодировании получаем следующий адрес: 11001000000=[1, op, op3, 00]=1024+512+64=1602. После для выполнения команды переходим к микрокоманде по найденному адресу.

Второй пример, предположим, что декодируем команду ветвления, а именно, переход при условии эквивалентности. У этой команды поле op=00 (группа команд ветвления), op2=010. В командах ветвления при декодировании не важен код конкретной команды, т.к. у них всех одинаковый адрес начала выполнения микрокода.

Итак, в блок декодирования идут следующие биты(код команды): 00010000 [op, op2, 000]. При декодировании получаем следующий адрес: 10001000000=[1, op, op2, 000]=1024+64=1088. 1088 – адрес микрокода исполнения команды для всех команд ветвления.

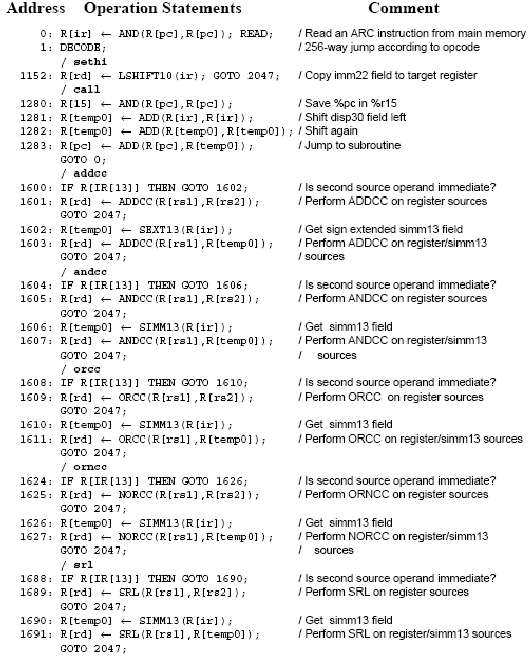

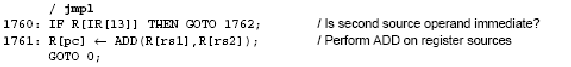

Микрокод процессора ARC

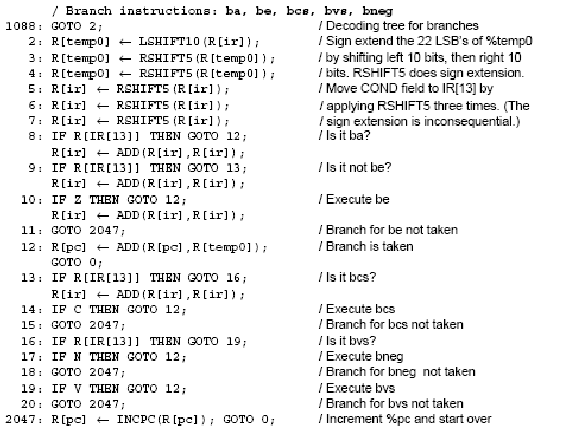

Декодирование (идентификация) ветвления

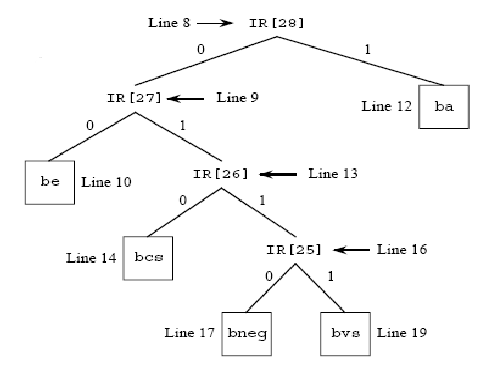

Поле cond регистра команд (IR)

Декодирование конкретной команды ветвления заключается в том, что значение регистра команд (IR) сдвигают так, чтобы 28-й бит стал 13-м. Т.к. 13-й бит (IR[13]) связан с устройством управления ветвлениями (Control branch logic).

Поэтому логика распознавания конкретной команды ветвления такая:

-

13 12 11 10

Команда ветвления

0 0 0 1

be

0 1 0 1

bcs

0 1 1 0

bneg

0 1 1 1

bvs

1 0 0 0

ba

Если после этих сдвигов 13-й бит равен 1, то это команда ba.

Иначе, следует искать из оставшихся 4-х (be, bcs, bneg, bvs) команд, далее выполняют сложение полученного значения после сдвига IR с самим собой (т.е. умноженного на 2 или сдвинутого влево на 1 разряд). Получается, что биты с 13 по 10 будут теперь такими:

-

13 12 11 10

Команда ветвления

0 0 1 *

be

1 0 1 *

bcs

1 1 0 *

bneg

1 1 1 *

bvs

* - бит равный 0 или 1, пришедший из 10-ого бита.

Получаем следующее, что если 13-й бит равен 0, то это точно команда be.

Иначе, следует искать из оставшихся не идентифицированных полностью команд (bcs, bneg, bvs). Опять выполняется сложение значения регистра команд с собой. Получаем следующие значения бит с 13 по 10:

-

13 12 11 10

Команда ветвления

0 1 * *

bcs

1 0 * *

bneg

1 1 * *

bvs

Если 13-й бит равен 0, то следует выполнять команду ветвления bcs. Иначе, это одна из двух команд (bneg, bvs). Опять выполняем сложение регистра команд с собой же. Получаем следующие значения бит с 13 по 10:

-

13 12 11 10

Команда ветвления

0 * * *

bneg

1 * * *

bvs

Если 13-й бит регистра команд (IR[13]) равен 1, то следует выполнять команду bvs. Иначе, перейти к выполнению команды bneg.

Заполнение полей регистра микрокоманд (MIR)

Поле COND регистра микрокоманд (МIR)

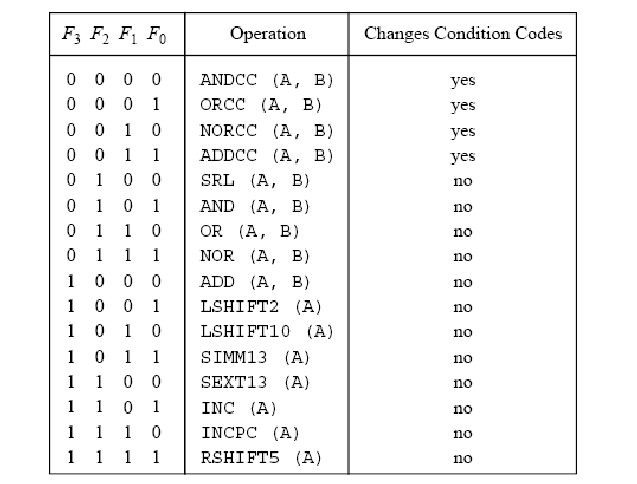

Операции АЛУ

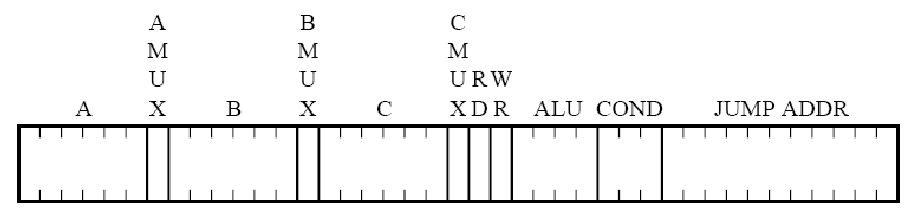

Поля регистра микрокоманд (MIR)

Поле A содержит код регистра источника. Этот код направляется на мультиплексор A (на входной информационный канал), управляющим сигналом для мультиплексора A является поле AMUX регистра микрокоманд (MIR). Если поле AMUX равно 0, то на выходе мультиплексора A появляется значение поля A регистра микрокоманд (MIR), иначе, на выходе мультиплексора A появляется значение [0, rs1], где rs1 - поле регистра команд (IR).

Поле B содержит код регистра источника. Этот код направляется на мультиплексор B (на входной информационный канал), управляющим сигналом для мультиплексора B является поле BMUX регистра микрокоманд (MIR). Если поле BMUX равно 0, то на выходе мультиплексора B появляется значение поля B регистра микрокоманд (MIR), иначе, на выходе мультиплексора B появляется значение [0, rs2], где rs2 - поле регистра команд (IR).

Поле C содержит код регистра приёмника. Этот код направляется на мультиплексор C (на входной информационный канал), управляющим сигналом для мультиплексора C является поле CMUX регистра микрокоманд (MIR). Если поле CMUX равно 0, то на выходе мультиплексора C появляется значение поля C регистра микрокоманд (MIR), иначе, на выходе мультиплексора C появляется значение [0, rd], где rd - поле регистра команд (IR).

В приведенном выше изложении упоминаются такие значения: [0, rs1], [0, rs2], [0, rd]. Эти результаты получаются в результате того, что пользователю программно доступны 32 регистра, которые кодируются 5 битами, но сам блок регистров содержит ещё и 6 программно недоступных регистров. Поэтому для кодирования всех регистров нужно 6 разрядов. Поэтому здесь простым добавлением старшего бита выполняется переход от пользовательской кодировки программно доступных регистров к кодировке всех регистров.

Поле AMUX – см. поле A.

Поле BMUX – см. поле B.

Поле CMUX – см. поле C.

Поле RD - если поле равно 1, то происходит чтение из памяти по адресу (шина A из блока регистров).

Поле WR - если поле равно 1, то происходит запись в памяти по адресу (шина A из блока регистров) значения (шина B из блока регистров).

Для того чтобы получить значения на этих шинах, нужно обратиться с какой-нибудь командой (AND, OR и т.д.) к АЛУ и указать коды регистров, с которых требуется получить значения. Для записи – это обязательно должна быть двух операндная команда.

Поле ALU – код операции АЛУ.

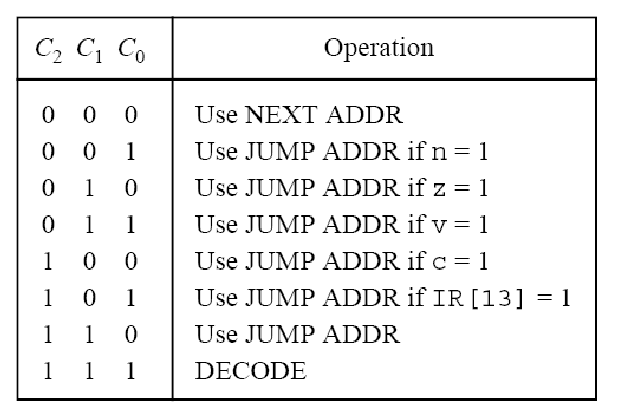

Поле COND – условие (condition) перехода. Принимает следующие значения: декодирование (DECODE) команды и получение адреса микрокода для её непосредственного исполнения; переход на следующий адрес микрокода при значении NEXT; условные переходы – переход, если выставлены флаги n, z, v, c; а также безусловный переход.

Поле JUMP ADDR – при выполнении условия, переходит в микропрограмме по адресу равному значению этого поля, за исключением условий (DECODE, NEXT в поле COND).

За управление ветвлением отвечают следующие устройства процессора:

Устройство управления ветвлением (control branch logic) – на вход этого устройства поступает поле COND регистра микрокоманд (т.е. код конкретной команды ветвления), 13-й бит (бит непосредственной адресации) из регистра команд (IR), а также значение слова состояния (т.е. регистров флагов psr). На выходе этого устройства получаем 3 сигнала (в зависимости от выполнения условия и самого условия): next, jump, instruction decode.

Счётчик адреса микропрограммы (CSAI – control store address incrementer) – следующий адрес микрокода (т.е. текущий адрес микрокода +1). Входной информацией этого устройства является текущий адрес микропрограммы, выходной – инкрементированное значение входного значения.

Мультиплексор адреса микропрограммы (CS address MUX) – мультиплексор, который в зависимости от кода перехода (next, jump, instruction decode), полученного с устройства управления ветвлением, выбирает адрес, на который перейдет микропрограмма. Если на управляющий вход мультиплексора пришло значение next, то на выход подаётся значение адреса, которое получено счётчиком адреса микропрограммы. Если на управляющий вход пришло значение jump, то значение адреса берётся из поля JUMP ADDR регистра микрокоманд (MIR). Если на управляющий вход пришло значение instruction decode, то значение адреса получается путем добавления к коду команды (31, 30, 24-19 биты регистра команд) одного старшего бита, равного 1, и двух младших битов, равных 0.

Пример микрокода команды bneg

1) Формат команды:

bneg disp22 ; если слове состояния (регистре psr) бит n =1 (т.е. переход при отрицательном значении), то перейти по адресу = текущий адрес + disp22.

Код команды: op=00, op2=010, 000.

Адрес при декодировании: 10001000000=1024+64=1088.

2) Микрокод команды bneg:

0: IR=AND(PC, PC); MemRD.

//выполнение этой микрокоманды не связано с какой-то конкретной командой АЛУ, т.к. у нас выполняется операция чтения. Даже когда операция в АЛУ выполнится, то её результат не сохранится, т.к. мультиплексор C Bus из двух шин данных из памяти и из АЛУ выберет одну в зависимости от поля RD в регистре микрокоманд. В нашем случае, это будет шина данных из памяти, как раз она и сохранится в блоке регистров.

Посмотрите на схему процессора ARC. Проследите за значением поля RD из регистра микрокоманд (MIR). Оно управляет чтением из основной памяти, а также является сигналом выбора для мультиплексора C Bus (C Bus MUX).

Когда сигнал чтения выставлен, то адрес, по которому должно произойти чтение берётся с шины A. Но для этого на шине A должно появиться значение. Оно там появится, только если на информационные каналы мультиплексора A подать код регистра, из которого надо считать информацию.

Так для нашего случая, в регистре микрокоманд (MIR) в поле A нужно указать код регистра PC.

1: Decode.

…

1088: Jump 2.

//этот адрес одинаковый для всех команд ветвления

…

2: temp0=LSHIFT10(IR).

3: temp0=RSHIFT5(temp0).

4: temp0=RSHIFT5(temp0).

//выполнение действий со 2-ого адреса по 4-й дают следующее:

в регистре команд содержится 22 битное значение смещения адреса. Задача заключается в том, чтобы корректно переписать только это 22 битное значение в регистр (в нашем случае, это регистр temp0). Следует напомнить, что все регистры 32 битные. И в регистре команд помимо 22 битного значения смещения старшие 10 бит заняты кодами команды и др.

Для корректного извлечения значения смещения сначала в регистр temp0 записывается значение регистра команд (IR) смещенное на 10 разрядов влево. Это действие нужно для того, чтобы избавится от лишних 10 битов, которые также хранятся в регистре команд (это старшие 10 бит).

После этого регистр temp0 2 раза сдвигается вправо на 5 разрядов каждый раз (т.к. нет команды сдвига вправо на 10 разрядов). Это возвращает обратно веса разрядов, и в регистре temp0 хранится 22 битное значение из регистра команд. А старшие 10 бит регистра temp0 хранят нулевые значения.

5: IR=RSHIFT5(IR).

6: IR=RSHIFT5(IR).

7: IR=RSHIFT5(IR).

//выполнение действий с 5-ого адреса по 7-й дают возможность сдвинуть вправо на 15 разрядов регистр команд, получаем, что 28-й бит (старший бит поля cond регистра IR) становится 13-м. Следовательно, он влияет на устройство управления ветвлением (Control branch logic). [см. выше декодирование ветвления и поле cond]

8: JIMM 12; IR=ADD(IR, IR). //если бит непосредственного значения выставлен (т.е. равен 1), то это команда ветвления ba. Иначе, одна из 4-х (be, bcs, bneg, bvs).

9: JIMM 13; IR=ADD(IR, IR). //если бит непосредственного значения равен 1, то это одна из 3-х команд (bcs, bneg, bvs). Иначе, следует перейти на следующий адрес микрокода (10) и выполнить команду be. [см. выше декодирование ветвления и поле cond]

…

13: JIMM 16; IR=ADD(IR, IR). //если бит непосредственного значения равен 1, то это одна из 2-х команд bneg, bvs). Иначе, следует перейти на следующий адрес микрокода (14) и выполнить команду bcs. [см. выше декодирование ветвления и поле cond]

16: JIMM 19; IR=ADD(IR, IR). //если бит непосредственного значения равен 1, то это команда bvs. Иначе, следует перейти на следующий адрес микрокода (17) и выполнить команду bneg. [см. выше декодирование ветвления и поле cond]

17: JN 12.

18: Jump 2047.

…

12: PC=ADD(PC, temp0); JUMP 0.

…

2047: PC=INC(PC); JUMP 0.

3) Заполнение полей регистра микрокоманд (MIR):

0: IR=AND(PC, PC); MemRD.

A=PC

B= PC

C=IR

//Это микрокоманда загружает в регистр IR команду из памяти программы по адресу равному значению регистра PC. PC и IR – эти регистры не доступны пользователю, поэтому их коды должны браться из регистра микрокоманд.

AMUX=0 (код регистра-источника берётся из регистра микрокоманд (MIR))

BMUX=0 (код регистра-источника берётся из регистра микрокоманд (MIR))

CMUX=0 (код регистра-приёмника берётся из регистра микрокоманд (MIR))

RD=1

WR=0

ALU=AND

COND=NEXT

JUMP ADDR=*