- •1. Основные понятия, стандарты и организации, действующие в области ис.

- •2. Семиуровневая модель вос.

- •Уровень 1, физический

- •3. Tcp/ip, распределение протоколов по уровням вос.

- •4. Протоколы ip, arp, rarp.

- •5. Протоколы tcp , icmp , udp.

- •6. Протокол tcp, алгоритм скользящего окна.

- •Разделение ip-сети на подсети, специальные адреса, частные адреса.

- •Механизм передачи информации в локальной сети.

- •11. Типы передачи пакетной информации (multicast, unicast, anycast, broadcast).

- •12. Технологии локальных сетей. Ethernet.

- •13. Адресация Ethernet, физические адреса.

- •14. Скс, основные принципы и стандарты.

- •15. Коммутаторы на основе коммутационной матрицы

- •17. Коммутаторы с общей шиной

- •Трехуровневая иерархическая модель сети.

- •Понятие петель. Широковещательный шторм.

- •Виртуальные локальные сети vlan, Tagged и Untagged .

15. Коммутаторы на основе коммутационной матрицы

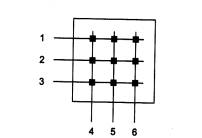

К оммутационная

матрица обеспечивает

основной и самый быстрый способ

взаимодействия процессоров портов,

именно он был реализован в первом

промышленном коммутаторе локальных

сетей. Однако реализация матрицы возможна

только для определенного числа портов,

причем сложность схемы возрастает

пропорционально квадрату количества

портов коммутатора (рис. 4.31).

оммутационная

матрица обеспечивает

основной и самый быстрый способ

взаимодействия процессоров портов,

именно он был реализован в первом

промышленном коммутаторе локальных

сетей. Однако реализация матрицы возможна

только для определенного числа портов,

причем сложность схемы возрастает

пропорционально квадрату количества

портов коммутатора (рис. 4.31).

Рис. 1. Коммутационная матрица

Б олее

детальное представление одного из

возможных вариантов реализации

коммутационной матрицы для 8 портов

дано на рис. 4.32. Входные блоки процессоров

портов на основании просмотра адресной

таблицы коммутатора определяют по

адресу назначения номер выходного

порта. Эту информацию они добавляют к

байтам исходного кадра в виде специального

ярлыка - тэга (tag). Для данного примера

тэг представляет собой просто 3-разрядное

двоичное число, соответствующее номеру

выходного порта.

олее

детальное представление одного из

возможных вариантов реализации

коммутационной матрицы для 8 портов

дано на рис. 4.32. Входные блоки процессоров

портов на основании просмотра адресной

таблицы коммутатора определяют по

адресу назначения номер выходного

порта. Эту информацию они добавляют к

байтам исходного кадра в виде специального

ярлыка - тэга (tag). Для данного примера

тэг представляет собой просто 3-разрядное

двоичное число, соответствующее номеру

выходного порта.

Рис. 2. Реализация коммутационной матрицы 8х8 с помощью двоичных переключателей

Матрица состоит из трех уровней двоичных переключателей, которые соединяют свой вход с одним из двух выходов в зависимости от значения бита тэга. Переключатели первого уровня управляются первым битом тэга, второго - вторым, а третьего - третьим.

Матрица может быть реализована и по-другому, на основании комбинационных схем другого типа, но ее особенностью все равно остается технология коммутации физических каналов. Известным недостатком этой технологии является отсутствие буферизации данных внутри коммутационной матрицы - если составной канал невозможно построить из-за занятости выходного порта или промежуточного коммутационного элемента, то данные должны накапливаться в их источнике, в данном случае - во входном блоке порта, принявшего кадр. Основные достоинства таких матриц - высокая скорость коммутации и регулярная структура, которую удобно реализовывать в интегральных микросхемах. Зато после реализации матрицы NxN в составе БИС проявляется еще один ее недостаток - сложность наращивания числа коммутируемых портов.

16.

Коммутаторы

с разделяемой памятью

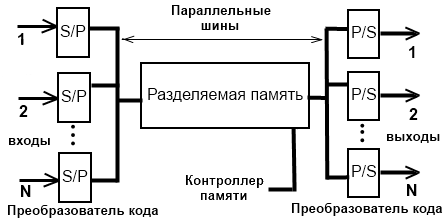

Основные принципы построения таких

устройств иллюстрирует рис. 2. Трудность

реализации этой архитектуры заключается

в том, что при наличии N входных (и

выходных) портов быстродействие памяти

должно быть в N раз выше, чем скорость

поступления данных в порт. Поэтому такие

коммутаторы оборудуются высокоскоростной

внутренней многоразрядной шиной, а

поступающий поток бит из последовательного

кода преобразуется в параллельный. Для

обеспечения приемлемой частоты

тактирования шину делают достаточно

широкой. Так, если W -- разрядность шины,

то необходимая тактовая частота будет

в N/W раз меньше, чем пропускная способность

порта.

16.

Коммутаторы

с разделяемой памятью

Основные принципы построения таких

устройств иллюстрирует рис. 2. Трудность

реализации этой архитектуры заключается

в том, что при наличии N входных (и

выходных) портов быстродействие памяти

должно быть в N раз выше, чем скорость

поступления данных в порт. Поэтому такие

коммутаторы оборудуются высокоскоростной

внутренней многоразрядной шиной, а

поступающий поток бит из последовательного

кода преобразуется в параллельный. Для

обеспечения приемлемой частоты

тактирования шину делают достаточно

широкой. Так, если W -- разрядность шины,

то необходимая тактовая частота будет

в N/W раз меньше, чем пропускная способность

порта.

Пакеты, предназначенные для разных портов, хранятся в специально отведенных раздельных областях памяти. Будут ли эти разделы фиксированной длины или переменной, зависит от особенностей реализации обсуждаемой архитектуры. Очевидно, что разделы переменной длины требуют более сложного управления, однако такой подход позволяет в большинстве случаев решить проблемы переполнения и значительно снизить потерю пакетов. Для выполнения операций записи и чтения за один такт память делается двухпортовой. Поскольку увеличение количества портов требует соответствующего повышения быстродействия памяти, то эта архитектура плохо расширяется. Кроме этого, контроллер, осуществляющий управление буферами, должен обрабатывать заголовки пакетов и маршрутные теги с той же скоростью, с которой работает память. Поэтому такой дизайн наиболее часто используется в небольших скоростных коммутаторах для объединения локальных сетей. Однако даже для коммутаторов средней (по количеству портов) величины требуемая частота внутренней шины становится чрезмерно большой. Так, для коммутатора с 32 входными портами и 16-разрядной шиной при скорости поступления данных 155 Mbps на порт необходимая тактовая частота внутренней шины составила бы 310 MHz.