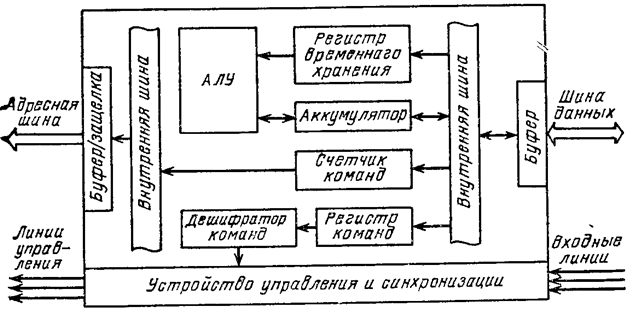

- •Структурная схема типового микропроцессора

- •Микро- эвм 8086.

- •Интерфейс. Определение интерфейса.

- •Состав микропроцессорного комплекта.

- •Микропроцессорный управляющий вычислительный комплекс. (мувк)

- •Язык ассемблера.

- •Многокристальные секционированные микропроцессоры.

- •Умножение двоичных чисел

- •9.Система команд мп кр580 ик80

- •11. Структура микропроцессора. Назначение линий шины управления.

- •12. Назначение управляющих сигналов в мп.

- •13. Постановка и решение задачи управления с помощью мп

- •18. Функционирование микроЭвм.

- •19. Регистр признаков.

- •20. Структура алу.

- •21. Синтез схемы контроля параметров технологического процесса.

- •22. Устройство управления и синхронизации мп

- •23. Примеры построения программ на ассемблере.

- •24. Назначение управляющих сигналов, поступающих по шине данных.

- •25. Стек. Определение.

- •26. Назначение выводов микропроцессора.

- •27. Регистры мп.

- •28. Счетчик команд мп.

- •29. Машинные коды.

- •30. Ацп. Схемы ацп. Технические характеристики.

- •31. Кодирование. Числовые коды.

- •33. Разделение сигналов при передаче по каналам связи.

- •34. Составные коды.

- •35. Пропускная способность канала связи.

- •36. Коды с обнаружением и исправлением ошибок.

- •37. Код Грея.

- •38. Преобразование двоичных чисел в десятичные с помощью регистров сдвига.

- •39. Код Хемминга.

- •40. Минимизация логических функций.

- •42. Мультиплексор. Схема и принцип действия.

- •43. Система команд мп кр580 ик 80.

- •44. Схема инкремент-декремент.

- •45. Дешифраторы.

- •47. Методы и схемы преобразования аналоговых сигналов в дискретные.

- •48. Структура умк.

Структурная схема типового микропроцессора

Основным устройством всех информационных систем является центральный процессор (ЦП). Из многочисленных ИС роль ЦП систем выполняют микропроцессоры, обычно в технологии микроинформационной техники программную память, память данных, интерфейс ввода-вывода, дешифратор адресов выполняют на различных ИС как это показано на рис. 4.1.

Центральным устройством системы является микропроцессор, который содержит обычно элементы размещения данных, называемые регистрами, и устройство счета, называемое арифметико-логическим устройством (АЛУ). Центральное устройство содержит также цепь декодирования команд и секцию управления и синхронизации. Оно снабжено также необходимыми соединениями с устройством ввода/вывода.

Основными функциями центрального устройства микро-ЭВМ являются следующие:

извлечение, декодирование и выполнение команд программы в указанном порядке;

передача данных из памяти и в память и из УВВ и в УBB;

ответы на внешние прерывания;

установка общей синхронизации и сигналов управления для всей системы.

Наиболее важные секции содержат различные регистры, АЛУ, дешифраторы команд, устройства управления и синхронизации, а также УВВ.

Микро- эвм 8086.

Это однокристальное устройство представляет собой удачное совмещение технологических и архитектурных достижений обеспечивает ей превышающей на порядок быстродействие 8-разрядных микропроцессоров. Он построен на транзисторах МДП что обеспечивает высокую плотность и сохранение быстродействия. Микро-ЭВМ содержит 2 процессора: обрабатывающий и адресный, работающие асинхронно. 16-разрядный обрабатывающий процессор АЛУ обеспечивает выполнение логических и арифметических операций над 8 и 16 разрядными числами. Адресный П обеспечивает опережающую выборку команд программы и формирование в блоке очередности последовательность команд байтов управления. Также содержит большое число регистров, упрощающих процесс выполнения операций, обеспечивающих при этом гибкость и высокое быстродействие. Содержит РОН, регистр указатель стека, индексные регистры, регистр состояния. Введение в адресный процесс систему сегментации и регистров переадресации, образующих сегментный регистровый файл позволяет расширить адресное пространство до 1Мб. Память может быть разделена на сегменты по 64 Кб.

Входящие: синхронизация, сброс, готовность, выбор структуры, анализ состояния, прерывание с повторением, прерывание без маскирования.

Выходящие: управление прямым доступом 0, …1, запрет захвата, состояние очередности 0, …1, код состояния 0, …1, память, ввод-вывод.

Блок интерфейсов: старший байт, состояние, адрес/данные.

Система команд состоит из 130 команд, включающих инструкции младших поколений М, что обеспечивает совместимость программных средств снизу-вверх.

Интерфейс. Определение интерфейса.

Для включения микропроцессора в любую микропроцессорную систему необходимо установить единые принципы и средства его сопряжения с остальными устройствами системы, т. е. унифицированный интерфейс.

Унифицированный интерфейс — совокупность правил, устанавливающих единые принципы взаимодействия устройств микропроцессорной системы. В состав интерфейса входят аппаратурные средства соединения устройств (разъем и связи), номенклатура и характер связей, программные средства, описывающие характер сигналов интерфейса и их временную диаграмму, а также описание электрофизических параметров сигналов.

Н а

рис. 4.4 представлена общая схема

взаимодействия микропроцессора МП с

устройствами ввода — вывода УВВ и ОЗУ

в микропроцессорной системе. Связь МП

с УВВ требует пяти групп связи,

обеспечиваемых через выводы корпуса.

По группе шин / передается код выбора

(адреса) устройства, по шине 2 — сигнал

управления считыванием—записью, по

шине 3 — сигнал запроса на прерывания,

шины 4 и 5 используются для передачи

данных от процессора к УВВ и от УВВ к

МП. Связь МП с ОЗУ также содержит пять

групп связей, которые необходимо

обеспечить через выводы корпуса МП. По

группе шин 6 передается адрес в ОЗУ, шина

7 нужна для управления чтением/записью,

по сигналам на шине 8 принимаются

команды в процессор, а шины 9 и 10

обеспечивают передачу данных из ОЗУ в

МП и обратно.

а

рис. 4.4 представлена общая схема

взаимодействия микропроцессора МП с

устройствами ввода — вывода УВВ и ОЗУ

в микропроцессорной системе. Связь МП

с УВВ требует пяти групп связи,

обеспечиваемых через выводы корпуса.

По группе шин / передается код выбора

(адреса) устройства, по шине 2 — сигнал

управления считыванием—записью, по

шине 3 — сигнал запроса на прерывания,

шины 4 и 5 используются для передачи

данных от процессора к УВВ и от УВВ к

МП. Связь МП с ОЗУ также содержит пять

групп связей, которые необходимо

обеспечить через выводы корпуса МП. По

группе шин 6 передается адрес в ОЗУ, шина

7 нужна для управления чтением/записью,

по сигналам на шине 8 принимаются

команды в процессор, а шины 9 и 10

обеспечивают передачу данных из ОЗУ в

МП и обратно.