- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

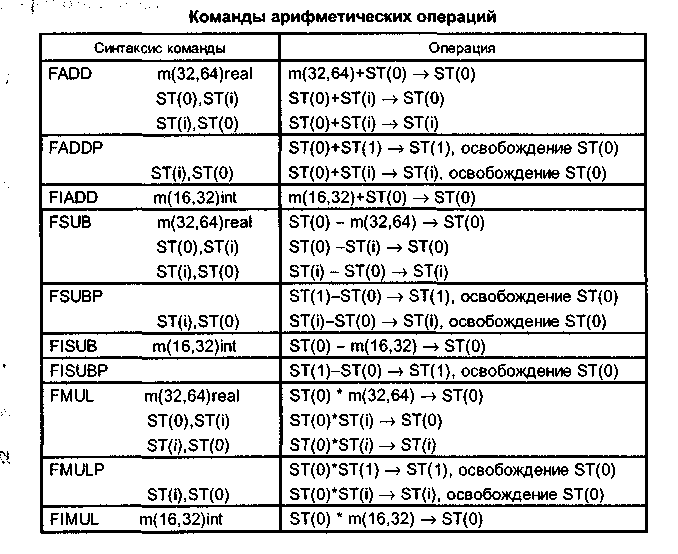

2.4.4. Команды арифметических операций

Команды этой группы обеспечивают выполнение арифметических операций сложения, вычитания, умножения, деления и ряда других (табл. 2.30).

Один из операндов всегда размещается в верхнем регистре арифметического стека ST(0), второй операнд выбирается из памяти или регистра стека ST(i), номер которого задается байтом MODRM. Формат выбираемого из памяти операнда ОТ, ДТ, ДВ, ЦС, КЦ определяется кодом операции. Результат операции размещается в регистрах арифметического стека ST(0) или ST(i).

После выполнения операций FADDP, FSUBP, FMULP, FDIVP вершина стека освобождается, т. е. для регистра ST(0) устанавливается значение tag = 11. Содержимое поля ТОР в регистре FPSR увеличивается на единицу, т. е. производится сдвиг вершины стека на один регистр вниз. Соответственно, значение номера i для регистра ST(i) уменьшается на единицу. Например, если операнд выбирается из регистра ST(3), то после выполнения операции и размещения результата в этот регистр его номер относительно новой вершины стека принимает значение ST(2).

Команды обратных операций FSUBR, FSUBRP, FDIVR, FDIVRP обеспечивают изменение порядка следования операндов при вычитании и делении.

При выполнении операций над вещественными числами операндами могут служить ± О и ± L. В этих случаях формирование результатов арифметических операций производится в соответствии с табл. 2.31, где используются следующие обозначения:

Н, IE= 1 -устанавливается флаг недействительной операции IE = 1, результатом является код неопределенности, если значение маски IM = 1;

(±) - знак результата S устанавливается с помощью операции «Исключающее ИЛИ» над знаками операндов S1, S2, т. е. S = S1 (+) S2;

±0 при UE = 1 - результат +0 или -0 устанавливается при получении антипереполнения (UE = 1), если значение маски DM = 1;

*0 - знак устанавливается в зависимости от способа округления, заданного полем RC: +0 при RC = 00,10,11; -0 при RC = 01.

При выполнении операций, вызывающих установку флагов IE = 1, UE = 1 или ZE = 1, реализуется прерывание, если флаги не маскированы. Если же соответствующие маски имеют значение IM = 1, UM = 1, или ZM = 1, то процессор продолжает выполнение программы, а результатами операций служат коды неопределенности (Н) при IE = 1, ±0 при UE-1, ±L при ZE = 1, согласно табл. 2.31.

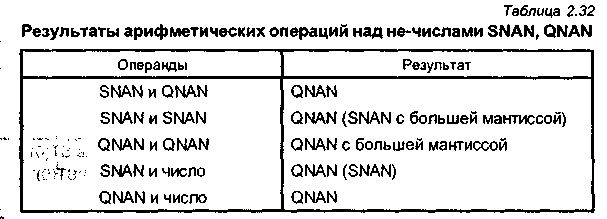

He-числа SNAN, QNAN также могут быть операндами при выполнении команд над вещественными числами. В этом случае результат арифметической операции определяется согласно табл. 2.32, где QNAN (SNAN) обозначает не число QNAN, полученное из SNAN путем установки единицы в старшем разряде мантиссы. Остальные разряды мантиссы при преобразовании SNAN в QNAN сохраняют свое значение.

Команда FPREM производит деление числа, расположенного в ST(0), на число в ST(1), остаток накапливается в регистре ST(0). Деление осуществляется путем последовательного вычитания, которое выполняется п раз -до тех пор, пока не будет получено ST(0) < ST(1).

При этом в регистре FPSR бит С2 принимает значение 0. Число вычитаний п определяется как частное ST(0)/ST(1), которое округляется до целого путем отбрасывания дробной части. Знак остатка устанавливается таким же, как знак делимого. Максимальное число выполняемых вычитаний ограничено п <- 64. Если 64 вычитаний недостаточно для получения ST(0)<ST(1), то в регистре FPSR устанавливается значение бита С2 = 1, а в регистре ST(0) сохраняется частичный остаток. Точный остаток получается при повторных выполнениях команды FPREM до получения С2 = 0. После выполнения этой команды биты СО, С1, СЗ регистра FPSR содержат три младших разряда частного.

Команда FPREM1 также осуществляет вычисление частичного остатка. Отличие от команды FPREM состоит в том, что число вычитаний при выполнении команды FPREM1 определяется в соответствии со стандартом IEEE 754, как частное ST(0)/ST(1), которое округляется до ближайшего целого. Получаемый остаток в этом случае будет не больше половины делителя.

Команда FSQRT вычисляет квадратный корень из содержимого ST(0) и размещает его в этом же регистре.

Команды FABS и FCHS изменяют знак числа в регистре ST(0), чтобы получить абсолютное значение этого числа (команда FABS) или число с противоположным знаком (команда FCHS).

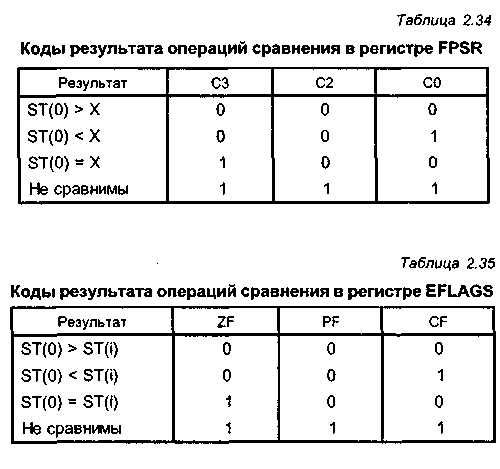

КОМАНДЫ СРАВНЕНИЯ

К этой группе относятся команды (табл. 2.33), выполняющие сравнение двух операндов с плавающей точкой и установкой соответствующих битов в регистре состояния FPSR или регистре EFIAGS, а также команды тестирования (сравнение операнда с нулем) и анализа содержимого регистра ST(0).

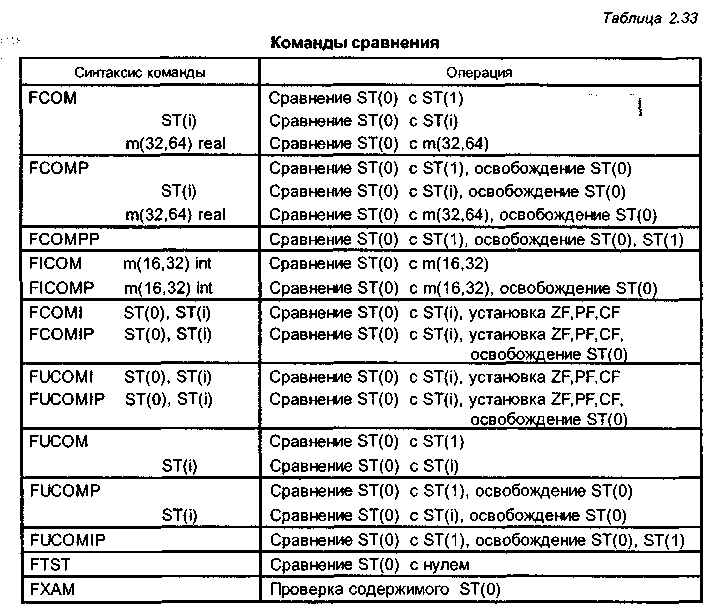

Команды FCOM, FCOMP, FCOMPP производят сравнение вещественных чисел. При выполнении команды FCOMP после сравнения производится освобождение вершины стека - регистра ST(0), т. е. значение поля ТОР увеличивается на единицу, а бывший регистр ST(0) становится пустым. После сравнения содержимого двух верхних регистров стека ST(0) и ST(1) по команде FCOMPP освобождаются оба этих регистра. Команды FICOM, FICOMP выполняют аналогичные операции с целыми числами в формате ЦС (ml 6int) и КЦ (m32int). По результатам сравнения устанавливаются соответствующие значения битов СО, С1, СЗ в регистре FPSR согласно табл. 2.34. При этом проверяются типы сравниваемых операндов. Операнды считаются не сравнимыми, если один из них или оба являются не числами или представлены в неподдерживаемом (unsupported) формате. В этом случае фиксируется ошибка FPU типа #1 (недействительная операция) и реализуется исключение типа #MF («Ошибка FPU»), если в регистре FPCR бит маски IM = 0.

Команды FUCOM, FUCOMP, FUCOMPP выполняют такие же операции, как FCOM, FCOMP, FCOMPP, но не реализуют исключение при поступлении не чисел типа QNAN, позволяя текущей программе обрабатывать неупорядоченные (unordered) операнды.

Команды FCOMI, FCOMIP, FUCOMIP, FUCOMIP производят сравнение операндов, размещенных в регистрах ST(0), ST(1). При этом результаты сравнения представляются определенными значениями признаков ZF, PF, CF в регистре EFLAGS в соответствии с табл.2.35. После выполнения сравнения команды FCOMIP, FUCOMIP освобождают регистр ST(0). Команды FCOMI, FCOMIP реализуют исключение типа #MF при сравнении операндов, являющихся не числами, команды FUCOMI, FUCOMIP не вызывают исключения, позволяя сравнивать, таким образом, неупорядоченные (unordered) операнды.

Команды FUCOM, FUCOMP, FUCOMPP производят сравнение мантисс операндов. При этом допускается сравнение не чисел),и имеют единичные значения всех разрядов порядка). Если один или оба операнда являются не числами, то устанавливается значение бита С2 = 1, а биты СЗ и СО определяют соотношение между мантиссами в соответствии с табл. 2.34, где х = ST(1). Команда FUCOMP освобождает вершину стека - регистр ST(0), команда FUCOMPP-два верхних регистра стека -ST(0) и ST(1).

Команда FTST выполняет сравнение содержимого регистра ST(0) с нулем, устанавливая биты СЗ, С2, СО в регистре FPSR в соответствии с табл. 2.34, где х = 0.

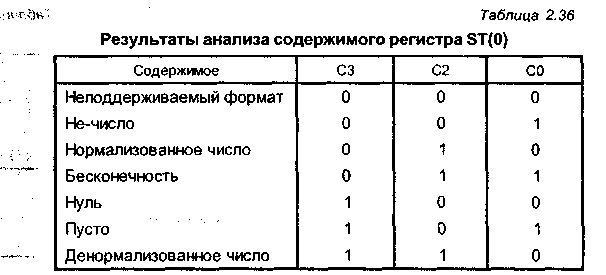

Команда FXAM производит анализ содержимого ST(0) и устанавливает соответствующие значения битов СО-СЗ в регистре FPSR. При этом бит С1 принимает значения знака, а разряды СО, С2, СЗ определяют содержимое ST(0) в соответствии с табл. 2.36.