- •Раздел 4. Микропроцессоры семейства intel

- •Тема 4.1. Модели мп семейства intel и их сравнительная характеристика

- •Тема 4.2. Организация однокристальных 16-разрядных микропроцессоров

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Организация памяти.

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Сегментные регистры (cs, ds, ss, es),

- •Регистр адреса командIp,

- •Регистр флагов f.

- •Регистр флагов f

- •3. Организация памяти.

- •Тема 4.3. Система команд мп, форматы команд, классификация команд, способы адресации

- •Формат команды микропроцессора

- •Режимы адресации операндов

- •Тема 4.4. Система прерываний микроЭвм

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Механизм обработки прерываний

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Аппаратные прерывания

- •Программные прерывания

- •Исключительные ситуации

- •Механизм обработки прерываний

- •Тема 4.5. Сопроцессоры

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Тема 4.6. Архитектура 32-разрядных мп

- •Регистровая структура мп 80486

- •Типы данных 32-разрядных мп

- •Система команд, форматы команд и способы адресации мп 80486

- •Тема 4.7. Реальный режим работы мп

- •Тема 4.8. Защищенный режим работы мп

- •Дескрипторы сегментов и их таблицы. Типы сегментов и дескрипторов

- •Страничная и сегментная организация памяти. Преобразование адресов в защищенном режиме

- •Средства поддержки мультизадачности и защиты. Механизмы защиты

- •Тема 4.9. Виртуальный режим работы мп

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Сегментно - страничное распределение

Раздел 4. Микропроцессоры семейства intel

Тема 4.1. Модели мп семейства intel и их сравнительная характеристика

Тема 4.2. Организация однокристальных 16-разрядных микропроцессоров

-

Стандартная архитектура 16-разрядного микропроцессора intel 8086.

-

Программная модель микропроцессора intel 8086.

-

Организация памяти.

-

Стандартная архитектура 16-разрядного микропроцессора intel 8086.

Микропроцессор INTEL 8086 – первое поколение 16-разрядных микропроцессоров. Микропроцессор INTEL 8086 представляет собой однокристальный 16-разрядный микропроцессор с мультиплексированной 20-разрядной магистралью адреса и 16-разрядной магистралью данных и рассчитан на работу в одно- и многопроцессорных системах. Тактовая частота – 5, 8 или 10 МГц. Кристалл микросхемы микропроцессора содержит 29000 транзисторов и потребляет 1,7 Вт от источника питания +5В.

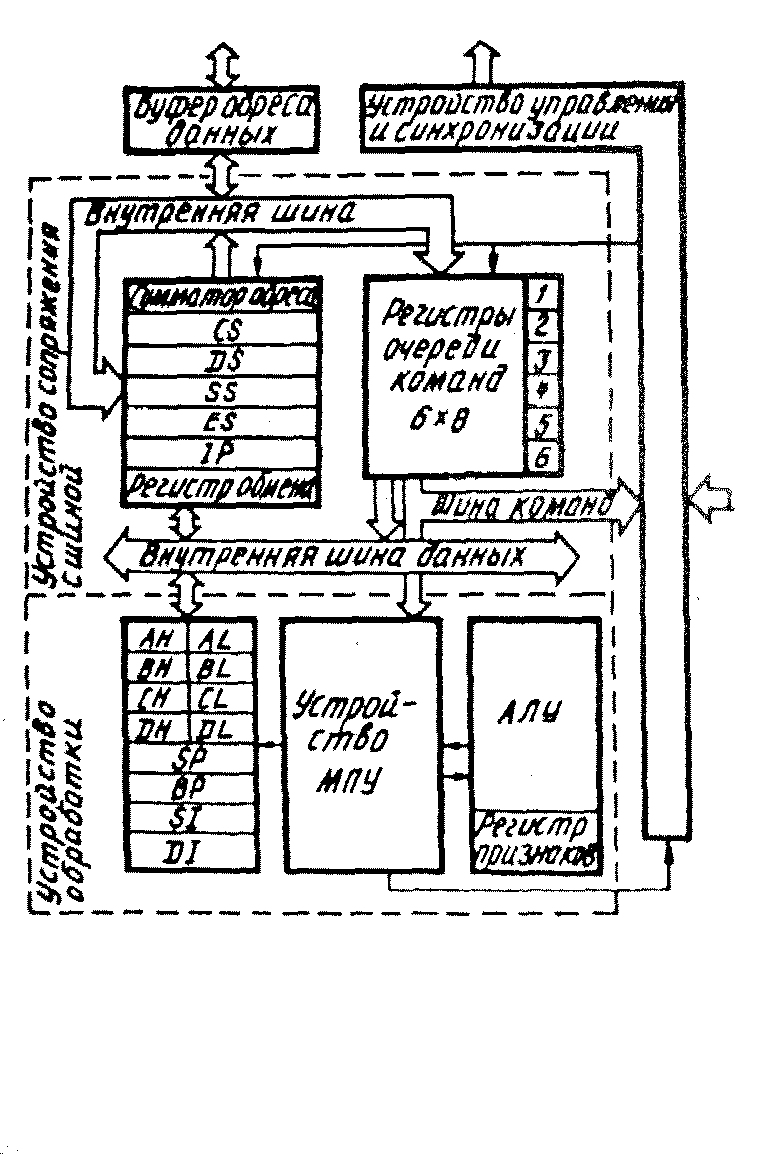

Внутренняя структура микропроцессора содержит две относительно независимые части (рисунок 1):

-

операционное устройство, реализующее заданные командой операции;

-

устройство шинного интерфейса, осуществляющее выборку команд из памяти, а также обращение к памяти и внешним устройствам для считывания операндов и записи результата.

Рисунок 1 - Структурная схема микропроцессора INTEL 8086

Оба устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и выполнения команд. Это повышает быстродействие микропроцессора. Пока операционное устройство занято выполнением очередной команды программы, устройство шинного интерфейса подготавливает следующую команду и данные для ее выполнения. Операционное устройство не имеет непосредственной связи с внешними магистралями микропроцессора, все пересылки команд и данных для операционного устройства выполняет устройство шинного интерфейса. В микропроцессоре INTEL 8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы выполнения и выборки из памяти кодов последующих команд. Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с внешней шиной – выставляет адреса, считывает коды команд и операнды, записывает результаты вычислений в память или устройства ввода-вывода.

Операционное устройство состоит из

-

РОН, предназначенных для хранения данных и адресной информации,

-

АЛУ,

-

регистра флагов,

-

схемы управления и синхронизации, которая дешифрирует коды команд и генерирует управляющие сигналы для всех блоков схемы микропроцессора.

Шинный интерфейс состоит

-

регистра очереди команд,

-

сегментных регистров,

-

регистра указателя адреса команды,

-

сумматора адресов,

-

буферов, обеспечивающих связь с шиной.

Интерфейсная часть микропроцессора служит для связи и согласования микропроцессора с системной шиной микроЭВМ, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Устройство шинного интерфейса микропроцессора предназначено для:

-

выборки команд из памяти и записи их в очередь команд,

-

чтения операндов из памяти или регистров контроллеров ввода-вывода,

-

записи результатов выполнения команд в память или регистры контроллеров ввода-вывода,

-

формирование 20-разрядного физического адреса ячейки памяти.

Шинный интерфейс выполняет операции обмена между микропроцессором, памятью и устройствами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку кодов очередных команд из памяти. В микропроцессоре организован конвейерный метод выполнения команд. Для создания конвейера используется регистр очереди команд (РОК) размером 6 байт, что соответствует максимально длинному формату команды. Команды поступают в РОК в той последовательности, в которой они записаны в программе. Когда операционное устройство выполняет команды перехода, передачи управления, обработки запросов прерывания, шинный интерфейс сбрасывает очередь команд, выбирает команду по новому адресу, передает ее в операционное устройство, а затем начинает заполнение очереди команд заново.

Если команда требует обращения к памяти или порту ввода-вывода, то шинный интерфейс приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными. Когда шинный интерфейс не занят выборкой команды, он удовлетворяет запрос немедленно; в противном случае операционное устройство ожидает завершения текущего цикла шины. Циклом шины называют обращение к ячейке памяти или к внешнему устройству.

Из РОК код операции команды передается на дешифрацию в устройство микропрограммного управления. После дешифрации, устройство микропрограммного управления вырабатывает соответствующую последовательность микрокоманд, управляющую выполнением текущей операции.

Блок микропрограммного управления входит в состав управляющего устройства микропроцессора и реализует программирование микропроцессора на микрокомандном уровне.

Устройство управления и синхронизации микропроцессора в соответствии с дешифрированными кодами команд и внешними управляющими сигналами генерирует управляющие сигналы для всех блоков микропроцессорной системы. Синхронизация работы микропроцессорной БИС осуществляется импульсами внешнего тактового генератора.