- •Санкт-Петербургский Государственный Технический Университет

- •Санкт-Петербург

- •1. Электрические сигналы и их модели

- •1.1. Вводная часть

- •1.2. Аналоговые и цифровые сигналы

- •1.3. Основные характеристики Электрических сигналов

- •1.3.1. Частотный спектр сигналов.

- •1.3.2. Временные характеристики сигналов

- •Глава вторая

- •2. Основные положения теории электрических и магнитных цепей

- •2.1. Электрические цепи. Схемные и математические модели

- •2.1.1. Законы теории электрических цепей

- •Глава третья

- •3. ТЕоретические основы электронных цепей.

- •3.1. Основные характеристики и параметры электронных компонент и систем

- •3.2. Амплитудно-частотная характеристика систем.

- •3.3.Теоретическое обоснование процедуры проектирования электронных устройств.

- •3.4. Связь качества электронных устройств с относительной чувствительностью характеристик к изменению параметров элементов

- •В частотную область уравнение (12) переводят с помощью преобразования Фурье формально заменяя оператор s на jω

- •3.4.1. Качество систем и принципы их построения

- •3.4.3. Связь функции относительной чувствительности с запасом

- •3.5. Структурный метод повышения качества систем

- •3.6.Основные положения теории графов

- •3.6.1. Типы графов и их элементы

- •3.6.2. Изоморфизм графов

- •3.6.3.Синтез графов.

- •3.6.3. Методика синтеза графа по смежностно-степенным таблицам .

- •Глава четвёртая

- •4. Источники питания электронных схем

- •4.1. Функциональный аспект.

- •4.2. Магнитные цепи

- •4.3. Структурный аспект. Принципы построения выпрямителей.

- •4.5.Полупроводниковый p-n переход и полупроводниковые выпрямительные диоды

- •4.6. Силовые выпрямители

- •4.7.Стабилитроны и их применение в параметрических стабилизаторах

- •4.8. Схемы диодных ограничителей

- •4.9.Специальные типы диодов

- •4.9.1.Модели светодиодов и фотодиодов и их применение

- •4.9.2.Диоды Шоттки

- •Глава пять

- •5. Однокаскадные усилители

- •4.1. Принципы построения однокаскадных усилителей

- •5.2. Транзисторы и их модели

- •5.2.1.Биполярные транзисторы

- •4.4. Оконечные каскады усиления

- •5. 3. Операционные усилители (оу) постоянного тока

- •5.3.1. Способы построения дифференциального усилителя и его модели

- •5.3.2. Дифференциальный каскад с повышенным коэффициентом усиления

- •Глава шесть

- •6. Элементы цифрОвых устройств

- •6.1. Реализация основных логических функций и эталонов.

- •6.1.1. Диодные логические компоненты «и».

- •6.1.2. Диодно-транзисторный компонент «и-не»

- •6.1.3. Транзисторно-транзисторные компоненты (ттл) «и-не»

5.3.2. Дифференциальный каскад с повышенным коэффициентом усиления

Для повышения коэффициента усиления дифференциального каскада необходимо сделать возможно большими балластные сопротивления, включённые в коллекторы транзисторов. С этой целью включают источники тока вместо балластных сопротивлений. Дифференциальный каскад этого типа приведён на рис. 5.7, где источник тока I0 создает в транзисторе T3 ток эмиттеров T1 и T2. Выходное сопротивление дифференциального каскада с одинаковыми источниками тока (токовым зеркалом) на транзисторах Т5 и Т6 приближается к rк*/2. Отсюда возникает потребность в усилителе тока на транзисторе T8, имеющем большое входное сопротивление. С помощью резистора Rcм осуществляют балансировку параметров транзисторов T5 и T6, устраняющую их технологический разброс.

Рис.5.7

Рассмотрим более подробно действие усилителя по схеме рис. 5.7. Когда на входе действует сигнал ΔUc , то он преобразуется транзисторами T1 и T2 в приращения их коллекторных токов соответственно ΔI и -ΔI. Приращение тока ΔI передается токовым зеркалом в коллектор транзистора T6. Через выходной узел дифференциального каскада идет ток базы T8 :

ΔIб8= Ik2-Ik6=I0/2- ΔI-(I0/2+ ΔI)=-2ΔI.

Таким образом, токовое зеркало позволило перейти от выходного сигнала дифференциального каскада, снимаемого с коллекторов транзисторов T1 и T2, к выходному, снимаемому с одного коллектора без потери в коэффициенте усиления.

Покажем, что синфазный сигнал токовым зеркалом подавляется. В самом деле, синфазный сигнал приведет к равным токам коллекторов T1 и T2, а ток базы ΔIб8= I0/2- ΔI-(I0/2+ ΔI)=0. Отметим в связи с этим, что одинаковая нагрузка (тока базы транзисторов T7 и T8) левого и правого плеч дифференциального каскада способствует повышению коэффициента ослабления синфазного сигнала. Следовательно, желательно выполнить Rэ3=Rэ4.

Коэффициент усиления дифференциального каскада с учетом Rс =0 и Rбал≈rк*>>Rн дается выражением (5.1):

Ku≈-h21Rн/h11. (5.7)

Сопротивлением нагрузки в рассматриваемом каскаде является входное сопротивление усилителя тока: Rн = Rвх ≈(h21+1) Rэ4. После подстановки в (5.7) этого значения находим

Ku≈-h21(h21+1) Rэ4 /h11. (5.8)

Несложно выполнить неравенство Rэ4> h11, необходимое для повышения коэффициента усиления каскада. Пусть h21=102, тогда Ku >104, что позволяет уже для большинства применений не производить дальнейшего увеличения Ku Однако усиление тока выполнить необходимо для получения универсального усилителя. Кроме того, следует изменить постоянный потенциал выходного напряжения так, чтобы выполнялось Uвых=0 при Uc=0. Соответствующую схему рассмотрим в разделе, описывающем операционные усилители.

Глава шесть

6. Элементы цифрОвых устройств

6.1. Реализация основных логических функций и эталонов.

6.1.1. Диодные логические компоненты «и».

В настоящее

время в цифровой

технике элементами

обычно считают

устройства, которые выполняют

основные логические операции

типа И, ИЛИ, И-НЕ, ИЛИ-НЕ. в

двоичной логике входные и выходные

сигналы этих элементов принимают два

значения, соответствующих истинному

высказыванию (его для краткости и

возможности применить математическую

логику обозначают 1) и ложному (его

обозначают 0). В электронных схемах

измеряемыми и наблюдаемыми переменными

чаще всего являются напряжения и токи.

Поэтому в пособии соотнесём логической

единице высокий уровень напряжения

![]() ,

а логическому нулю низкий уровень

напряжения

,

а логическому нулю низкий уровень

напряжения

![]() .

Это отношение соответствует так

называемой положительной

логике. В нижнем индексе

обозначения напряжений поставлены

точки, так как вместо них подставляются

названия узлов электронной цепи или

сокращённое название напряжения в этом

узле.

.

Это отношение соответствует так

называемой положительной

логике. В нижнем индексе

обозначения напряжений поставлены

точки, так как вместо них подставляются

названия узлов электронной цепи или

сокращённое название напряжения в этом

узле.

Конечно, в отличие от логических

переменных, имеющих всего два значения,

реальные напряжения

![]() и

и

![]() имеют некоторое множество значений,

границы которых должны чётко соблюдаться.

Это необходимо для того, чтобы логический

элемент не создавал ошибочных сигналов

от воздействия внешних электромагнитных

помех, при изменении напряжений питания

в заданных диапазонах, при изменении

температуры окружающей среды и т.д.

Разность между минимальным значением

имеют некоторое множество значений,

границы которых должны чётко соблюдаться.

Это необходимо для того, чтобы логический

элемент не создавал ошибочных сигналов

от воздействия внешних электромагнитных

помех, при изменении напряжений питания

в заданных диапазонах, при изменении

температуры окружающей среды и т.д.

Разность между минимальным значением

![]() и максимальным значением

и максимальным значением

![]() на входе логического элемента определяет

его помехоустойчивость, т.е. невосприимчивость

элемента к любым сигналам меньших этой

разности.

на входе логического элемента определяет

его помехоустойчивость, т.е. невосприимчивость

элемента к любым сигналам меньших этой

разности.

Теперь перейдём к более низкому этапу по иерархии в спиралевидной модели проектирования, в котором логический элемент будет рассматриваться как компонент, состоящий из элементов с более простыми функциями. Такими элементами будут резисторы, конденсаторы, диоды, транзисторы. Начинается проектирование с функционального аспекта.

Реальное проектирование невозможно строго изложить в рамках данного пособия, поэтому, следуя знаменитому французскому математику Джорджу Пойа, заменим строгий синтез правдоподобными рассуждениями, понимая правдоподобность как достаточно строгие но не полные выводы.

Итак, на входе и выходе логического

компонента должно быть в идеальном

случае только два существенно отличающихся

значения напряжения. В практике чаще

всего используют один источник питания

с напряжением Uп.

поэтому одно

значение напряжения (на выходе компонента),

соответствующее логической «1», примем

равным

![]() .

другое значение

напряжения на нагрузке, соответствующее

логическому «0», можно принять равным

.

другое значение

напряжения на нагрузке, соответствующее

логическому «0», можно принять равным

![]() .

.

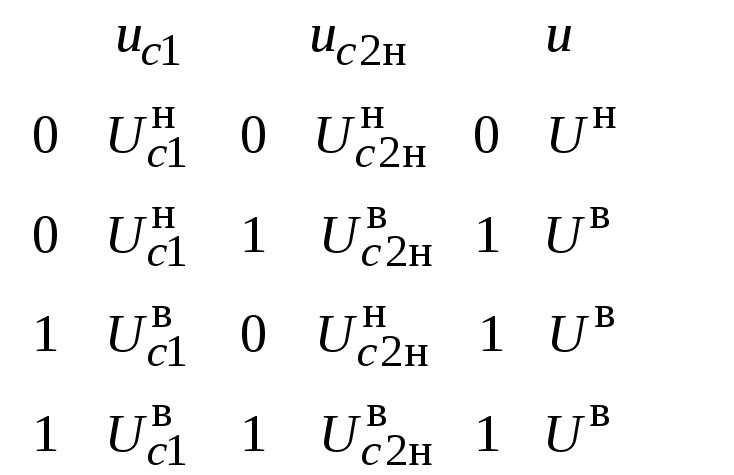

Таким образом, в результате синтеза логического компонента И должны быть получены соотношения, приведённые в таблице истинности 1. В ней «0» и «1» являются логическими переменными соответствующим вышеуказанным уровням напряжениям в устройстве.

Таблица 1 Таблица 2

сформулированное функциональное задание теперь позволяет перейти к структурному аспекту проектирования, который начинается с этапа выбора принципа построения логического компонента. В рамках этого этапа выбирают элементный базис, если он не указан в задании на проектирование.

Начнём проектирование этого этапа с выбора простейшего элементного базиса (из соображений экономических и достаточно хорошего уровня надёжности), т.е. будем использовать резисторы и диоды.

Анализ последнего столбца таблицы показывает, что напряжение питания попадает на нагрузку после ограничения его на низком уровне (желательно нулевом). Поэтому воспользуемся уже известными схемами ограничителей, построенных по параллельному или последовательному принципам. так как необходимо ограничивать напряжение на нагрузке в зависимости от, например, двух независимых сигналов, то необходимо на каждый сигнал включить параллельно по одному ограничителю, работающих на общую нагрузку.

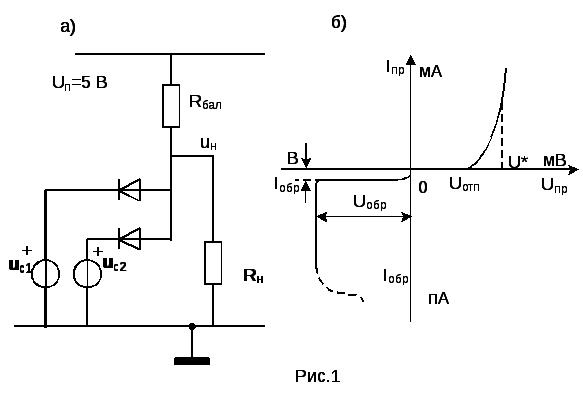

Итак, выбираем параллельный принцип построения ограничителей, у которых нагрузка и балластный резистор являются общими. в результате получается схема логического компонента (рис.1,а).

Проверим, удовлетворяет ли этот компонент поставленным условиям, выявим его достоинства и недостатки (функциональный аспект).

Безусловным достоинством схемы является минимально возможное число элементов. Это особенно важно в случае большого числа входных сигналов, так как при этом будет на каждый вход добавляться ровно один диод.

Теперь определим напряжения на нагрузке

при разных значениях входных сигналов.

Если напряжения uc1=uc2=0,

то оба диода открыты. падения

напряжений на них одинаковы U*

(рис.1,б) и создают напряжение на нагрузке

![]() .

В комбинациях сигналов, при которых

хотя бы один из диодов имеет напряжение

равное нулю, на нагрузке будет оставаться

напряжение равное 0,7В. Если же напряжения

сигналов равны

.

В комбинациях сигналов, при которых

хотя бы один из диодов имеет напряжение

равное нулю, на нагрузке будет оставаться

напряжение равное 0,7В. Если же напряжения

сигналов равны

![]() ,

то напряжение на нагрузке будет

,

то напряжение на нагрузке будет

![]() .

.

Следовательно, первый недостаток

структуры логического компонента И

состоит в зависимости уровня его

напряжения

![]() от уровня напряжения сигнала

от уровня напряжения сигнала

![]() .

.

При входных сигналах

![]() оба диода будут заперты, а напряжение

на нагрузке будет определяться делителем

напряжения gбал,

gн:

оба диода будут заперты, а напряжение

на нагрузке будет определяться делителем

напряжения gбал,

gн:

Как видно из уравнения (1), для того чтобы

напряжение

![]() приближалось к Uп

, необходимо выполнить неравенство

приближалось к Uп

, необходимо выполнить неравенство

![]() (2)

(2)

но это может привести при некоторых

типах нагрузки, например в случае работы

компонента на открытый переход

эмиттер-база биполярного транзистора,

к увеличению мощности потребляемой

компонентом от источника питания и

повышение температуры кристалла. Отсюда

возникает ограничение на число логических

элементов, размещаемых на одном кристалле

(ограничения технологического

аспекта проектирования). В

результате получим второй недостаток

![]() <

<

![]() .

.

Однако если выход диодного логического элемента подсоединён к входу полевого транзистора с изолированным окислом затвором (МОП), то неравенство (2) легко выполнимо.

в статике входное сопротивление МОП транзистора составляет несколько сотен мегом. В динамике же через балластный резистор протекает ток заряда входного конденсатора транзистора МОП. несмотря на малую величину емкости конденсатора (0,1-1 пФ), он вместе с балластным резистором логического компонента будет определять время задержки переключения транзистора МОП.

Следовательно, сопротивление Rбал очень большим не должно быть при желании сохранить быстродействие или оно должно быть нелинейным. В этом случае в статическом состоянии сопротивление Rбал должно быть очень большим для уменьшения потребляемой энергии, а в момент переключения – стремящимся к нулю.

Чаще всего логические элементы работают

друг на друга, поэтому без развязывающих

транзисторных каскадов вышеприведённое

неравенство сохраняется для каждого

элемента. Отсюда возникает ограничение

на число последовательно соединённых

элементов из-за снижения помехоустойчивости

компонента по причине быстрого снижения

разности напряжений

![]() .

.

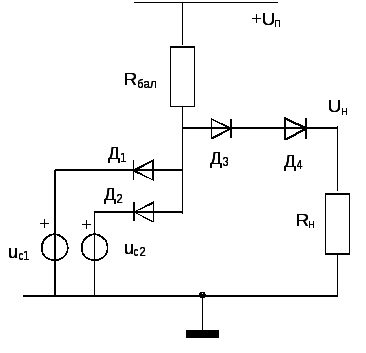

Устраним первый недостаток компонента, включив дополнительный ограничитель последовательно соединённый с нагрузкой (рис.2). В компоненте диоды Д3 и Д4 отпираются, если к ним приложено напряжение большее 2Uотп = 0,8 В.

Рис.2

Поэтому даже, если суммарное напряжение

будет равно

![]() ,

ток через нагрузку всё ещё не пойдёт. К

тому же, увеличение сопротивления

балластного резистора, снижает напряжение

,

ток через нагрузку всё ещё не пойдёт. К

тому же, увеличение сопротивления

балластного резистора, снижает напряжение

![]() на открытом диоде и потребляемую

компонентом мощность, а заодно несколько

увеличивает максимально допустимый

уровень

на открытом диоде и потребляемую

компонентом мощность, а заодно несколько

увеличивает максимально допустимый

уровень

![]() .

.

Осуществлять любые логические

преобразования сигналов с помощью

только элементов И невозможно. Поэтому

необходимо рассмотреть построение

других типов логических компонентов,

например реализующих операцию ИЛИ и

операцию НЕ. Начнём конструирование,

как и выше, с таблицы истинности (таблица

2) в той же положительной логике. Сравнение

таблиц 1 и 2 показывает, что при наличии

на одном из входов компонента И сигнала

низкого уровня

![]() на выходе компонента будет также сигнал

низкого уровня

на выходе компонента будет также сигнал

низкого уровня

![]() .

у компонента

ИЛИ наоборот: определяющим является

сигнал высокого уровня

.

у компонента

ИЛИ наоборот: определяющим является

сигнал высокого уровня

![]() .

Фактически, для построения логического

компонента ИЛИ можно применить схему,

изображённую на рис.2, применив свойство

дуальности двоичной логики. Следует

поменять на противоположные значения

уровней напряжения, принимаемых за

логический «0» и логическую «1», т.е.

поменять тип логики – положительную

на отрицательную:

.

Фактически, для построения логического

компонента ИЛИ можно применить схему,

изображённую на рис.2, применив свойство

дуальности двоичной логики. Следует

поменять на противоположные значения

уровней напряжения, принимаемых за

логический «0» и логическую «1», т.е.

поменять тип логики – положительную

на отрицательную:

![]() .

.

Конечно, применять два типа логики в одной системе не удобно. Поэтому на практике в интегральных системах применяют один тип логики, основанную на элементах И-НЕ или на элементах ИЛИ-НЕ.