курсовой проект / введение

.docВВЕДЕНИЕ

Задачей курсового проекта является развитие и закрепление навыков самостоятельной работы при решении конкретной задачи, подбора и разработки управляющей программы МП.

Цель курсового проекта: формирование навыков разработки и оформления текстовой и графической документации, разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

1 ТЕХНИЧЕСКОЕ ЗАДАНИЕ

Технические характеристики применяемого микропроцессора МП К1810ВМ86. Таким образом, индикатор обладает следующими параметрами:

- допустимый диапазон температур -10° С до + 70° С

- напряжение (питание индикатора шин осуществляется через соответствующие контакты вилки) + 5 В;

- максимальная тактовая частота 5МГц ;

- максимальная потребляемая мощность <\.15Вт.

Принципиальная схема процессора представлена в приложении 1.

Регистры D12 и D14 предназначены для сохранения адреса по сигналу ALE МП и данных по сигналу ALE35 ОЭВМ, регистр D17 - для сбора информации с управляющих выводов МП, регистры D19 и D20 - для подстановки кода команды и данных, системный контроллер D15 - для выработки управляющих сигналов в

максимальном режиме. На триггере D16 собрана схема управления готовностью в пошаговом режиме.

При установке эмулирующего МП К1810ВМ86 выключатель SA2 необходимо перевести в соответствующее положение. Индикатор шин удобно применять при настройке и ремонте устройств на базе МП К1810ВМ86, прогоняя «зашитую» в РПЗУ программу в автоматическом, пошаговом или полуавтоматическом режиме с остановом на контрольной точке.

Если неисправность заключается в «залипании» отдельных сигналов адреса, данных или управляющих сигналов, то ее удается локализировать за первые же несколько шагов в пошаговом режиме.

Микропроцессорный комплект БИС серии К1810 предназначен для построения, как простейших одноплатных микро ЭВМ общего назначения, так и мощных мультипроцессорных систем. Комплект используется в системах управления технологическими процессами, производственным оборудованием и промышленными работами, в контрольно - измерительных комплексах и в информационно -измерительных системах.

При разработке системы управления и обработки информации на основе комплекта К1810 полезно учитывать его программную и аппаратную совместимость с интерфейсными и контрольными БИС серии К580.

БИС К1810ВМ86 представляет собой однокристальный высокопроизводительный 16-разрядный микропроцессор, выполненный по усовершенствованной n-канальной МОП-технологии, позволившей получить среднее время задержки распространения сигналов на вентиль 2 не и обеспечить высокую функциональную плотность (29 тыс. транзисторов на кристалл).

Основные электрические и системные характеристики микропроцессора К1810ВМ86 при температуре окружающей среды (+25 ± 10)" С приведены ниже:

- объем адресуемой памяти - 1 Мбайт;

- разрядность адресной шины - 20;

- разрядность шины данных -16;

- число адресуемых устройств: ввода/вывода - 216/216;

- основных команд - 133.

Тип корпуса микросхемы КР580ИК80 - 2123.40 - 6 (7).

Температурный диапазон работы микросхем комплекта от -10 до + 70 ° С.

Требования к МП, как к элементу системы, определяются функциональным назначением всей системы. Оценка качества и выбор того или иного типа микропроцессора для данной области применения производится ориентировано с помощью критериев, учитывающих важность параметров для потребителя.

Микроконтроллер рассматривается одновременно, как вычислительное устройство, и как интегральная схема.

Как вычислительное устройство, микроконтроллер характеризуется следующими параметрами: разрядность обрабатываемых данных, способность к наращиванию разрядности, время выполнения команд, число команд, число внутренних регистров, наличие и объем стека, тип интерфейса, возможность обеспечения режима прерывания, объем адресуемой памяти, наличие канала прямого доступа к памяти, число входных и выходных шин и их разрядность.

Как интегральная схема, микроконтроллер характеризуется следующими критериями: тип базовой технологии, степень интеграции, число источников питания, их номиналы и допуски на номиналы, тип корпуса, помехоустойчивость, нагрузочная способность, устойчивость к механическим, климатическим и радиационным факторам.

Для комплексно-сравнительного анализа выбираются наиболее значимые критерии и проводится оценка микроконтроллерной системы.

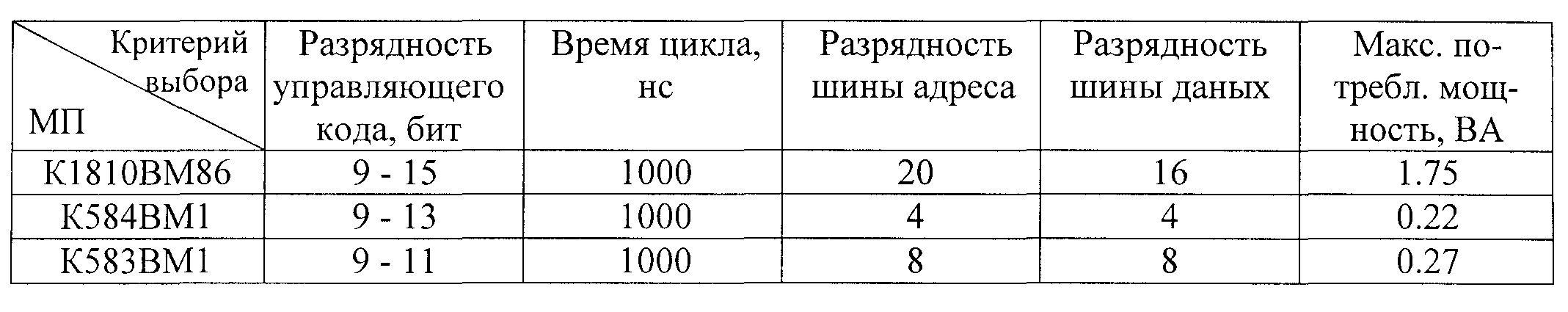

Для сравнения рассмотрим два аналога данного МП, это К584ВМ1 и К583ВМ1. Критерии всех трех микропроцессоров запишем в виде таблицы 1.

Таблица 1 - Основные критерии выбора микропроцессора

По приведенным данным можно сделать вывод о том, что микроконтроллер К1810ВМ86 более усовершенствованный, чем остальные.

Для разрабатываемой лабораторной установки микроконтроллер К1810ВМ86 является наиболее оптимальным.

4 ОПИСАНИЕ МИКРОПРОЦЕССОРА

4.1 Архитектура и режимы работы микропроцессора К1810ВМ86

Основные архитектурные особенности микросхемы К1810ВМ86, позволяющие больше чем на порядок повысить производительность систем, являются:

- мощная система команд с расширенными возможностями адресации памяти, включающая команды умножения, деления и обработки последовательностей байтов или слов;

- аппаратная реализация процесса совмещения операций выполнения и выборки команд;

- гибкая и мощная организация системы прерываний;

- аппаратная реализация некоторых механизмов взаимодействия нескольких процессов, упрощающая построение сложных мультипроцессорных систем.

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду.

Синхронизируется с тактовой частотой 25 МГЦ.

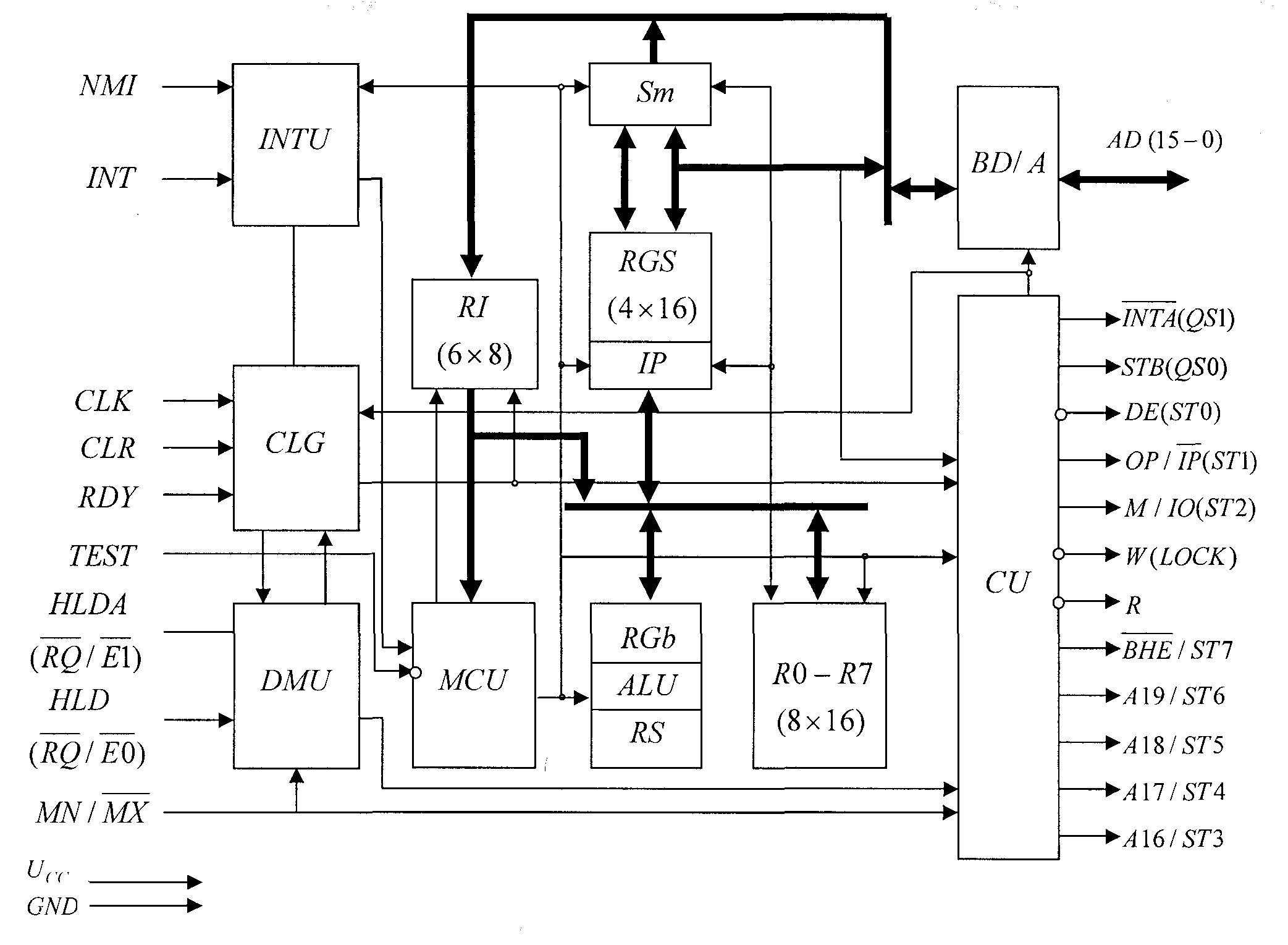

Структурная схема микропроцессора К1810ВМ86 представлена на рисунке 2. Она включает следующие устройства: арифметико-логическое устройство (ALU) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (RO—R7); микропрограммное устройство управления (MCU) для управления выполнением команд; схему управления доступом к магистрали (DMU); схему внутренней синхронизации (CLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (CU), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/данных (BD/A); указатель команд (IP), выполняющий функции программного счетчика; сегментные регистры (RGS), со-

держащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд готовых к исполнению.

Рисунок 2 - Структурная схема микропроцессора К1810ВМ86

Отличительной особенностью архитектуры микропроцессора К1810ВМ8(: является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). Упрощенная структурна* схема представляет МП в виде двух независимых устройств. УО декодирует к выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команд. Организация параллельной работы УО и УСК и уменьшение конфликтных ситуации

при обращении к памяти за счет применения очереди команд позволяет существенно повысить производительность систем на основе микропроцессора К1810ВМ86.

Регистровая модель микропроцессора К1810ВМ86 приведена на рисунке 3(а).

а)

в)

Рисунок 3 - Регистровая модель микропроцессора К1810ВМ86

Регистры CS, DS, SS и ES называются сегментными регистрами и используются при обращении к памяти для вычисления физических адресов ячеек. Основные назначения этих регистров следующие: регистр программного или кодового сегмента (CS) определяет текущий программный сегмент; содержимое регистра CS вместе с содержимым указателя команд (IP) задает адрес очередной команды выполняемой программы; регистр сегмента данных, или информационного сегмента (DS), используется в командах при обращении к данным; регистр стекового сегмента (SS) определяет текущий стековый сегмент и используется в командах обращения к стеку, при обработке подпрограмм и прерывании; регистр дополнительного сегмента (ES) обычно применяется как вспомогательный сегмент данных.

Регистры общего назначения АХ, ВХ, СХ и DX, называемые также регистрами данных, используются при выполнении арифметических и логических операций. Эти же регистры могут выполнять некоторые специальные функции, что и нашло отражение в их мнемонических обозначениях: АХ - аккумулятор, ВХ - базовый регистр, СХ - счетчик, DX - регистр данных. Эти регистры общего назначения допускают раздельную адресацию к их старшим (Н) и младшим (L) половинам и могут использоваться в виде набора 8-разрядных регистров.

Регистры общего назначения SP, BP, SI и DI называются адресными регистрами, так как в них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. В указателе стека (SP) и в указателе базы (ВР) содержаться относительные адреса в пределах стекового сегмента памяти, а в регистре индекса источника (SI) и регистре индекса приемника (DI) хранятся относительные адреса в пределах сегмента данных.

В пределах любого из сегментов емкостью в 64К байт обращение к операндам происходит с помощью 16-разрядного адреса смещения в сегменте. Этот адрес определяется способом адресации и называется также исполнительным адресом (ЕА). 20-разрядный физический адрес памяти (ADDR) формируется в сумматоре адреса (Sm) посредством сложения 16-раздного адреса смещения в сегменте

с 16-разрядным адресом в сегментном регистре, сдвинутым на четыре разряда влево (рисунок 3(6)).

Рассмотренные функции регистров микропроцессора К1810ВМ86 является основными и реализуются в командах по умолчанию. Дополнительные возможности использования регистров указываются при описании конкретных видов команд.

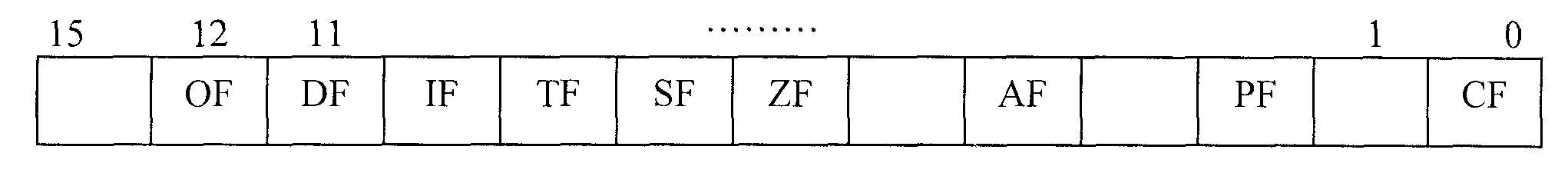

Регистр признаков или флагов (RS) состоит из одноразрядных регистров, фиксирующих состояние процессора и применяемых для управления его функционированием (рисунок 3(в)). Флаги CF, PF, AF, SF и ZF аналогичны флагам микропроцессора КР580ИК80А и характеризуют результат выполнения последней арифметической или логической операции. Флаг переполнения OF устанавливается в состояние 1 при переполнении, возникающем в результате арифметических операций над величинами со знаком. Флаги DF, IF и TF применяются для управления микропроцессором. Флаг направления DF служит для автоматического увеличения или уменьшения адреса при обработке последовательностей символов (имитация режимов автоинкрементной и автодекрементной адресации). Установка флага разрешения прерывания IF разрешает МП прием запроса прерывания на входе INT. Установка флага трассировки TF переводит МП в состояние прерывания после выполнения каждой команды, т.е. организует режим пошагового выполнения программ.

Микропроцессор К1810ВМ86 предназначен для использования как в простых однопроцессорных, так и в сложных мультипроцессорных системах управления и обработки информации. В связи с этим МП имеет специальный вывод MN/MX (рисунок 2) для задания минимального или максимального режимов функционирования. Каждый режим характеризуется некоторым набором управляющих сигналов, соответствующим сложности проектируемой системы. При подключении вывода MN/MX к выводу Ucc микропроцессор настраивается на работу в минимальном режиме, в котором все сигналы управления периферийными устройствами вырабатываются самим МП. При подключении вывода MN/MX к выводу

GND происходит изменение функций ряда управляющих сигналов и МП перенастраивается на работу в максимальном режиме. В этом режиме МП используется обычно с системным контроллером, генерирующим сигналы управления системой. Управляющие сигналы максимального режима работы на рисунке 2 заключены в круглые скобки.

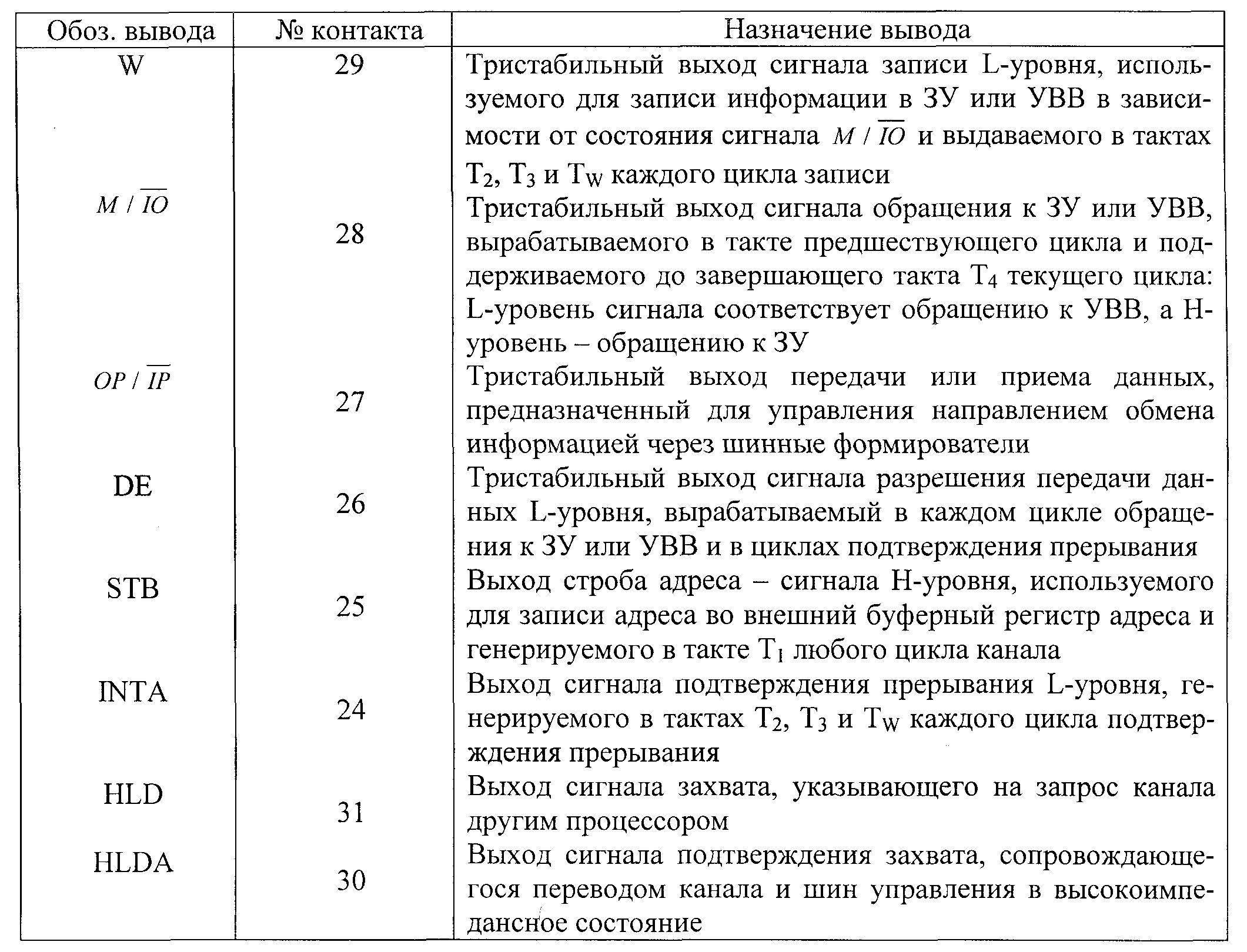

Таблица 2 - Описание выводов микропроцессора, общих для максимального и минимального режимов

Таблица 3 - Описание выводов МП, используемых для минимального режима

Таблица 4 - Описание выводов, используемых для максимального режима

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов, приведены в таблице 2. Назначения выводов, относящиеся только к минимальному режиму, даны в таблице 3, а только к максимальному в таблице 4. В максимальном режиме, как это видно из таблицы 4, МП использует лишь три вывода ST0 - ST2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируется сигналы, необходимые для организации работы МП в мультипроцессорных системах.

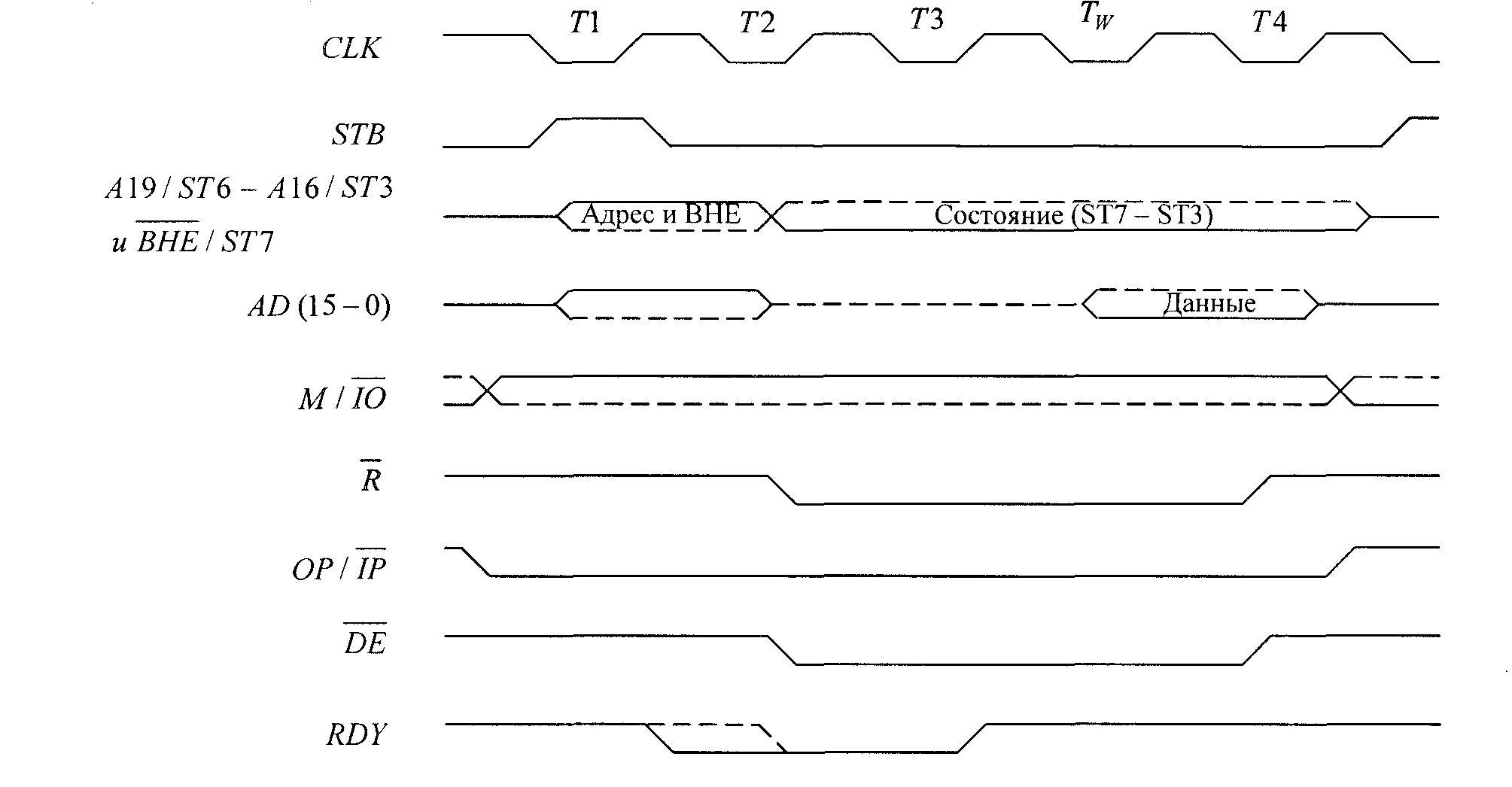

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала включает обычно выдачу адресов ЗУ или УВВ, данных, а также сигналов, сопровождающих процесс обмена, и состоит из четырех машинных тактов (Ть Т2, Т3, Т4). В такте Ti в канал выдается адрес ЗУ или УВВ. Обмен данными для цикла записи происходит в тактах Т2, Т3, Т4, а для цикла чтения в тактах Т3, Т4. Такт Т2 в цикле чтения используется для переключения МП из режима записи в режим чтения, а канал переводится в высокоимпе-дансное состояние. Для согласования с медленными УВВ или ЗУ с помощью RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Tw), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между относительными циклами канала могут вводиться холостые такты (Т5).

Временные диаграммы циклов чтения и записи для минимального режима представлены на рисунке 4. В цикле чтения (рисунок 4(а)) выдается сигнал чтения R, а также сигналы управления направлением обмена P0/IP и разрешением передачи данных DE. Сигнал DE разрешает шинным формирователям передать данные в МП. В цикле записи (рисунок 4(6)) сигнал DE выдается раньше, чем в цикле чтения, а выдача данных и сигнала записи W производится по переднему фронту в такте Т2. Для многих ЗУ и УВВ требуется постоянство адреса в течение всего цикла канала, поэтому в такте Т] каждого цикла выдается стробирующий сигнал STB, позволяющий зафиксировать адрес по заднему фронту сигнала STB.

а)

б)

Рисунок 4 - Временные диаграммы циклов чтения и записи для минимального режима

Сигналы состояния ST3, ST4 указывают сегментный регистр, используемый в текущем цикле канала для вычисления физического адреса ячейки памяти.

Три 16-разрядных регистра очереди команд (RI) микропроцессора обеспечивают временное хранение 6 байт очереди команд (рисунок 2). УО микропроцес-

сора при выполнении команды извлекает из очереди байт кода команды, не требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя ее, когда другие системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполнять вновь. В максимальном режиме МП передает информацию о состоянии очереди на выходы QSO и QS1. Эта информация используется внешними процессорами. Тип цикла канала для максимального режима определяется с помощью сигналов ST2, ST1 и ST0.

4.2 Система команд БИС К1810ВМ86

Система команд микропроцессора включает 133 базовые команды и позволяет обрабатывать как восьми-, так и шестнадцатиразрядные данные. Команды могут быть безоперандными, а также содержать один или два операнда. Длина команд может составлять от 1 до 6 байт. Код операции находится в первом байте команды, а остальные байты содержат информацию об адресах операндов. Чтобы различать операции над байтами или словами, в первом байте команды используется специальный разряд W. При W=l операции выполняются с шестнадцатиразрядными данными.

В микропроцессоре К1810ВМ86 используются почти все известные в настоящее время способы адресации: прямая, регистровая, регистровая косвенная, непосредственная, стековая, базовая, индексная, базово-индексная, относительная. Разнообразие способов адресации во многом связано с наличием большого набора регистров, применяемых для хранения данных и адресов. Наряду с основным использованием сегментных регистров для адресации операндов по правилу умолчания при выполнении многих команд возможны дополнительные варианты адресации.

Для операндов, расположенных в памяти, применяются следующие виды ад-

ресации: прямая адресация с 16-разрядным адресом; косвенная по содержимому некоторого базового регистра (базовая) с 8-разрядным или 16-разрядным смещением; косвенная по сумме содержимого базового регистра и регистра индекса (ба-зово-индексная) с 8-разрядным и 16-разрядным смещением.

При использовании индексной адресации операнд по умолчанию располагается в текущем сегменте данных, а при базово-индексной адресации операнд по умолчанию находится в сегменте, задаваемом базовым регистром.

Вид адресации в команде чаще всего задается байтом, следующим за кодом операции.

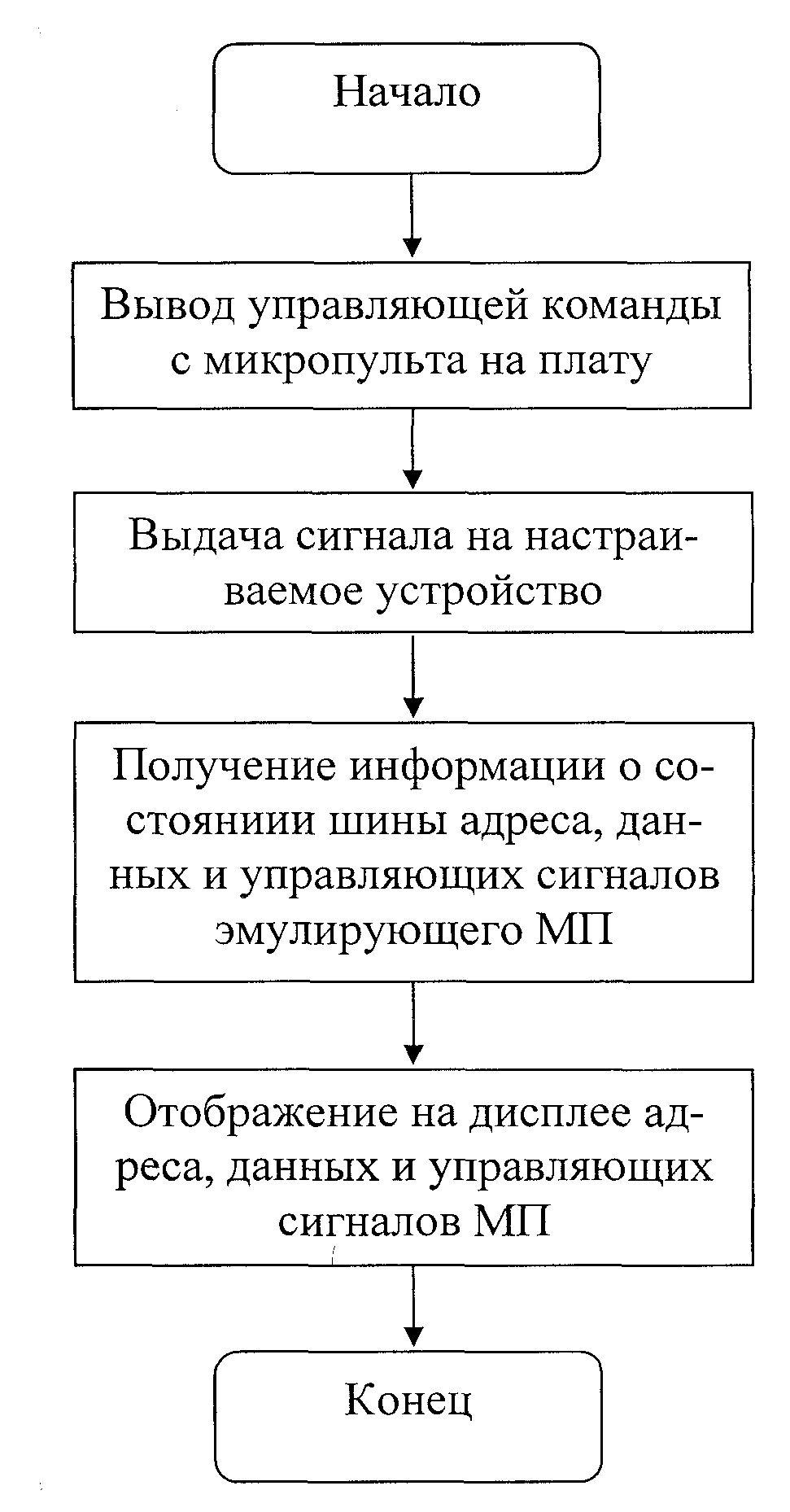

5 ОПИСАНИЕ БЛОК-СХЕМЫ РАБОТЫ ИНДИКАТОРА ШИН

Описывая алгоритм работы индикатора шин видно, что его удобно применять при настройке и ремонте устройств на базе МП К1810ВМ86, прогоняя «зашитую» в РПЗУ программу в автоматическом, пошаговом или полуавтоматическом режиме с остановом на контрольной точке. Управляющая команда поступает из микропульта на плату, затем подается на настраиваемое устройство. Затем идет обратная передача информации от настраиваемого устройства и отображается на дисплее микропульта.

ЗАКЛЮЧЕНИЕ

В данном курсовом проекте был рассмотрен индикатор шин, который применяется при настройке и ремонте устройств. Представлена его структурная схема, рассмотрены основные элементы, составляющие схему.

На основе анализа литературы проведено сравнение применяемого микропроцессора К1810ВМ86 с аналогами по основным характеристикам, что позволило сделать вывод, данный микропроцессор по всем параметрам подходит для данной системы.

Рассмотрена структурная схема микропроцессора, основные узлы составляющие ее.

Описана блок-схема работы индикатора шин.

ПРИЛОЖЕНИЕ

Приложение 1 - Принципиальная схема процессора

Микросхемы динамических ОЗУ

В микросхемах памяти динамического типа функции ЭП выполняет электрический конденсатор, образованный внутри МДП-структуры. Информация представляется в виде заряда: наличие заряда на конденсаторе соответствует логическому О, отсутствие — логической 1. Поскольку время сохранения конденсатором заряда ограничено, предусматривают периодическое восстановление (регенерацию) записанной информации. В этом состоит одна из отличительных особенностей динамических ОЗУ. Кроме того, для них необходима синхронизация, обеспечивающая требуемую последовательность включений и выключений функциональных узлов.

Для изготовления микросхем динамических ОЗУ в основном применяют я-МДП-технологию, которая позволяет повышать быстродействие и уровень интеграции микросхем, обеспечивать малые токи утечки и за этот счет увеличивать время сохранения заряда на запоминающем конденсаторе.

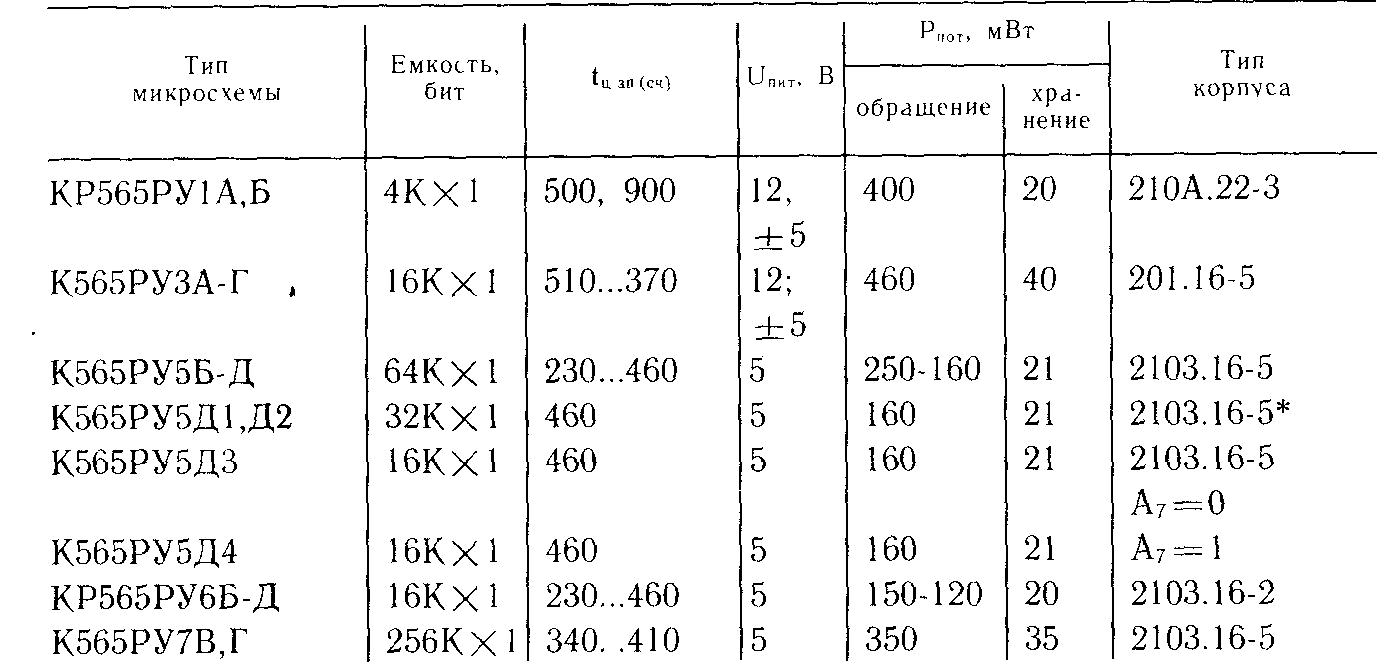

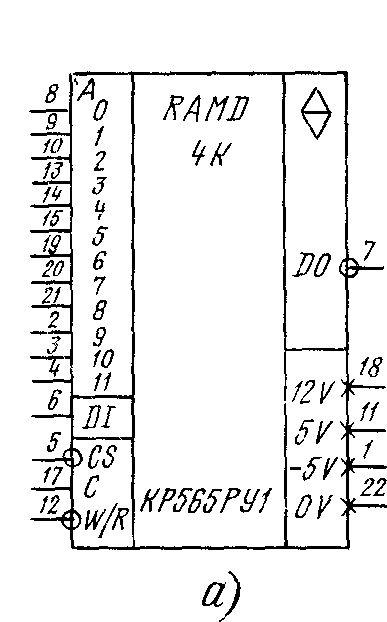

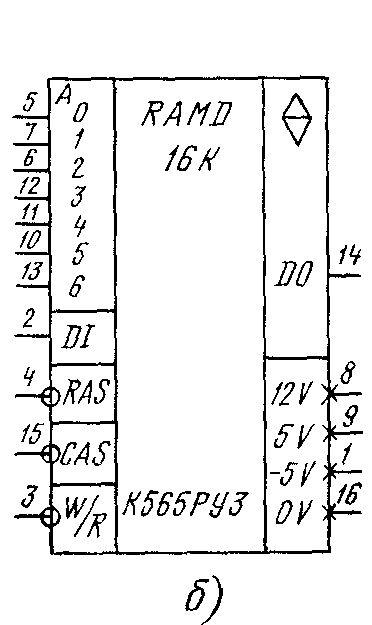

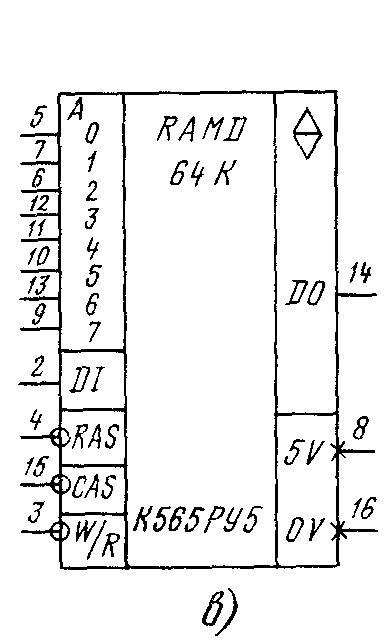

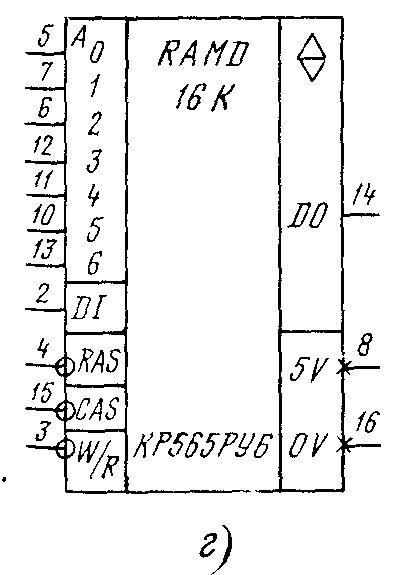

Микросхемы динамических ОЗУ отечественного производства представлены в основном серией К565. Она включает в свой состав ряд микросхем, отличающихся не только своими характеристиками, но и использованными в них структурными решениями. Характеристики микросхем динамических ОЗУ серии К565 приведены в табл. 2.11, а их условные графические изображения — на рис. 2.12.

Рассмотрим типичный вариант реализации динамического ОЗУ на примере микросхемы К565РУЗ информационной ем-

Таблица 2.11. Характеристики микросхем динамических ОЗУ

Рис. 2.12. Микросхемы памяти

серии К565

Рис 2 13 Структура микросхемы динамического ОЗУ

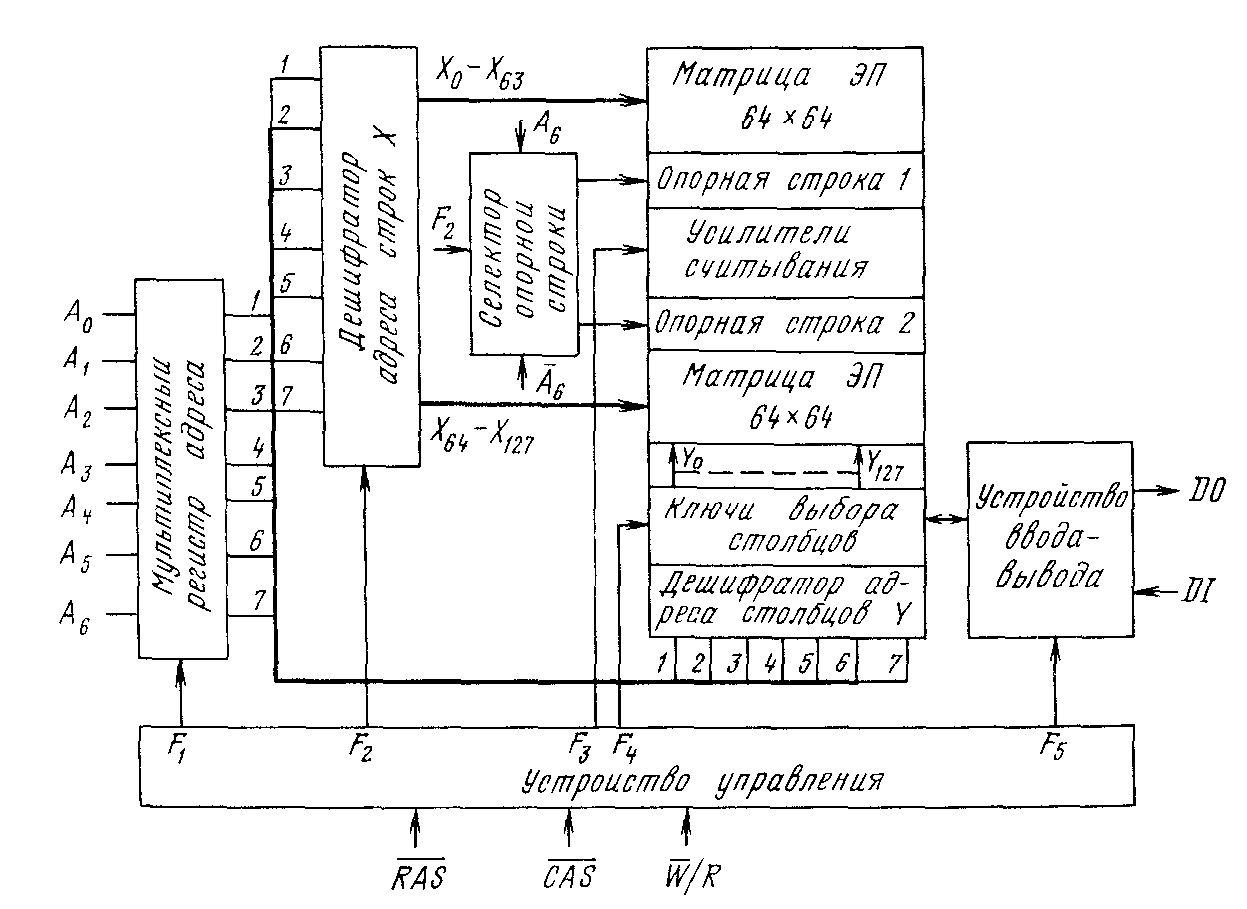

костью 16КХ1 бит. В ее структурную схему (рис. 2.13) входят выполненные в одном кремниевом кристалле матрица накопителя, содержащая 16 384 элементов памяти, расположенных на пересечениях 128 строк и 128 столбцов, 128 усилителей считывания и регенерации, дешифраторы строк и столбцов, устройство управления, устройство ввода-вывода и мультиплексный регистр адреса.

Матрица накопителя разделена на две части по 64X64 ЭП в каждой. Между ними размещены усилители, так что каждый столбец состоит из двух секций, подключенных к разным плечам усилителя (рис. 2.14).

Элемент памяти построен по однотранзисторной схеме и включает конденсатор С,, и транзистор VT,r Транзистор выполняет функции ключа: при сигнале на адресной шине строки Х,= 1 он открывается и соединяет конденсатор Сц с j-разрядной шиной. Предварительно в паузах между обращениями к накопителю емкости полушин Сш4 и СшВ заряжает источник напряжения Uo через открытые ключевые транзисторы VT5 и VT6. При обращении к накопителю эти транзисторы закрываются и изолируют полушины Aj и В, от источника напряжения Uo. Запоминающий конденсатор С,, выбранного ЭП подключается через открытый транзистор VT,, к полушине At и изменяет ее потенциал. Это изменение незначительно, так как емкость запоминающего конденсатора, равная 0,1...0,2 пФ, много меньше

Рис 2 14 Фрагмент разряда (столбца) микросхемы динамического ОЗУ

емкости шины. Поэтому для индикации малого изменения потенциала шины при считывании информации применен высокочувствительный дифференциальный усилитель триггер-ного типа на транзисторах VT1 — VT4, включенный в середину РШ, как показано на рис. 2.14.

Кроме массива ЭП и усилителей, матрица имеет в своей структуре опорные элементы (ЭО) по одному элементу в каждой полушине. Эти элементы в каждой половине матрицы составляют опорную строку (ОС). Опорный элемент построен аналогично запоминающему. Его назначение состоит в поддержании опорного напряжения Uo, с которым усилитель сравнивает потенциал полушины с выбранным ЭП и реагирует на получающуюся при сравнении разность потенциалов положительного и отрицательного знака в зависимости от считываемого уровня. Эта операция происходит следующим образом: если выбрана для обращения строка верхней полуматрицы X,, то сигнал А6 старшего разряда кода адреса строки коммутирует в селекторе опорной строки цепь через ключевой транзистор VTi2 для сигнала F2 к ОСг, расположенной в нижней полуматрице. Таким образом, в каждом из 128 столбцов к усилителю с разных сторон подключены ЭП и ЭО. Поскольку потенциал полушины с ЭП отличается от опорного, то в проводимости транзисторов разных плеч усилителя-триггера появляется асимметрия, которая при включении цепи его питания сигналом F3 вызывает опрокидывание триггера по преобладающему уровню. В итоге на выходах-входах А и В триггера формируются полные уровни 1 и 0. Тот из сигналов, который отражает считываемую информацию, в нашем примере на рис. 2.14 — сигнал с плеча А, коммутируется на вход устройства вывода через

ключевые транзисторы VT7, VT9 и VT10, открываемые сигналами А6, F4 и Yr Очевидно, считан может быть только один сигнал с выбранного дешифратором столбца: Y, = 1. У остальных столбцов ключи VT10 закрыты. Сигнал F4 зависит от наличия сигнала CAS: при отсутствии последнего он не формируется и ключ VT9 закрыт.

Сигнал на входе-выходе А триггера-усилителя выполняет также функцию восстановления уровня заряда запоминающего конденсатора С,,, т. е. функцию регенерации информации. Причем эта операция происходит во всех ЭП выбранной строки одновременно.

Таким образом, при каждом обращении к матрице для считывания информации автоматически осуществляется регенерация информации во всех ЭП, принадлежащих выбранной строке.

Для адресации 16К элементов памяти необходим 14-разрядный код, а у рассматриваемой микросхемы только семь адресных входов. С целью уменьшения числа необходимых выводов корпуса в микросхемах динамических ОЗУ код адреса вводят по частям: вначале семь младших разрядов Ао — А6, сопровождая их стробирующим сигналом RAS, затем семь старших разрядов А7 — А|3 со стробирующим сигналом CAS. Внутри микросхемы коды адреса строк и столбцов фиксируются на адресном регистре, затем дешифрируются и осуществляют выборку адресуемого ЭП

Для формирования внутренних сигналов Fi— F4, управляющих включением и выключением в определенной последовательности функциональных узлов микросхемы, в ее структуре предусмотрено устройство управления, для которого входными являются сигналы RAS, CAS, W/R.

Устройство ввода-вывода обеспечивает вывод одного бита информации DO в режиме считывания и ввод одного бита информации DI с ее фиксацией с помощью триггера-защелки в режиме записи. Во всех режимах, кроме режима считывания, выход принимает высокоомное (третье) состояние. Наличие у выхода высоко-омного состояния позволяет объединять информационные вход и выход при подключении микросхемы к общей информационной шине.