- •1 Анализ проектируемой системы

- •2 Разработка аппаратной части мпс

- •2.1 Блок центрального процессора

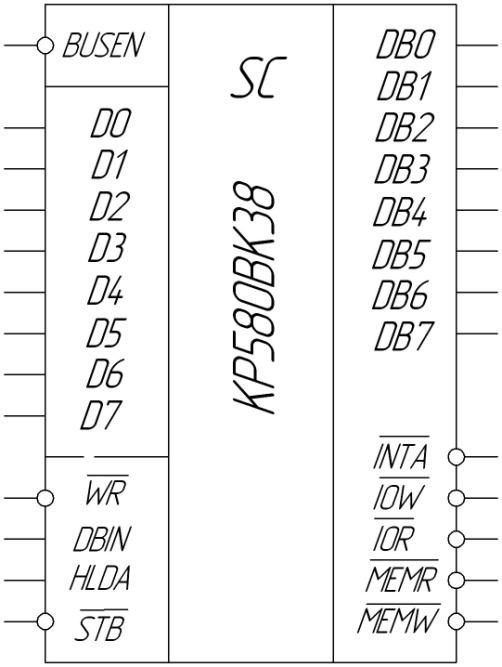

- •2.1.2 Бис системного контроллера кр580вк38

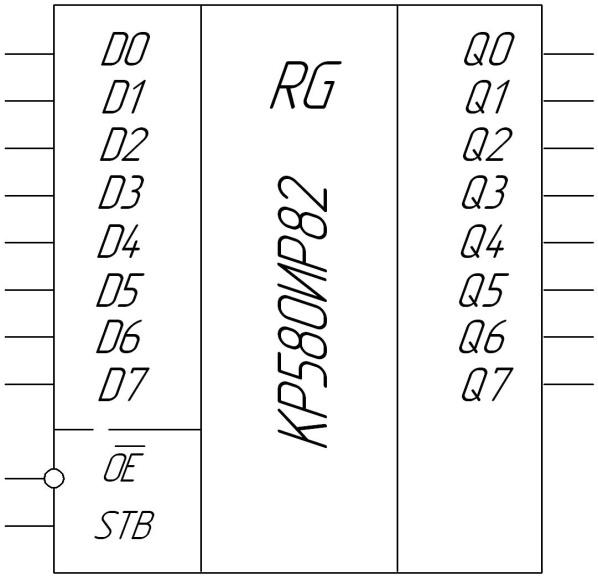

- •2.1.3 Бис буферных регистров кр580ир82

- •2.1.4 Бис тактового генератора кр580гф24

- •2.2 Модуль памяти

- •2.2.1.1 Расчет модуля озу

- •2.2.1.4 Выбор имс для логической схемы выбора страниц озу

- •2.2.2 Модуль пзу

- •2.2.2.4 Выбор имс для логической схемы выбора страниц пзу

- •2.3 Интерфейсный модуль

- •2.3.1 Организация параллельного ввода-вывода информации

- •2.3.2 Организация режима прерываний

- •2.3.2 Организация режима прямого доступа к памяти

- •3 Разработка программных средств мпс

- •3.1 Постановка и формулировка задачи

- •3.3 Разработка программы инициализации на языке Assembler

2.1.2 Бис системного контроллера кр580вк38

Таблица 2 – Назначение выводов КР580ВК38

|

Обозначение |

Ввод - вывод |

Назначение |

|

DB0-DB7 |

Вывод |

Разделенная шина данных |

|

INTA |

Ввод |

Сигнал готовности МП к обработке прерывания |

|

IOW |

Ввод |

Запись в УВВ |

|

IOR |

Ввод |

Чтение из УВВ |

|

MEMR |

Ввод |

Чтение памяти |

|

MEMW |

Ввод |

Запись в память |

|

STB |

Ввод |

Строб состояния |

|

HLDA |

Ввод |

Подтверждение захвата |

|

DBIN |

Ввод |

Прием |

|

WR |

Ввод |

Запись (выдача) |

|

D0-D7 |

Ввод |

Шина данных |

|

BUSEN |

Ввод |

Управление системной шиной |

Рисунок 2 – УГО ИМС КР580ВК38

Микросхема КР580ВК38 выполняет функцию системного контроллера и шинного формирователя, осуществляет формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ), обеспечивает прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Формирование

сигналов

![]() ,

,

![]() в данной микросхеме происходит

относительно сигнала

в данной микросхеме происходит

относительно сигнала

![]() “Строб

состояния”,

что позволяет при применении в

микропроцессорной системе микросхемы

КР580ВК38

использовать ЗУ и УВВ с более широким

диапазоном быстродействия. Двунаправленный

шинный формирователь осуществляет

буферирование 8-разрядной шины данных

и автоматический контроль направления

передачи данных.

“Строб

состояния”,

что позволяет при применении в

микропроцессорной системе микросхемы

КР580ВК38

использовать ЗУ и УВВ с более широким

диапазоном быстродействия. Двунаправленный

шинный формирователь осуществляет

буферирование 8-разрядной шины данных

и автоматический контроль направления

передачи данных.

Подключение системного контроллера к шине данных микропроцессора осуществляется с помощью двунаправленных выводов DO—D7, к системной шине—с помощью двунаправленных выводов DBO—DB7.

При необходимости с помощью сигнала BUSEN “Управление системной шиной” выводы DBO—DB7 системного контроллера могут быть переведены в состояние “Выключено”.

2.1.3 Бис буферных регистров кр580ир82

Таблица 3 – Назначение выводов КР580ИР82

|

Обозначение |

Ввод - вывод |

Назначение |

|

Q0—Q7 |

Ввод |

Входы регистра |

|

STB |

Ввод |

Строб |

|

___ ОЕ |

Ввод |

Разрешение выхода |

|

DO-D7 |

Вывод |

Выходы регистра |

|

U СС |

Вывод |

|

|

GND |

Вывод |

Земля |

Рисунок 3 – УГО ИМС КР580ИР82

Микросхема 8-разрядного адресного регистра, предназначенная для связи микропроцессора с системной шиной; обладает повышенной нагрузочной способностью. Микросхема КР580ИР82 - восьмиразрядный D-регистр с "защелкой" без инверсии и с тремя состояниями на выходе.

Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления.

В зависимости от состояния сигнала строба STB микросхемы могут работать в двух режимах: в режиме шинного формирователя или в режиме хранения. При высоком уровне сигнала STB и низком сигнале ОЕ микросхема работает в режиме шинного формирователя: информация на выходах Q повторяется или инвертируется по отношению к входной информации. При переходе сигнала STB из состояния высокого уровня в низкий происходит "защелкивание" передаваемой информации во внутреннем триггере, и она сохраняется до тех пор, пока на входе STВ присутствует напряжение низкого уровня.

При переходе сигнала ОЕ в состояние высокого уровня все выходы Q переходят в высокоомное состояние независимо от входных сигналов STB и Q. При возвращении сигнала ОЕ в состояние низкого уровня выходы Q переходят в состояние, соответствующее внутренним триггерам.

При обращении к внешнему устройству микропроцессор в начальный период цикла выполнения микрокоманды выдает на местную шину адрес этого устройства, который через системную шину передается необходимым числом регистров микросхемы.