Сафоненко ЗУ

.docxМинистерство образования и науки Российской Федерации

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ МЭИ

Кафедра ВМСиС

ЛАБОРАТОРНАЯ РАБОТА № 4

по дисциплине

«Современные методы проектирования цифровых систем»

Тема: «Проектирование микросхемы памяти»

Выполнил: Сафоненко Д.П

Группа: А-07м-16

Москва, 2016

Выполнение работы

-

Создание текстового описания модуля проекта на языке VHDL:

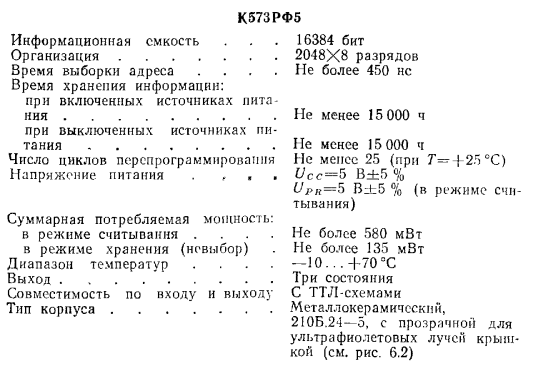

1.1) Описание микросхемы памяти КР573РФ5

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.CONV_INTEGER;

use IEEE.STD_LOGIC_ARITH.CONV_STD_LOGIC_VECTOR;

entity k573rf5 is

generic (

-- Динамические параметры микросхемы

t_aa:time:=450 ns; -- Время выборки адреса

t_cs:time:=450 ns; -- Время выбора

t_aceo:time:=150 ns; -- Время выборки сигнала разрешения по выходу

t_dis_cs:time:=120 ns; -- Время восстановления высокого сопротивления после сигнала CS

t_dis_ceo:time:=120 ns; -- Время восстановления высокого сопротивления после сигнала CEO

-- Параметры микросхемы

A_WIDTH:integer:=11; -- Ширина шины адреса

MEM_WORDS:integer:=2048; -- Количество слов

MEM_WLENGTH:integer:=8 -- Количество разрядов в слове

);

-- Выводы микросхемы

Port ( A : in STD_LOGIC_VECTOR (A_WIDTH-1 downto 0);

CS : in STD_LOGIC;

CEO : in STD_LOGIC;

DO : out STD_LOGIC_VECTOR (MEM_WLENGTH-1 downto 0):=(others=>'Z')

);

end k573rf5;

architecture Behavioral of k573rf5 is

type mem is array ( 0 to MEM_WORDS-1) of std_logic_vector(0 to MEM_WLENGTH-1);

shared variable pzu: mem;

shared variable upAfter: time:=0 ns;

shared variable downAfter: time:=0 ns;

shared variable badAdr: boolean:=false;

shared variable timeUp: time:=0 ns;

shared variable timeDown: time:=0 ns;

shared variable atest: time:=0 ns;

begin

------------------------начало-Заполнение-ПЗУ-------------

process

variable i: integer;

begin

for i in 0 to MEM_WORDS-1 loop

if (i mod 2=0) then

pzu(i):="H0H0H0H0";

else

pzu(i):="HHHH0000";

end if;

end loop;

DO<="HHHHHHHH";

wait;

end process;

----------------------конец-Заполнение-ПЗУ----------------

------------------------начало-Считывание------------------

process(CS,CEO,A)

begin

if (A'event)and(CEO='0')and(CS='0') then

upAfter := t_aa;

if(badAdr) then

DO<="XXXXXXXX" after upAfter;

else

DO<=pzu(conv_integer(A)) after upAfter;

timeUp:=now+upAfter;

end if;

end if;

if falling_edge(CS) then

if(CEO='0') then

upAfter := t_cs;

if(badAdr) then

DO<="XXXXXXXX" after upAfter;

else

DO<=pzu(conv_integer(A)) after upAfter;

timeUp:=now+upAfter;

end if;

end if;

end if;

if falling_edge(CEO) then

if(CS='0') then

if t_aceo-CEO'last_event > t_cs-CS'last_event then

upAfter := t_aceo;

else

upAfter := t_cs-(CS'last_event-CEO'last_event);

end if;

if(badAdr) then

--DO<="XXXXXXXX" after upAfter;

DO<="HHHHHHHH" after upAfter;

else

DO<=pzu(conv_integer(A)) after upAfter;

timeUp:=now+upAfter;

end if;

end if;

end if;

if rising_edge(CS) then

downAfter := t_dis_cs;

DO<=(others=>'H') after downAfter;

timeDown:=now+downAfter;

end if;

if rising_edge(CEO) then

downAfter := t_dis_ceo;

DO<=(others=>'H') after downAfter;

timeDown:=now+downAfter;

end if;

end process;

----------------конец-Считывание-----------------------------------------------

process(A)

begin

badAdr:=false;

for i in 0 to A_WIDTH - 1 loop

if A(i) /= '0' and A(i) /= '1' then

badAdr:=true;

end if;

end loop;

if badAdr and (now>1 ns) and (CS='0') then

report time'image(now) & ": Некорректные сигналы на адресных входах" severity ERROR;

end if;

if (CS='0')and(now>1 ns)and(CS'last_event < t_cs or CEO'last_event < t_aceo or atest+t_aa > now) then

report time'image(now) & ": Некорректная расстановка сигналов: Изменение адреса в момент считывания" severity ERROR;

end if;

atest := now;

end process;

-------------------------начало-Проверка--------------------------------

process(CS)

begin

if (now<timeUp)and(now>1 ns) and (CS='1') then

report time'image(now) & ": Некорректная расстановка сигналов: Изменение CS=1 в момент считывания" severity ERROR;

end if;

if (now<timeDown)and(now>1 ns) and (CS='0') then

report time'image(now) & ": Некорректная расстановка сигналов: Изменение CS=0 в момент отключения выходов" severity ERROR;

end if;

if badAdr and (now>1 ns) and (CS='0') then

report time'image(now) & ": Некорректные сигналы на адресных входах" severity ERROR;

end if;

end process;

process(CEO)

begin

if (now<timeUp)and(now>1 ns) and (CEO='1') then

report time'image(now) & ": Некорректная расстановка сигналов: Изменение CEO в момент считывания" severity ERROR;

end if;

if (now<timeDown)and(now>1 ns) and (CEO='0') then

report time'image(now) & ": Некорректная расстановка сигналов: Изменение CEO в момент отключения выходов" severity ERROR;

end if;

end process;

------------------конец-Проверка-----------------------------------------------

end Behavioral;

2) Создание тестирующей программы (Test Bench)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY TBZU IS

END TBZU;

ARCHITECTURE behavior OF TBZU IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT k573rf5

PORT(

A : IN std_logic_vector(10 downto 0);

CS : IN std_logic;

CEO : IN std_logic;

DO : OUT std_logic_vector(7 downto 0)

);

END COMPONENT;

--Inputs

signal A : std_logic_vector(10 downto 0) := (others => '0');

signal CS : std_logic := '0';

signal CEO : std_logic := '0';

--Outputs

signal DO : std_logic_vector(7 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

-- constant <clock>_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: k573rf5 PORT MAP (

A => A,

CS => CS,

CEO => CEO,

DO => DO

);

-- Stimulus process

ADDREC_proc: process

begin

CS <= '1';

CEO <= '1';

wait for 100 ns;

CS <= '0';

wait for 120 ns;

CEO <= '0';

wait for 500 ns;

A <="01010010101";

wait for 500 ns;

A <="01010010110";

wait for 500 ns;

A <="01010011110";

wait for 500 ns;

A <="01011110101";

wait for 500 ns;

end process;

END;

3) Функциональная верификация (Behavioral simulation). Полученная диаграмма.

Справочные данные