LEC09. Структура и принципы функционирования компьютера

.pdf

Классификация архитектур ЭВМ (2)

•По разрядности интерфейсов и машинных слов:

8-, 16-, 32-, 64-, 128-разрядные

•По особенностям набора команд и регистров:

CISC – Complete Instruction Set Computer RISC – Restricted (Reduced) ISC

CRISP – Complex-Reduced-Instruction-Set Processor

•По количеству вычислителей: Однопроцессорные, многопроцессорные, одноядерные, многоядерные

Классификация систем команд

Архитектура систем команд

Аккумуляторная

архитектура

(195х)

Регистровая

архитектура

(196x)

Полный набор команд CISC (197x)

Сокращенный набор команд

RISC (198x)

Стековая Безоперандный архитектура набор команд

(196х) (200x)

Архитектура CISC

CISC – complex instruction set computer – компьютер с полным набором команд («долгоиграющие интеллектуальные команды»).

•команды с большим количеством операндов;

•мало регистров общего назначения (до 32);

•разнообразие способов адресации;

•много форматов команд различной разрядности;

•обработка совмещается с обращением к памяти.

Доля сложных дополнительных команд CISC в общем объеме программ не превышает 10-20%. Емкость микропрограммной памяти для поддержании сложных команд может увеличиваться на 60%.

Архитектура RISC

RISC – reduced instruction set computer – компьютер с сокращенным набором команд («быстрые простые команды»).

•команды очень простые (только наиболее часто используемые);

•много РОНов (сотни)

•есть только две команды обращения к памяти (все остальные команды могут работать только с РОНами)

•мало форматов команд и способов указания адресов операндов.

RISC vs CISC

1.Возможность повышения тактовой частоты и упрощения кристалла с высвобождением площади под кэш.

2.Снижение энергопотребления процессора за счёт уменьшения числа транзисторов.

3.Доля сложных дополнительных команд CISC в общем объеме программ не превышает 10-20%.

4.Возможность упреждающего выполнения команд.

Результат: большинство современных процессоров являются либо чистыми RISC, либо “CISC-поверх-

RISC”.

Форматы команд процессора

а)

15 |

12 |

11 |

9 |

8 |

6 |

5 |

3 |

2 |

0 |

Код |

Адрес 1-го Адрес 2-го |

Адрес |

Адрес |

|

следующей |

||||

операции |

операнда |

операнда |

результата |

команды |

б)

15 |

12 |

11 |

0 |

|

|

|

|

|

|

|

|

|

|

Код |

|

|

Адрес операнда, результата или перехода |

|||

|

|

операции |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в) |

|

|

|

|

|

|

||

15 |

12 |

11 |

0 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Код |

Расширение кода операции |

операции |

Этапы выполнения команд процессором

Полный цикл выполнения команды может включать в себя следующие этапы:

•Вычисление адреса команды (ВАК).

•Выборка команды (ВК).

•Декодирование команды (ДК).

•Вычисление адреса операнда (ВАО).

•Выборка операнда (ВО).

•Выполнение заданной операции (ВЗО).

•Запись результата (ЗР).

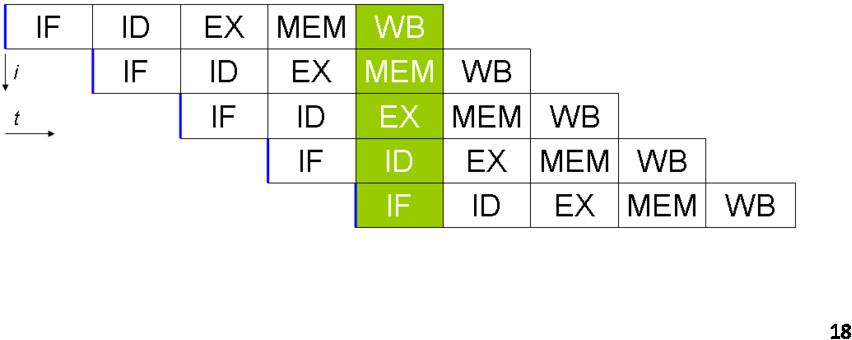

Конвейерная обработка команд

Одним из наиболее распространённых способов увеличения скорости обработки команд является конвейерная обработка команд.

Пример 5-уровневого конвейера в реальном RISC-процессоре:

Обозначения этапов конвейера (см. предыдущий слайд): IF = ВАК+ВК, ID = ДК+ВАО+ВО, EX = ВЗО, MEM+WB = ЗР