- •Блок выбора и обработки входных видеосигналов однокристального процессора UOCIII

- •Цифровой спутниковый ресивер STRONG SRT-4450

- •Питание и информация по одной паре проводов

- •НОВОСТИ ЭФИРА

- •Рамочная антенна KB диапазона

- •Генератор фиксированных частот и частотомер

- •Модуль управления ЖКИ на микроконтроллере

- •Заряжаем батарею ноутбука от зарядного устройства мобильного телефона

- •Источник питания с микроконтроллерным управлением

- •Комбинированный регулятор мощности

- •Изготовление платы без травления

- •Нанесение рисунка проводников печатной платы

- •Сигнализатор недостаточной освещенности

- •Электронный камертон-метроном

- •Автомат световых эффектов — приставка к компьютеру

- •Кодовый замок на микроконтроллере

- •Ультразвуковой отпугиватель крыс на микросхеме КР1211ЕУ1

- •Основные характеристики отечественных микросхемных усилителей мощности ЗЧ

- •Антибраконьер

- •Миниатюрная елка с " бегущим огнем"

- •Звуковые сигнализаторы включения и выключения

- •Охранно-переговорное устройство

- •Игра "Уровень"

- •Управление приборами через СОМ-порт компьютера

- •YL не сбавляют темпа

- •"Охота на лис" началась у нас 50 лет назад

- •"Домодедово — 2007"

- •Усилитель мощности с бестрансформаторным питанием

- •Смеситель диапазона 70 см

- •Вычислитель КСВ-метра

- •Прохождение на KB диапазонах

- •Четыре куплета о доступе

- •НАША КОНСУЛЬТАЦИЯ

- •DS360 — генератор сигналов с ультранизким уровнем гармонических искажений

Модуль управления ЖКИ на микроконтроллере

С.ЗАДОРОЖНЫЙ, г. Киев, Украина

Описанный в статье модуль позволяет соединить четырехраз рядный семиэлементный ЖКИ с источником отображаемой информации по известному малопроводному интерфейсу SPI. Для увеличения разрядности индикатора допускается каскади рование нужного числа модулей. А изменив программу встроен ного в модуль МК, можно принимать информацию по I2С, RS-232 и другим последовательным интерфейсам.

Применение микроконтроллеров в различных устройствах с выводом

числовых значений на цифровой инди катор стало уже д е л о м привычным . Чаще всего индикатор выглядит как ряд семиэлементных знакомест, разделен ных десятичными запятыми. Наиболь шее распространение получили свето диодные индикаторы и ЖКИ . При про ектировании портативной аппаратуры с автономным питанием предпочтение

отдают, как правило, последним ввиду их очень малого энергопотребления, хотя с их применением и связан ряд сложностей и ограничений . Одна из таких сложностей состоит в том, что для управления каждым элементом ЖКИ необходимо переменное напря жение. То есть, если для свечения све тодиодного элемента требуется посто янный ток, элемент изображения на ЖКИ виден только при подаче на него

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контроллер |

|

Число |

Число |

|

Интерфейс |

|

Корпус |

||||||

|

элементов |

общих выводов |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HOLTEK |

|

|

|

|

|

||

HT1621 |

|

32 |

|

4 |

|

|

|

Последовательный |

|

|

|

||

|

|

|

|

|

NXP (Philips Semiconductor) |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ОМ4068 |

|

|

32 |

|

3 |

|

|

|

SPI |

|

DIP-40, QFP-44 |

||

PCF2100C |

|

|

20 |

|

2 |

|

|

|

SPI |

|

DIP-28, SOIC-28 |

||

PCF2111C |

|

|

32 |

|

2 |

|

|

|

SPI |

|

DIP-40, VSO-40 |

||

PCF2112C |

|

|

32 |

|

1 |

|

|

|

SPI |

|

DIP-40, VSO-40 |

||

PCF8533 |

|

|

80 |

|

4 |

|

|

|

l2C |

|

Chip On Glass |

||

PCF8562 |

|

|

32 |

|

4 |

|

|

|

l2C |

|

TSSOP-48 |

||

PCF8566 |

|

|

24 |

|

4 |

|

|

|

l2C |

|

DIP-40, VSO-40 |

||

PCF8576 |

|

|

40 |

|

4 |

|

|

|

l2C |

|

LQFP-64, VSO-56 |

||

PCF8577 |

|

|

32 |

|

2 |

|

|

|

l2C |

|

DIP-40, VSO-40 |

||

|

|

|

|

|

OKI Semiconductor |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ML9060 |

|

|

160 |

|

2 |

|

|

|

SPI |

|

Chip On Glass |

||

MSM6779B |

|

|

160 |

|

нет |

|

|

|

Параллельный |

|

Chip On Glass |

||

|

|

|

|

|

|

|

|

|

четырехразрядный |

|

|

|

|

MSM9006-01 |

|

41 |

|

3 |

|

|

|

SPI |

|

QFP-64 |

|||

MSM9006-02 |

|

41 |

|

4 |

|

|

|

SPI |

|

QFP-64 |

|||

|

|

|

|

|

|

ROHM |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BU9716BK |

|

|

32 |

|

3 |

|

|

|

SPI |

|

QFP-44 |

||

BU9716BKV |

|

|

32 |

|

3 |

|

|

|

SPI |

|

VQFP-48C |

||

BU9718KV |

|

|

32 |

|

3 |

|

|

|

SPI |

|

VQFP-48C |

||

BU9728AKV |

|

|

32 |

|

4 |

|

|

|

SPI |

|

VQFP-48C |

||

BU9735K |

|

|

18 |

|

4 |

|

|

|

SPI |

|

QFP-32 |

||

|

|

|

|

|

MiniLogic |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ML1001 |

|

|

40 |

|

2 |

|

|

|

SPI |

|

Chip On Glass |

||

ML2002 |

|

|

48 |

|

2 |

|

|

|

SPI |

|

Chip On Glass |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Микроконтроллер |

|

Число |

|

|

Число |

|

|

Корпус |

|

||||

|

элементов |

|

общих выводов |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmel |

|

|

|

|

|

|

ATmega169 |

|

|

|

|

25 |

|

|

|

4 |

|

|

TQFP-64 |

|

ATmega329, ATmega649 |

|

25 |

|

|

|

4 |

|

|

TQFP-64 |

|

|||

ATmega3290, ATmega 6490 |

|

40 |

|

|

|

4 |

|

|

TQFP-100 |

|

|||

|

|

|

|

|

Microchip: |

|

|

|

|

|

|||

PIC18F8390, |

|

PIC18F8490 |

|

48 |

|

|

|

4 |

|

|

TQFP-80 |

|

|

PIC18F6390, |

|

PIC18F6490 |

|

32 |

|

|

|

4 |

|

|

TQFP-64 |

|

|

PIC16F946 |

|

|

|

|

42 |

|

|

|

4 |

|

|

TQFP-64 |

|

PIC16F914, |

PIC16F917 |

|

24 |

|

|

|

4 |

|

DIP-40, TQFP-44 |

|

|||

PIC16F913, |

PIC16F916 |

|

16 |

|

|

|

4 |

|

DIP-28, SOIC-28, |

|

|||

|

|

|

|

|

|

|

|

|

|

SSOP-28, QFP-28 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

переменного напряжения частотой в пределах, как правило, 30...60 Гц. Тре буется своего рода "регенерация" изо бражения.

Чтобы освободить п р о г р а м м н о - аппаратные ресурсы основного МК системы от необходимости регенери ровать изображение на таком индика торе, применяют либо специально раз работанные для этой цели микросхе мы-контроллеры (табл. 1), либо ЖКИ с встроенными контроллерами. Эта про блема привела такие фирмы, как Atmel и Microchip к разработке и серийному выпуску МК с встроенными узлами управления ЖКИ (табл. 2) .

И тем не менее радиолюбители и раз работчики промышленной аппаратуры еще сталкиваются с трудностями при менения в своих разработках ЖКИ, так как универсального решения не суще ствует. Если, например, требуется упра влять шестиразрядным семиэлемен - тным ЖКИ с только одним общим элек тродом, то даже без учета десятичных запятых число требующих управления элементов составит 6x7 = 42. Очевидно, что с этой задачей справятся только два МК из числа приведенных в табл. 2, а из представленных в табл. 1 специализи рованных микросхем — только пять, да и те недешевы, малодоступны и не всегда удобны в использовании.

Модуль управления многоразряд ным семиэлементным ЖКИ можно сде лать самостоятельно на основе недоро гого современного МК общего назначе ния. Преимущества такого решения в том, что этот модуль несложно сконфи гурировать под конкретный индикатор, его интерфейс легко адаптировать под устройство — источник отображаемой информации . На модуль управления ЖКИ можно возложить и дополнитель ные обязанности, например, преобра зование двоичных значений или ASCIIкодов символов в "семиэлементные".

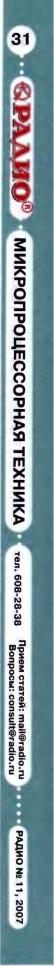

Схема такого модуля изображена на р и с . 1. Он обеспечивает управление четырехразрядным семиэлементным индикатором ИЖЦ5-4/8 (HG1). Инфор мация для вывода на индикатор посту пает от ее источника на вход модуля DATA IN (ХТ4) в сопровождении такто вых импульсов на входе SCK (ХТ3). Мик роконтроллер ATtiny2313 (DD1) прини мает эти сигналы и преобразует их в необходимые для подачи на выводы индикатора. Элементы старшего знако места (А4—G4) соединены в соответ ствующем порядке непосредственно с выходами PB0—РВ7 МК. Сигналы уп равления элементами младших знако мест формируются с помощью сдвиго вых регистров DD2—DD4, информацию для записи в которые МК выводит на выход PD4, а импульсы сдвига — на выход PD5. На выход PD1 и соединен ный с ним контакт ХР7 (DATA OUT) во время приема очередного блока информации длиной 32 двоичных раз ряда (по одному на каждый элемент ЖКИ) МК выдает содержимое предыду щего блока. Его примет следующий модуль, если они соединены последо вательно, как показано на р и с . 2.

Напряжение питания поступает на первый в цепочке модуль (Н1) от источ ника информации, а далее последова-

Рис. 1

Рис. 2

Рис. 3

тельно на все остальные. При напряже нии питания 5 В потребляемый одним модулем ток не превышает 0,4 мА. Р а б о т о с п о с о б н о с т ь сохраняется при снижении напряжения питания до 2,8 В.

Модуль выполнен на двусторонней печатной плате, изображенной на рис. 3, размеры которой лишь незначи тельно больше размеров самого ЖКИ, который установлен со стороны платы, противоположной той, где размещены микросхемы . Монтируют индикатор в последнюю очередь. Вместо сдвиговых регистров HEF4015BP можно применить отечественные К561ИР2. Все конденса торы — керамические . Внешний вид собранного модуля показан на рис. 4.

В микроконтроллере DD1 необходи мо загрузить программу, коды которой приведены в табл. 3. Она рассчитана на прием информации только по интер фейсу SPI, варианты программы, пред назначенные для работы с д р у г и м и интерфейсами, в этой статье не рас сматриваются . С момента включения питания и до загрузки в модуль какойлибо информации на ЖКИ будет видна десятичная запятая крайнего правого знакоместа.

Если используется МК ATtiny2313 с заводскими установками (встроенный RC-генератор на 8 МГц с делением его частоты на 8), кварцевый резонатор ZQ1 и конденсаторы С4, С5 не требуют ся . Без изменений в программе и без кварцевого резонатора можно приме нить устаревший и снимаемый с произ водства МК AT90S1200, но потребуется предварительно запрограммировать в нем разряд конфигурации (fuse) RCEN, чтобы разрешить работу встроенного RC - генератора частотой 1 МГц. Для микроконтроллера AT90S2313 кварце вый резонатор и конденсаторы необхо д и м ы , так как встроенного генератора в нем нет. Учтите, чтобы при тактовой частоте МК, отличающейся от 1 МГц, сохранить частоту регенерации ЖКИ в пределах 30...60 Гц, придется соответ ственно изменить значение константы PERIOD в исходном тексте программы и заново оттранслировать ее.

Поскольку все функциональные осо бенности модуля управления опреде ляются программой, загруженной в МК D D 1 , ее заменой может быть реализо ван, например, последовательный ин терфейс l2 C. При этом контакт ХТ3 ста нет входом SCL, а ХТ4 — SDA. Исполь зуя же вход RXD (контакт ХТ2), соеди ненный с входом встроенного в МК DD1 модуля UART, можно реализовать сов местимый с RS-232 асинхронный по следовательный интерфейс. Для прие ма и н ф о р м а ц и и потребуется всего одна сигнальная линия. Частоту квар цевого резонатора ZQ1 в этом случае удобно выбрать равной 1,8432 МГц, что позволит точно устанавливать стан дартные значения скорости приема в интервале от 600 до 1152090 Бод. Реко мендация справедлива при использо вании МК всех упомянутых типов.

Чтобы облегчить переработку про г р а м м ы , р а с с м о т р и м а л г о р и т м ы ее работы при использовании интерфейса SPI. Прием одного двоичного разряда информации в этом случае иллюстри руют временные диаграммы на рис. 5.

Таблица 4

|

Разряд |

Элемент |

Разряд |

Элемент |

|

|

|

|

|

|

1 |

4А |

17 |

2А |

|

2 |

4В |

18 |

2В |

|

3 |

4С |

19 |

2С |

|

4 |

4D |

20 |

2D |

|

5 |

4Е |

21 |

2Е |

Рис. 5 |

6 |

4F |

22 |

2F |

|

7 |

4G |

23 |

2G |

|

8 |

4Н |

24 |

2Н |

|

9 |

ЗА |

25 |

1А |

|

10 |

зв |

26 |

1В |

|

11 |

зс |

27 |

1С |

|

12 |

3D |

28 |

1D |

|

13 |

3E |

29 |

1Е |

|

14 |

3F |

30 |

1F |

|

15 |

3G |

31 |

1G |

|

16 |

3H |

32 |

1Н |

очередного перепада, на выводе PD1 МК и на контакте ХТ7 (DATA OUT) модуля устанавливается уровень, соответ ствующий находящемуся в младшем разряде приемного регистра значению, принятому 32 такта назад.

Элемент ЖКИ будет включен, если в соответствующем ему, согласно табл. 4, разряде принятого информационного блока записана лог. 1, и выключен, если там лог 0. При каскадном соединении нескольких модулей индикации 32-раз рядные информационные блоки, пред назначенные каждый для своего моду ля, следуют один за другим без пауз. Разряды, принятые предыдущим моду лем, с его выхода DATA OUT (ХТ7) посту пают на вход DATA IN (ХТ3) следующего модуля с задержкой на 32 импульса SCK. Поэтому источник информации должен передавать первым блок, пред назначенный для последнего модуля в цепочке, а последним — для первого.

Теперь рассмотрим алгоритм реге нерации изображения на Ж К И . Вре менные д и а г р а м м ы сигналов на его выводах показаны на р и с . 7. На общий электрод (выводы 1 и 34) с выхода PD6 МК подается последовательность им пульсов частотой около 50 Гц и скваж ностью около 2. Чтобы элемент был ви ден, уровень сигнала на соответствую щем ему выводе всегда должен быть инверсным уровню на общем электроде

Ж К И , т. е. подаваемые на |

них и м |

пульсные последовательности |

должны |

быть противофазными. Амплитуда ко лебаний разности потенциалов между элементом и общим электродом при этом достигает удвоенного напряжения питания МК. Когда импульсы на выводе элемента и на общем электроде синфазны, разность потенциалов эпе-

Рис. 6

Период повторения импульсов SCK ( T P E R I O D ) может находиться в пределах от 40 мкс до 20 мс. Если за 20 мс спадаю щий перепад сигнала SCK не зафикси рован, это служит признаком окончания блока информации. Для правильного приема информации программой дли тельность поддержания низкого логиче ского уровня на входе SCK должна нахо диться в пределах 4 ... t P E R I O D - 4 мкс . Уровень на входе DATA IN должен быть

установлен за tR E A D Y >1 мкс до спадающе

го перепада уровня на входе SKC и сох раняться неизменным в течение

t H O L D > 1 2 мкс после него.

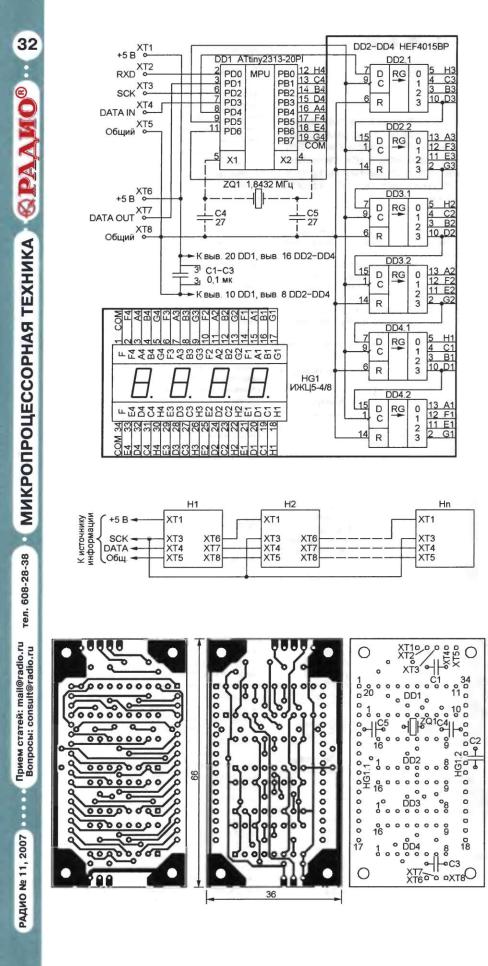

Ввод очередного разряда данных, поступившего на вход DATA IN, реализо ван в подпрограмме обработки преры вания, запрос которого генерируется по спадающему перепаду уровня на входе PD2 МК. Схема алгоритма этой подпро граммы приведена на р и с . 6, а ее исходный текст — в приложенном к статье файле STROBINT.ASM.

Рис. 7

В первую очередь значение очеред ного разряда данных (состояние вывода PD2 на момент прерывания) помещает ся в разряд переноса С регистра SREG. Далее организуется сдвиг вправо через перенос содержимого четырехбайтово го приемного регистра, находящегося в оперативной памяти. После установки флага, свидетельствующего об актив ности процесса приема, и запуска отс чета времени, отведенного на ожидание

мент—общий электрод нулевая, и этот элемент невидим.

С каждой инверсией уровня напря жения на общем электроде соответ ственно инвертируются уровни и на выводах элементов. На элементы стар шего разряда ЖКИ сигналы поступают непосредственно с выходов PB0—РВ7 МК а на выводы элементов остальных разрядов — с выходов сдвиговых реги стров DD2—DD4. Загрузка этих реги-

Рис. 8

стров происходит по сигналам форми руемым МК на выходах PD4 (информа ция) и PD5 (импульсы сдвига). Этот про цесс занимает незначительное по срав нению с периодом регенерации время. При этом выход PD6 МК переводится в в ы с о к о и м п е д а н с н о е с о с т о я н и е , что уменьшает п а р а з и т н у ю е м к о с т н у ю нагрузку выходов регистров, предот вращает нежелательное затягивание перепадов сигналов, а также немного снижает энергопотребление.

Период регенерации задан преры ваниями по переполнению встроенного в МК таймера - счетчика Т/С0. Схема алгоритма обработки этих прерываний приведена на рис. 8, а исходный текст соответствующей п о д п р о г р а м м ы — в

файле TOVELINT.ASM. Прежде |

всего в |

р е г и с т р TCNT0 з а н о с и т с я |

число, |

задающее интервал времени до сле дующего переполнения (около 9,9 мс). Если идет прием информации, следует анализ условий ее завершения с уста новкой и с н я т и е м с о о т в е т с т в у ю щ и х флагов (признаков). Перед выходом из п о д п р о г р а м м ы устанавливается флаг з а п р о с а р е г е н е р а ц и и — о ч е р е д н о г о и з м е н е н и я уровней н а п р я ж е н и я на выводах Ж К И .

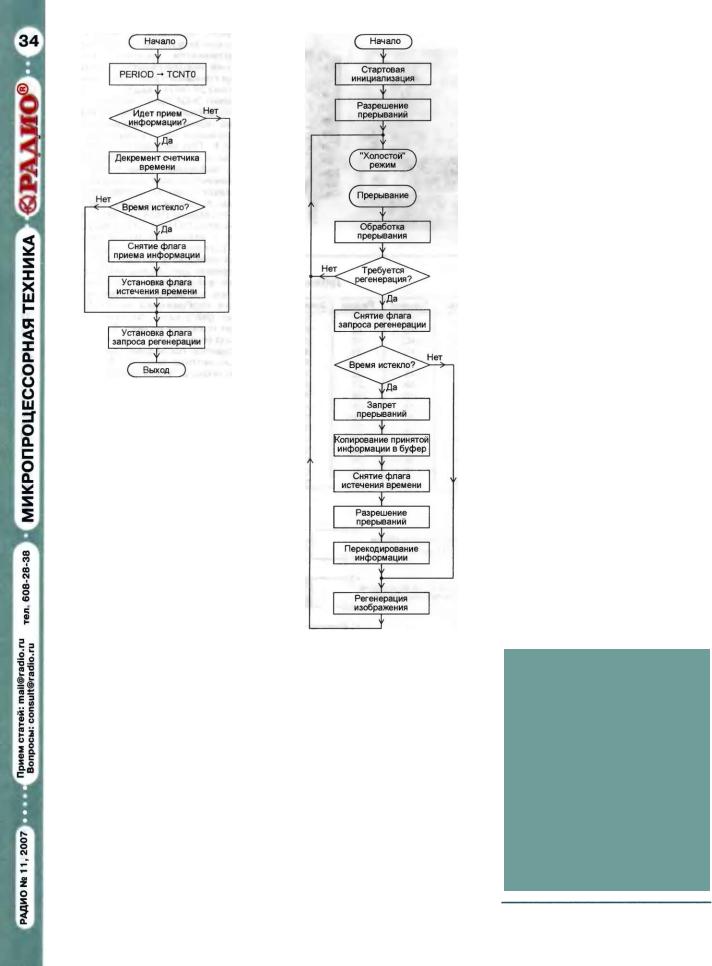

Хранение принятой и н ф о р м а ц и и , преобразование кодов для вывода на ЖКИ, а также собственно регенерация реализованы в основном блоке про граммы, схема алгоритма работы кото рого представлена на рис. 9. Его вы полнение начинается после включения питания и окончания действия внутрен него сигнала установки аппаратных средств МК в исходное с о с т о я н и е . Первым делом происходит стартовая инициализация — установка необходи мых режимов работы таймера-счетчи ка, портов ввода — вывода и прочих встроенных в МК узлов, запись началь ных значений в регистры оперативной

Рис. 9

памяти, после чего следует разрешение прерываний. Далее, с целью снижения общего энергопотребления, программа переводит микроконтроллер в "холо стой" режим (idle mode), выход из кото рого возможен только в ответ на посту пающие запросы прерываний.

После обработки прерывания, вы званного изменением уровня на входе PD2, никаких дальнейших действий от основного блока программы не требу ется и МК возвращается в "холостой" режим .

Если прерывание произошло в ре зультате переполнения таймера-счет чика Т/СО и был установлен флаг запро са регенерации, то по выходе из под программы этот флаг немедленно сни мается. Далее проверяется флаг завер шения приема информации, и если он

установлен, |

прерывания |

временно |

з а п р е щ а ю т с я , |

а принятый |

и н ф о р м а |

ционный блок копируется в организо ванный в оперативной памяти буфер индикации.

Во избежание повторения этих д е й ствий флаг завершения приема снима ется, разрешаются прерывания и про изводится перестановка разрядов при нятой информации для отображения на Ж К И . Необходимость перестановки

обусловлена |

несоответствием порядка |

|

следования |

разрядов |

принятого и н |

ф о р м а ц и о н н о г о блока |

( с м . табл. 4) |

|

порядку подключения элементов инди катора к выходам МК и регистров DD2 — DD4. Эти соединения выполнены исхо дя из удобства трассировки проводни ков на печатной плате модуля.

По окончании перестановки, а также в случаях, когда п р и е м информации еще не завершен, производится реге нерация — инвертируются уровни на выходах РВ0—РВ7 и PD6 МК и выполня ется загрузка инверсной относительно ранее загруженной информации в реги стры DD2—DD4. Затем МК возвращает ся в "холостой" режим и ждет следую щего запроса прерывания,

Исходный |

текст о с н о в н о г о |

блока |

|

п р о г р а м м ы |

с о д е р ж и т с я |

в |

файле |

LCDCTRL.ASM. |

Имеющийся |

в нем |

под |

робный комментарий в сопоставлении с о п и с а н н ы м и алгоритмами позволит легко разобраться в программе, чтобы, если потребуется, самостоятельно мо дифицировать ее под свои нужды.

Предлагаемый модуль управления ЖКИ может стать основой и для других устройств отображения информации . Подобным ж е о б р а з о м м о ж н о по строить контроллер ЖКИ других типов. Для увеличения разрядности достаточ но дополнить ряд сдвиговых регистров требуемым числом аналогичных мик росхем. Можно использовать и другие сдвиговые регистры . Например, мик росхема SN74HC595N с о д е р ж и т не только в о с ь м и р а з р я д н ы й с д в и г о в ы й регистр, но и выходной регистр-защел ку, информация появляется на его выхо дах по отдельному сигналу, что очень удобно, особенно при большой разряд ности Ж К И . Не забудьте при этом изме нить соответствующим образом и про граммное обеспечение.

От редакции. Процедура, названная автором регенерацией изображения, фак тически таковой не является Дело в том, что для обеспечения видимости элемента на ЖКИ достаточно приложить между этим элементом и общим электродом постоян ное напряжение любой полярности. Но происходящие в таком режиме электрохи мические процессы быстро разрушают очень тонкие элементы индикатора замет но снижая срок его службы. Чтобы не давать этим процессам развиться, и при меняют периодическую смену полярности напряжения, стремясь сохранить его постоянную составляющую нулевой.

Программа микроконтроллера модуля управления, в том числе исходные тексты основного блока и подпрограмм находятся на нашем FTP-сервере по адресу <ftp: ftp.radio.ru/pub/2007/11/lcdctrl.zip>

Редактор — А. Долгий, графика — А. Долгий, фото — автора