0, 1, 2, …, (М – 1), 0, 1, 2, … .

Для n-разрядного двоичного счетчика, имеющего 2n состояний, модуль счета M (или коэффициент счета КСЧ) и максимальное число подсчитанных входных импульсов Nmax определяются соотношениями:

M = 2n = Kд; Nmax = 2n – 1. (1.2)

Модуль счета M численно совпадает с коэффициентом деления числа входных импульсов КД. Для периодических входных сигналов, следующих с частотой Fвх, частота выходных сигналов счетчика-делителя равна

Fвых = Fвх / Kд. (1.3)

Счетчики классифицируются по ряду признаков.

По способу переключения триггеров счётчики делятся на:

– асинхронные (последовательные);

– синхронные (параллельные).

По направлению счета:

– суммирующие (прямого счета);

– вычитающие (обратного счета);

– реверсивные (с изменением управления счета).

По способу организации внутренних связей счетчики бывают:

– с последовательным переносом сигналов;

– с параллельным переносом;

– с комбинированным переносом.

По способу кодирования различают двоичные счетчики, двоично- кодированные, счетчики с кодом Грея, счетчики Джонсона и др.

Наибольшее распространение получили двоичные счётчики, а из двоично- кодированных чаще всего применяют двоично-десятичные.

Счётчики с другим модулем счёта можно получить, применяя следующие методы:

– метод принудительного управляемого сброса;

– метод предварительной установки исходного состояния;

– метод синтеза счётчика с дополнительными межразрядными связями.

2. ПРИНЦИПЫ ПОСТРОЕНИЯ СУММИРУЮЩИХ СЧЁТЧИКОВ.

Рассматривая работу счётчика во времени, можно выделить два основных события:

1)промежуток времени, когда счётчик находится в каком-либо определённом состоянии (условимся называть его хранением);

2) момент переключения счётчика из одного состояния в другое (условимся в названии «переключение»).

Во время хранения в каждом разряде счётчика хранится либо логическая единица, либо логический нуль — это определяется текущим состоянием счётчика. При поступлении на счётный вход одного импульса, счётчик должен переключиться в следующее состояние — поменять значения разрядов в согласно следующему состоянию.

Поступление импульса нужно каким-то образом зафиксировать, чтобы счётчик «знал», когда нужно переключиться. Дать команду счётчику на переключение можно либо в момент нарастания фронта импульса, либо его спада.

Соответственно, счётчики можно классифицировать следующим образом:

– переключающиеся по нарастанию фронта импульса;

– переключающиеся по спаду фронта импульса.

Становится понятно, что для формирования разрядов счётчика требуются элементарные ячейки памяти (слово «элементарные» означает то, что они могут хранить только один лог.0 либо одну лог.1 — то есть имеют один бит памяти), которые способны изменять своё содержимое под действием либо нарастания фронта счётного импульса, либо его спада. Этими элементарными ячейками являются синхронные динамические триггеры.

Триггер — это последовательностное цифровое устройство, способное формировать два устойчивых состояния выходного сигнала и скачкообразно изменять эти состояния под действием внешних управляющих сигналов. Одно из состояний триггера называют единичным, второе – нулевым. Состояние триггера определяется значением уровня сигнала на прямом Q или инверсном Q выходе. Если на прямом выходе имеется уровень, соответствующий лог.1, то считают, что триггер находится в единичном состоянии, при этом Q = 1, а Q = 0. В противном случае триггер находится в нулевом состоянии, тогда Q = 0, Q = 1.

Для того, чтобы осуществить переключение счётчика в другое состояние, необходимо чтобы в момент переключения его триггеры переключились определённым образом, соответственно этому состоянию. T-триггер — это триггер, который меняет своё состояние на противоположное по фронту синхронизирующего импульса. Обеспечив нужное соединение T-триггеров между собой и включив в схему определённым образом определённые логические элементы, если это нужно, мы получим счётчик. Как было сказано ранее (см. пункт 3 записки), T-триггер реализуется на основе JK- или D-триггера. В зависимости от типа триггера и от способа реализации можно получить T-триггеры двух видов:

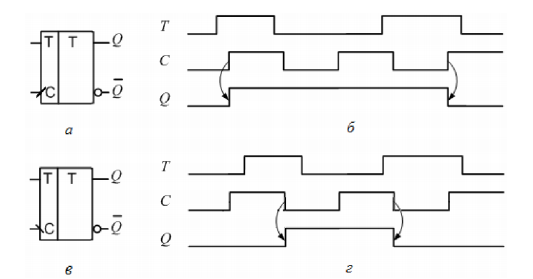

– синхронные (см. рис. 1), которые способны переключатся только при активном уровне управляющего сигнала, поступающего на вход T; – асинхронные (см. рис. 2), которые не имеют управляющего входа и переключаются при каждом нарастании/спаде (в зависимости от триггера) фронта импульса синхронизирующего сигнала на входе T.

Рис. 1. Обозначения и временные диаграммы работы синхронного T-триггера: а и б — переключающегося по нарастанию фронта, в и г — переключающегося по спаду фронта.

Рис. 2. Обозначения и временные диаграммы работы асинхронного T-триггера: а и б — переключающегося по нарастанию фронта, в и г — переключающегося по спаду фронта.

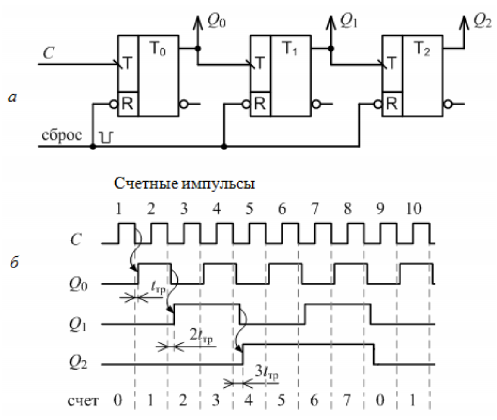

В суммирующем двоичном счётчике каждый очередной входной счётный импульс увеличивает результат счёта на единицу. Такой счётчик можно орга- низовать на асинхронных T-триггерах, соединив прямой выход каждого предыдущего триггера с входом T последующего триггера. Пример такого трёхразрядного счётчика представлен на рис. 3.

Рис. 3. Функциональная схема (а) и временные диаграммы работы (б) асинхронного трёхразрядного счётчика.

Заметным недостатком счётчиков такого типа является относительно большая задержка, численно равная произведению количества триггеров и длительности задержки одного триггера; в данном случае она равна 3tтр (см. рис. 3.3 б). Условие нормальной работы асинхронного счётчика:

tуст = n·tтр < Tи, (2.1)

где Ти — период следования импульсов входного сигнала.

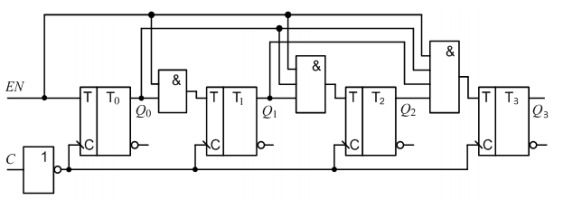

Заметно меньшей задержкой обладает синхронный счётчик (счётчик с параллельным переносом сигналов). В таком счётчике все разряды переключаются одновременно по единому входному счётному сигналу, поступающему на синхровход C. Это происходит благодаря:

– подаче входного счётного сигнала на синхровход каждого триггера; – формированию с помощью комбинационной логики управляющих сигналов для триггеров сигналов межразрядного переноса и параллельной ихподаче на триггеры.

Иными словами, элементы комбинационной логики должны формировать для триггеров сигналы, которые будут разрешать или запрещать триггерам пе- реключаться. Естественно, T-триггеры в таком случае могут применяться только синхронные.

На рис. 4. представлена функциональная схема синхронного четырёхразрядного счётчика. Он выполнен на триггерах с инверсным динамическим входом. Потому как счётный сигнал, который поступает на вход C идёт к триггерам через инвертор, динамический вход C счётчика является прямым, то есть счётчик переключается по нарастанию фронта импульса счётного сигнала. Убрав инвертор, получим инверсный динамический вход.

Рис. 4. Синхронный четырёхразрядный суммирующий счётчик.

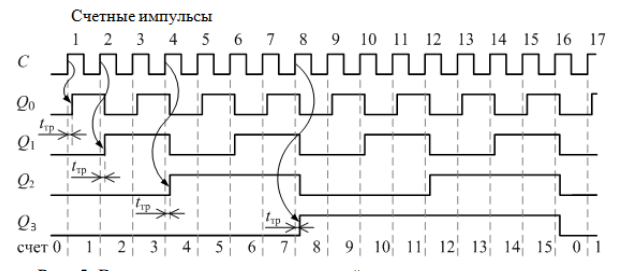

Вход EN разрешает работу счётчика. Из схемы видно: триггер n-го разряда переключается тогда, когда на триггеры 0, 1, …, (n – 1) установлены в единицу, что обеспечивает правильную работу суммирующего счётчика. Временные диаграммы его работы приведены на рис. 5.

Рис. 5. Временные диаграммы четырёхразрядного синхронного двоичного счётчика с прямым динамическим управлением.

Необходимо отметить, что изменения значений сигналов на выходах триггеров всех разрядов происходят в одно и то же время с задержкой на время установления кода tтр в одном триггере (см. рис. 3.5) и отличаются от работы асинхронного счетчика, где время установления выходного кода определяется выражением (2.1).

Время установления выходного кода в синхронном счетчике с параллельным переносом сигналов равно

tуст.сч = tуст.тр. (2.2)

Рассмотренный синхронный счетчик (см. рис. 3.4) обладает согласно выражению (2.2) самым высоким быстродействием, которое не зависит от разрядности n. Однако с ростом числа разрядов реализация счетчика затруднена ввиду усложнения комбинационной логики и применения многовходовых логических.

3. СИНТЕЗ СЧЁТЧИКА НА JK-ТРИГГЕРАХ.

Триггеры типа JK являются универсальными и могут выполнять функции RS-, D-, T-триггера. В сериях ИС JK-триггеры обозначаются буквами ТВ. Выпускаются двухступенчатые JK-триггеры (ТВ1), одноступенчатые с внутренней задержкой (ТВ9,ТВ10, ТВ11), универсальные с динамическим управлением (ТВ15).

В

отличие от RS-триггеров

все JK-триггеры

не имеют запрещенных комбинаций, когда

S

=

R

=

1. При подаче на информационные входы J

и

K

комбинации

сигналов

J

=

K

=

1 триггер переключается в состояние,

противоположное

предыдущему

(Q+

=

),

такой режим работы триггера называется

счетным.

),

такой режим работы триггера называется

счетным.

По сравнению с D-триггером в JK-триггере наличие двух информационных входов J и K позволяет расширить функциональные возможности триггера при построении различных последовательностных цифровых устройств.

Синхронный

JK-триггер

со статическим управлением. Составим

таблицу истинности синхронного

JK-триггера

(рис. 6, а)

с

учетом организации

счетного режима

работы, тогда при значениях CJK

= 1

выходные его состояния

будут

принимать значения Q+

=

Рис.

6. Таблица истинности (а)

и карта Карно (б)

синхронного JK-триггера

Рис.

6. Таблица истинности (а)

и карта Карно (б)

синхронного JK-триггера

По данным таблицы (рис. 6.12, а) составим карту Карно (рис. 6.12, б) и запишем в минимальной дизъюнктивной нормальной форме логическое уравнение, характеризующее работу синхронного JK-триггера:

![]()

С целью

реализации синхронного JK-триггера

на логических элементах

И-НЕ преобразуем

выражение (6.10), введя дополнительный

консенсусный

член Q

,

численно равный нулю, тогда

,

численно равный нулю, тогда

![]()

На рис. 7, а, б, в соответственно показаны: логическая схема, таблица переключений и условное обозначение синхронного JK-триггера.

Рис. 7. Синхронный JK-триггер со статическим управлением.

Особенностью

синхронных JK-триггеров

со статическим управлением является

наличие обратных связей с выхода триггера

на его вход. В этом случае

состояние

триггера будет зависеть не только от

входных информационных сигналов J

и

K,

но и от выходных сигналов Q

и

,

которые

по

цепям обратной

связи

будут поступать на вход схемы и могут

вызвать многократное срабатывание

триггера. Действительно, если применяется

триггер с управлением уровнем

синхросигнала,

то при C

=

1 триггеру, находящемуся в состоянии

,

которые

по

цепям обратной

связи

будут поступать на вход схемы и могут

вызвать многократное срабатывание

триггера. Действительно, если применяется

триггер с управлением уровнем

синхросигнала,

то при C

=

1 триггеру, находящемуся в состоянии

,

будет разрешен прием сигнала с выходаQ

.

В

этом

случае триггер переключится. Если C

по-прежнему

равно 1, то триггеру также разрешен прием

состояния Q,

и он

вновь

переключится. Таким образом, управляющий

синхроимпульс Cдолжен

быть

короче времени переключения триггера,

что практически выполнить довольно

сложно.

,

будет разрешен прием сигнала с выходаQ

.

В

этом

случае триггер переключится. Если C

по-прежнему

равно 1, то триггеру также разрешен прием

состояния Q,

и он

вновь

переключится. Таким образом, управляющий

синхроимпульс Cдолжен

быть

короче времени переключения триггера,

что практически выполнить довольно

сложно.

Поэтому для нормальной работы триггера с обратными связями применяются различные методы построения: двухступенчатые триггеры, выполненные по MS-схеме; одноступенчатые триггеры с внутренней задержкой; триггеры с динамическим управлением.

Двухступенчатый JK-триггер. В различных системах управления с применением синхронных JK-триггеров возникает необходимость независимой установки и считывания информации, причем снятие выходной информации необходимо осуществлять при отключенных входных сигналах. Подобные задачи можно решать с помощью двухступенчатого синхронного триггера, называемого MS-триггером, у которого отсутствует сквозная передача информационного сигнала с входа на выход.

Структура MS-триггера показана на рис. 8, а, его условное обозначение – на рис. 8, в. В состав MS-триггера входят два синхронных RS-триггера со статическим управлением: ведущий триггер M (Master) и ведомый триггер S (Slave). Схема тактируется единым синхросигналом, который подается непосредственно на вход C ведущего M-триггера и через инвертор на вход ведомого S-триггера. На схему управления, выполненную на логических элементах 2И, поступают информационные сигналы J и K.

Рис. 8. Двухступенчатый JK-триггер

Если на входе MS-триггера действует синхросигнал C = 1, то ведущий M-триггер по положительному фронту синхроимпульса C устанавливается в состояние, соответствующее поданным на вход схемы информационным сигналам J и K согласно таблице переключений (рис. 8, б). Данное состояние M-триггера сохранится, пока уровень синхросигнала C будет равен лог. 1.

В это время ведомый S-триггер, имеющий на своем входе инверсный сигнал C, будет находиться в режиме хранения прежней информации и не воспринимает поступающие на его вход сигналы с выхода ведущего M-триггера.

Если

на вход MS-триггера

поступит синхросигнал C

=

0, то при достижении им уровня лог. 0

ведущий M-триггер

установится в режим хранения информации

и будет отключен от информационных

входов J

и

K.

В это время по

отрицательному

фронту синхроимпульса C информационные

сигналы с выходов q

и

ведущего

M-триггера

будут переписаны в ведомый S-триггер

и поступят на выход MS-триггера

(выходы Q

и

ведущего

M-триггера

будут переписаны в ведомый S-триггер

и поступят на выход MS-триггера

(выходы Q

и

).

).

Следует

обратить внимание, что двухступенчатый

JK-триггер

охвачен обратными связями и сигнал J

попадает

на вход S

ведущего

M-триггера

только

тогда,

когда текущие состояния выходных

сигналов принимают значения Q

=

0

и

= 1.

Сигнал K

попадает

на вход R

ведущего

M-триггера,

когда текущие состояния выходных

сигналов принимают значения Q

=

1 и

= 1.

Сигнал K

попадает

на вход R

ведущего

M-триггера,

когда текущие состояния выходных

сигналов принимают значения Q

=

1 и

=

0.При

одновременном воздействии входных

информационных сигналов, когда

J

K 1,

триггер переключается и переходит в

состояние, противоположное

тому, в

котором он находился.

=

0.При

одновременном воздействии входных

информационных сигналов, когда

J

K 1,

триггер переключается и переходит в

состояние, противоположное

тому, в

котором он находился.

Таким

образом, управление процессами в

двухступенчатых триггерах

осуществляется

фронтом и срезом тактового синхроимпульса

C,

а выходные

сигналы триггера Q

и

устанавливаются

только по отрицательному фронту

синхроимпульса.

При этом общая задержка в перезаписи

триггера определяется

в

основном длительностью синхронизирующего

импульса С.

устанавливаются

только по отрицательному фронту

синхроимпульса.

При этом общая задержка в перезаписи

триггера определяется

в

основном длительностью синхронизирующего

импульса С.

Двухступенчатые триггеры не нашли должного применения ввиду сложности схемы и низкого быстродействия.

Одноступенчатый JK-триггер с внутренней задержкой. В последнее время преимущественное применение получил простой одноступенчатый JK-триггер с внутренней задержкой, переключаемый перепадом отрицательного фронта при переходе синхросигнала из единичного в нулевое состояние. Тактовый вход C триггера является инверсным динамическим.

На

рис. 6.15, а,

б представлены

типичная структурная схема и

условные

обозначения JK-триггера

с внутренней задержкой, которая является

основой для

построения

триггеров типа TB6, TB9, TB10, TB11 ТТЛШ- и

КМОП-технологий.

Триггеры

могут иметь дополнительные входы

асинхронной установки

и

сброса

и

сброса

,

которые с целью упрощения схемы на рис.

9, а

не

показаны.

,

которые с целью упрощения схемы на рис.

9, а

не

показаны.

Для правильного функционирования JK-триггера с внутренней задержкой необходимо обеспечить условие, при котором задержка логических элементов И-НЕ tзд.1,2 превышала бы суммарную задержку tзд.Σ остальных элементов И, ИЛИ-НЕ, т.е. tзд.1,2 > tзд.Σ. При указанных условиях в триггерах с внутренней задержкой отсутствует сквозная передача информационных сигналов с входа на выход.

Рис. 9. Одноступенчатый JK-триггер с внутренней задержкой:

а – схема;

б – условные обозначения

Изменения выходных сигналов в данном JK-триггере происходят только по отрицательному фронту синхросигнала C в соответствии с поданными на входы J и K информационными сигналами.

При значениях тактового синхросигнала C = 0 либо C = 1, а также при переходе синхросигнала с нулевого в единичное состояние в триггере устанавливается режим хранения информации и выходной сигнал Q+ = Q.

Режим хранения информации можно осуществить, если в схеме рис. 6.15, а установить следующий режим работы триггера: J = K = 1, C = 1, Q = 0.

Тогда согласно работе логических элементов рисунка 9, а на выходе логического элемента 1 (ЛЭ1) установится значение лог.0, так как на всех его входах присутствует лог. 1.

На выходе ЛЭ3 установится лог.0, на выходе ЛЭ4 – лог. 1, а на выходе ЛЭ7 установится лог. 0. Следовательно, значение на выходе триггера останется прежним: Q+ = Q = 0. Аналогично работает нижнее плечо триггера. При C = 0 режим работы триггера не изменяется.

При ранее установленном режиме работы триггера и действии отрицательного фронта импульса синхронизации, т. е. при переходе C от лог. 1 к лог. 0 (переход 10) на выходе ЛЭ1 – 01. Тогда на выходах ЛЭ3 и ЛЭ4 установится лог. 0, а на выходе ЛЭ7 – 01. Следовательно, триггер изменит свое состояние с нулевого на единичное и станет равным Q+ = 1.

На

рис. 6.16, а,

б

показано

функциональное поведение триггера в

счетном

режиме

при исходном состоянии Q

=

0 и

=

1 и значениях входных

информационных

сигналов J

=

K

=

1.

=

1 и значениях входных

информационных

сигналов J

=

K

=

1.

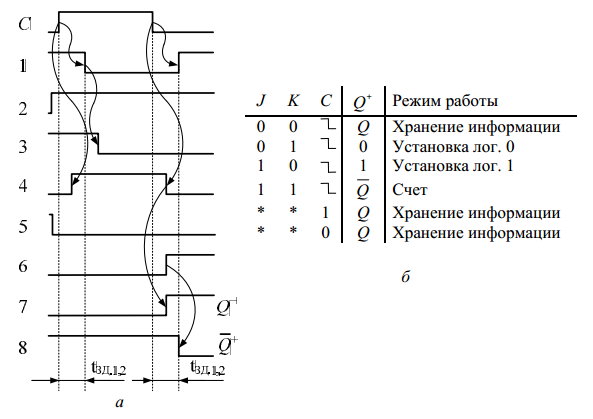

Рис. 10. Временные диаграммы (а) и таблица переключений (б) JK-триггера с внутренней задержкой, * – произвольные значения J и K

Одноступенчатый JK-триггер с внутренней задержкой можно реализовать на микросхемах 3И-НЕ (КР1533ЛА4, аналог 74ALS10) и 2-2И-2ИЛИ-НЕ (КР1533ЛР11, аналог 74ALS51).

3.1. СИНТЕЗ СЧЁТЧИКА С МОДУЛЕМ СЧЁТА 14.

Разработка логической схемы суммирующего недвоичного счетчика с коэффициентом пересчета Кпер.=14

Согласно заданию на курсовое проектирование разработаем логическую схему недвоичного счетчика с коэффициентом пересчета Кпер.=14.

Определим необходимое число триггеров, которое будет определяться как минимальное n, удовлетворяющее неравенству 2n Kпер. В данном случае число триггеров n=4.

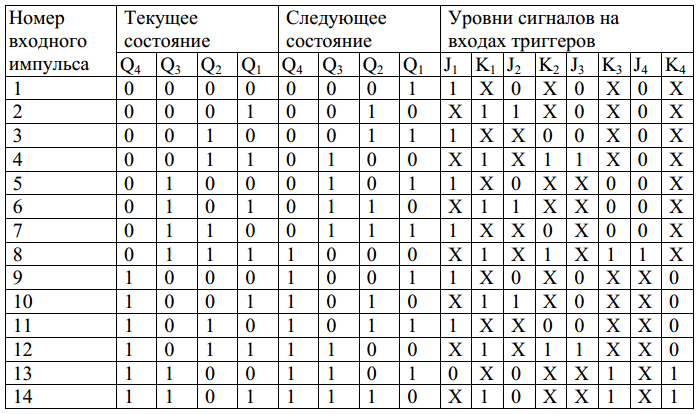

Таблица переходов счётчика представлена в таблице 1. В счётчике с коэффициентом пересчёта Kпер=15 тринадцать состояний, причём каждый тринадцатый импульс сбрасывает счётчик в нулевое состояние. Переход счётчика из текущего в следующее состояние связан с переключением триггеров. Для переключения триггеров в требуемые состояния на их входах J и K необходимы определённые уровни сигналов. В таблице 3 показаны все возможные переходы состояний триггера и требуемые для этих переходов уровни сигналов на входах J и K. На основании таблицы 2 в таблице 3 указаны уровни сигналов на входах J и K, которые обеспечивают переходы счётчика в следующее состояние.

Таблица 1 – Таблица переходов счётчика с коэффициентом пересчёта Kпер=14

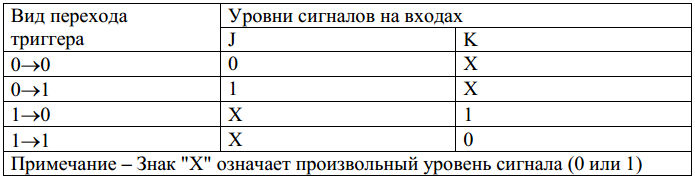

Таблица 2 – Таблица переходов JK-триггера

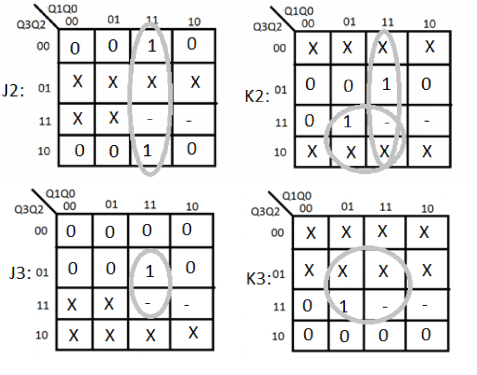

Пусть к моменту подачи первого импульса счётчик находился в состоянии 0000. Под действием этого импульса должно быть обеспечено новое состояние 0001 (таблица 2). Следовательно, в триггере младшего разряда происходит переход вида 01, обеспечиваемый при следующих уровнях на информационных входах: J1=1, K1=X. В остальных триггерах происходит переход вида 00, который обеспечивается уровнями J2=0, K2=X, J3=0, K3=X, J4=0, K4=X. Эти значения занесены в клетки карт Карно для входов J и K всех триггеров, соответствующие состоянию счётчика 0000 (рисунок 5). Пользуясь таблицей 2, можно заполнить карты Карно для входов J и K всех триггеров счётчика. При этом следует помнить, что уровни сигналов на входах J и K являются логическими функциями текущего состояния триггеров и на картах Карно (рисунок 6) под Q4, Q3, Q2, Q1 понимается текущее состояние счётчика, т.е. перед поступлением на вход счётчика очередного импульса. На картах Карно знаком "-" обозначены неопределённые значения функций возбуждения входов J и K, соответствующие лишним состояниям счётчика.

Следует помнить, что при минимизации не полностью заданных логических функций произвольные и неопределённые значения функции можно доопределять с целью упрощения результата минимизации. Следовательно, на картах Карно при записи результата минимизации в МДНФ в замкнутые области следует объединять клетки, заполненные единицами, а также произвольными и неопределёнными значениями логической функции.

Рисунок 11 – Карты Карно для счётчика с коэффициентом пересчёта Kпер=14

По картам Карно запишем следующие выражения для функций возбуждения входов J и K всех триггеров счётчика в МДНФ

J0 = 1 ; (3.3)

K0 =1 ; (3.4)

J1

=

Q0

·(

∀

∀ ; (3.5)

; (3.5)

K1 = Q0 ; (3.6)

J2 = Q1 · Q0 ; (3.7)

K2 = Q1 · Q0 ∀ Q0 · Q3 ; (3.8)

J2 = Q1 · Q0 · Q2 ; (3.9)

K1 = Q0 · Q2 ; (3.10)

Синтез счётчика на триггерах с применением метода введения дополнительных межразрядных связей подразумевает введение в схему логических элементов, реализующих рассчитанные с помощью математического аппарата алгебры логики уравнения запуска триггеров счётчика. При составлении функциональной схемы ориентируются на произвольную элементную базу, отвлекаясь от вопроса о существования таких логических элементов в выпуске промышленностью.

Как видно из временной диаграммы под действием нарастающего фронта счётного сигнала CLK, начиная с нулевого состояния «0000», состояния счетчика сменяются по очередно до последней «1101», после чего цикл счетчика повторяется.

4. АНАЛИЗ И ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ.

Микросхема триггера ТВ9 (IN74AC112), на котором требуется спроектировать счётчик, относится к быстродействующим маломощным КМОП микросхемам серии 1554.