- •Лабораторна робота №1 Тема: Розвиток комп'ютерної архітектури

- •Таблиця 1.1. Основні етапи розвитку комп'ютерів

- •Таблиця 1.2. Перші моделі серії івм-360

- •Лабораторна робота №2 Тема: Типова архітектура еом.

- •Таблиця 2.1. Інтерпретація команд перетворення з різною кількістю адрес в адресній частині

- •Лабораторна робота №3 Тема: Формати команд. Адресовий простір еом

- •Лабораторна робота №4 Тема: Етапи виконання команди. Типи і структура даних. Взаємодія основних пристроїв еом.

- •Лабораторна робота №5 Тема: Структури універсальних, функціонально-орієнтованих і спеціалізованих процесорів. Мікропроцесори

- •Таблиця 3.1. Еволюція мікропроцесорів фірми Intel. Вироби 1970-х років.

- •Таблиця 3.2. Еволюція мікропроцесорів фірми Intel. Вироби 1980-х років.

- •Таблиця 3.3. Еволюція мікропроцесорів фірми Intel. Вироби 1990-х років.

- •Лабораторна робота №6 Тема: Арифметико-логічні пристрої

- •Лабораторна робота №7 Тема: Принцип мікропрограмного управління. Реалізація різних етапів виконання команд

- •Таблиця 15.2 Мікрокоманди пристрою керування гіпотетичного процесора Уілкса

- •Лабораторна робота №8 Тема: Організація даних на магнітному диску. Внутрішня пам’ять

- •Таблиця 6.1. Характеристики пзпмд

- •Лабораторна робота №9 Тема: Ієрархічна структура пам'яті. Віртуальна пам’ять.

- •Таблиця 6.3. Основні функції api для керування віртуальною пам'яттю в системі Windows nt

- •Лабораторна робота №10

- •Листінг 7.1. Приклад програмованого вводу-виводу

- •Лабораторна робота № 12 Тема: Класи переривань

- •Лабораторна робота №12 Тема: Переривання. Дії апаратного та програмного забезпечення

- •Дії апаратного забезпечення:

- •Дії програмного забезпечення:

- •Лабораторна робота № 13 Тема: Фаза переривання основного циклу

- •Лабораторна робота №14 Тема: Організація прямого доступу до пам’яті

- •Лабораторна робота № 15 Тема: Арбітраж шини

- •Лабораторна робота № 16 Тема: Персональні еом, їх різновидності

- •Лабораторна робота № 17 Тема:Робота еом у мультипрограмному режимі

- •Лабораторна робота № 18 Тема:Системи колективного користування з розподілом та без розподілу часу. Системи реального часу

Лабораторна робота №7 Тема: Принцип мікропрограмного управління. Реалізація різних етапів виконання команд

Мікрокоманди

В принципі пристрій керування процесора є досить простим. Але реалізувати його у виді безлічі логічних схем — задача досить складна. Пристрій керування повинен включати логіку формування послідовності мікрооперацій, виконання мікрооперацій, інтерпретації кодів команд і ухвалення рішення на основі аналізу стану прапорів АЛП. Розробити і налагодити таку схему досить складно. Більш того, схема повинна піддатися значній переробці при додаванні в набір команд процесора якої-небудь нової команди.

Альтернативою такої схеми може послужити широко використовувана в сучасних CISC-процесорах мікропрограмна організація пристрою керування. У ній кожна мікрооперація представлена за допомогою символічної нотації, що дуже нагадує нотацію, яка використовується у мові програмування. Фактично — це теж мова програмування, але оскільки вона описує мікрооперації, її, на відміну від більш складних мов, стали називати мовою мікропрограмування. Кожен оператор цієї мови описує набір мікрооперацій, виконуваних спільно в один і той же момент часу, а послідовність операторів являє собою мікропрограму.

Яким же чином концепція мікропрограмування реалізується в конструкції пристрою керування? Для виконання визначеної мікрооперації єдине, що потрібно від пристрою керування, — це сформувати відповідний набір керуючих сигналів. Отже, при виконанні будь-якої мікрооперації кожний з виходів пристрою керування повинен бути або включений (сигнал на ньому дорівнює "лог. 1"), або виключений (сигнал дорівнює "лог. 0"). Тому для сукупності виходів можна сформувати двійкове керуюче слово, кожен розряд якого відповідає визначеному виходу і може приймати значення 0 або 1. Тоді кожна мікрооперація представляється своїм значенням керуючого слова.

Припустимо, що послідовність керуючих слів ми об'єднали в рядок і в такий спосіб представили в пристрої керування послідовність мікрооперацій виконання визначеної команди. Але ця послідовність не є фіксованою. Наприклад, іноді в цикл обробки команди включається фаза непрямої адресації, а іноді ні. Тому запишемо кожне керуюче слово в пам'ять і додамо до нього ще і поле адреси, у якому вкажемо, яке керуюче слово повинне оброблятися наступним при виконанні визначених умов (наприклад, при установці розряду непрямої адресації в поле адреси машинної команди). Додамо до них ще і кілька розрядів для специфікації умови.

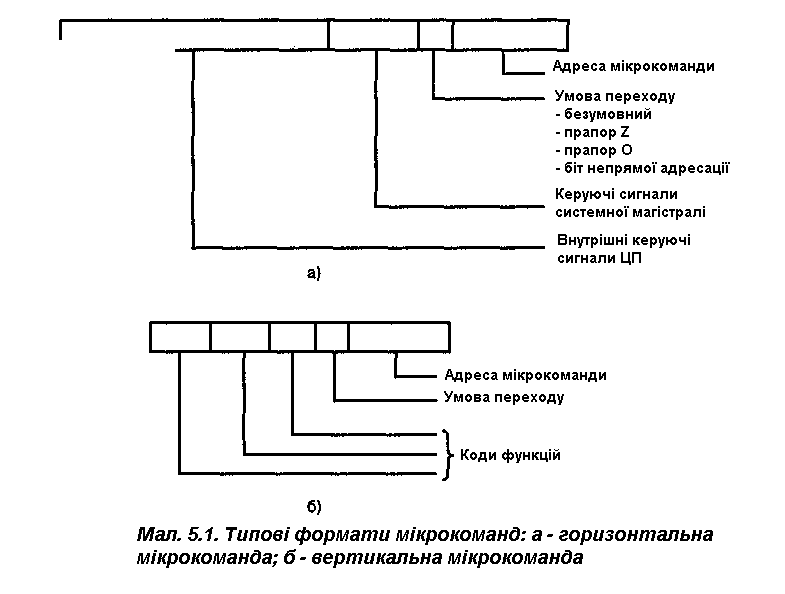

Те, що вийшло, називається горизонтальною мікрокомандою, приклад якої наведений на мал. 5.1,а. Формат мікрокоманди включає такі поля:

•поле внутрішніх керуючих сигналів (по одному розряду на кожен керуючий сигнал);

•поле зовнішніх керуючих сигналів, що передаються по лініях системної магістралі;

•поле умов, у якому вказується код умови переходу;

•поле адреси наступної мікрокоманди при умовному переході. Мікрокоманда інтерпретується в такий спосіб:

1. Необхідно установити сигнали "лог. 1" на усіх виходах, яким відповідає код 1 у керуючому слові мікрокоманди, а на інших виходах установити сигнал "лог. 0". Ця комбінація керуючих сигналів приведе до виконання заданої мікрооперації (чи декількох мікрооперацій).

2. Якщо умова, специфікована в поле умов, має значення "неправда", потрібно далі виконувати мікрокоманду, розміщену по наступній адресі.

3. Якщо умова, специфікована в поле умов, має значення "істина", далі виконується мікрокоманда, розміщена за адресою, що зазначена у полі адреси даної мікрокоманди.

На мал. 5.2 показана схема розміщення послідовностей мікрокоманд (мікропрограм) у керуючій пам'яті (пам'яті пристрою керування). У мікропрограмі всі мікрокоманди виконуються послідовно. Кожна мікропрограма завершується командою переходу, що специфікує, яку мікропрограму потрібно виконати наступною. На схемі показана також спеціальна мікропрограма фази виконання машинних команд, що призначені для розшифровки коду команди (AND, ADD і т.д.) і переходу на відповідну мікропрограму виконання.

Таким чином, вміст керуючої пам'яті вичерпується описом операцій, виконуваних пристроєм керування. У ній визначається, які мікрооперації виконуються протягом кожної фази циклу обробки машинної команди (фаз витягу, непрямої адресації, виконання і переривання) і яку послідовність потрібно виконати наступною. Крім іншого, запис послідовності мікрокоманд є зручним способом документування функцій пристрою керування конкретної моделі комп'ютера.

Мікропрограмний пристрій керування

Керуюча пам'ять, представлена на мал. 5.2, містить програму, що цілком описує функціонування пристрою керування. Тому єдине, що залишається зробити проектувальнику пристрою, — організувати в ньому зчитування і виконання цієї програми.

На мал. 5.3 показані основні вузли пристрою, що реалізує мікропрограмне керування. Послідовність мікрокоманд, що утворить мікропрограму, зберігається в блоці керуючої пам'яті. Регістр адреси керуючої пам'яті (control address register — CAR) містить адреси наступної мікрокоманди. Мікрокоманда, яка зчитана з блоку керуючої пам'яті, міститься в буферний регістр керуючої пам'яті (control buffer register — CBR). Ліва частина цього регістру (див. мал. 5.1,а) приєднана до вихідних ліній керуючих сигналів. Отже, читання мікрокоманди є одночасно і її виконанням. Третій вузол — вузол синхронізації і керування послідовністю виконання мікропрограми — організує завантаження адреси в CAR і формує сигнал читання з блоку керуючої пам'яті.

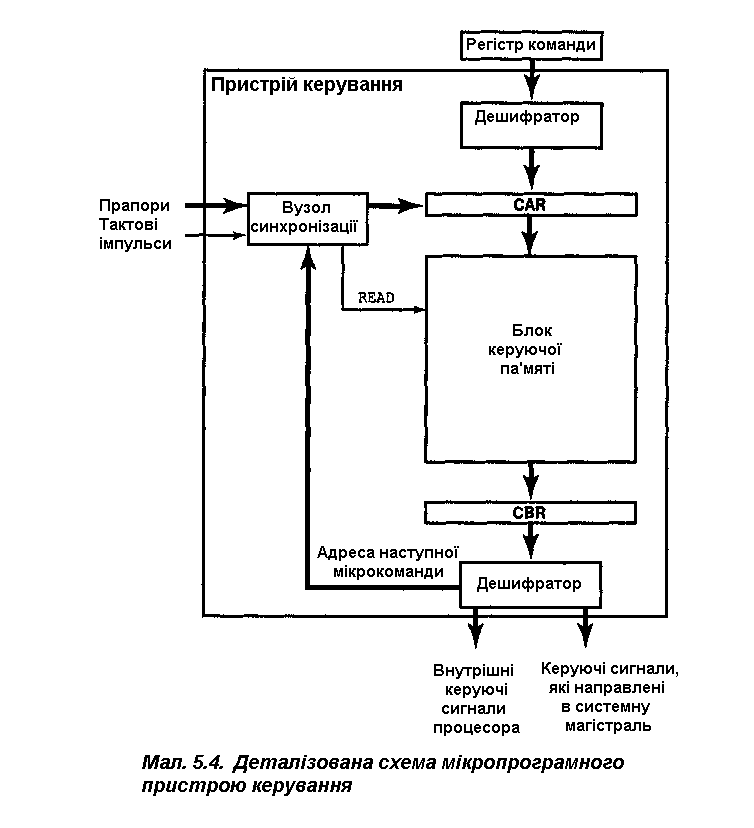

Більш докладна схема мікропрограмного пристрою керування представлена на мал. 5.4. Ця схема приймає вхідні сигнали — вміст IR, прапори АЛП і тактові імпульси і формує відповідні вихідні сигнали. Працює мікропрограмний пристрій керування в такий спосіб:

1. Вузол синхронізації формує сигнал RЕAD (читання), що надходить у блок керуючої пам'яті.

2. Мікрокоманда, адреса якої встановлена у регістрі CAR, зчитується в регістр CBR.

3. На підставі вмісту CBR формуються керуючі сигнали й адреса наступної мікрокоманди.

4. Вузол синхронізації аналізує прапори АЛП і завантажує адресу наступної мікрокоманди в CAR.

Усі ці дії виробляються протягом одного такту.

Останню операцію розглянемо докладніше. Виконання кожної мікрокоманди завершується установкою в регістрі CAR нового значення адреси в блоці керуючої пам'яті. У залежності від значень прапорів АЛП і коду в CBR вузол синхронізації вибирає один із трьох можливих варіантів.

• Витягти мікрокоманду, розміщену по наступній адресі в блоці керуючої пам'яті. Для цього необхідно додати 1 до вмісту CAR.

• Перейти на нову мікропрограму. Для цього код з поля адреси регістра CBR завантажується в CAR.

• Перейти на мікропрограму виконання визначеної машинної команди. Для цього в CAR завантажується адреса, що відповідає коду операції в регістрі IR процесора.

На мал. 5.4 показані два вузли дешифраторів. Верхній дешифратор перетворить код операції з регістра IR на адресу в блоці керуючої пам'яті. Нижній дешифратор використовується тільки в тих пристроях керування, у яких застосовується вертикальне мікропрограмування (див. мал. 5.1,6). Як відзначалося вище, при горизонтальному мікропрограмуванні кожен розряд поля керуючого слова в мікрокоманді відповідає визначеному вихідному сигналу пристрою керування. При вертикальному мікропрограмуванні в мікрокоманді зберігається код, що відповідає виконуваній операції (наприклад, MAR<— (PC)), а дешифратор перетворить цей код в окремі керуючі сигнали. Перевага вертикального формату мікрокоманд — більш компактний код мікропрограми, але за це приходиться платити деяким ускладненням схеми пристрою керування і зниженням швидкодії.

Пристрій керування Уілкса

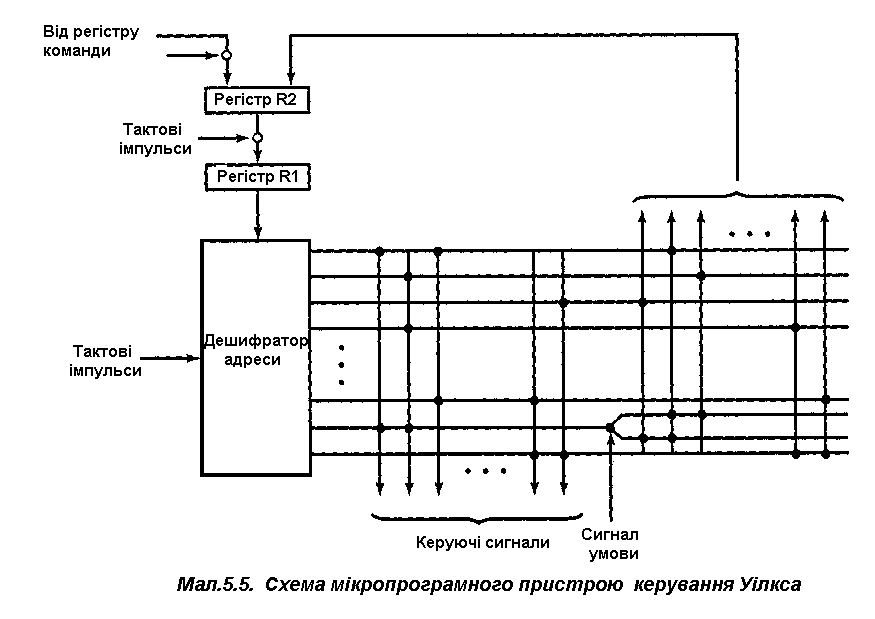

Першим ідею мікропрограмного керування висловив у 1951 році М. Уилкс (M.V. Wilkes). Перша конструкція мікропрограмного пристрою керування зображена на мал.5.5.

Основним вузлом пристрою була матриця провідників, у деяких вузлах якої упаяні діоди. Протягом машинного циклу на один з горизонтальних провідників подавався тактовий імпульс. Цей імпульс проходив на ті вертикальні провідники, що були з'єднані діодами з обраним горизонтальним провідником (на схемі діоди показані жирними крапками). У першій групі вертикальних провідників формувалися сигнали, що керують роботою процесора, а в другій — сигнали, що представляють адресу горизонтального провідника, який повинний бути обраним у наступному циклі. Таким чином, кожен рядок матриці представляв мікрокоманду, а вся матриця — те, що тепер ми називаємо керуючою пам'яттю.

На початку циклу адреса обраного рядка міститься в регістрі R1. Виходи розрядів регістра підключені до дешифратора, що стробірується тактовими імпульсами. Черговий тактовий імпульс формує сигнал на одному з виходів дешифратора, що приєднаний до визначеного горизонтального провідника матриці. У залежності від керуючих сигналів у регістр R2 заноситься або код команди з регістра команд IR, або код, сформований другою групою вертикальних провідників матриці. Потім по наступному тактовому імпульсу код з R2 переноситься в R1. Використання пари регістрів забезпечує затримку установки нового коду в R1 на один такт, що необхідно, оскільки дешифратор являє собою комбінаційну схему без пам'яті.

Фактично в цій схемі реалізований горизонтальний формат мікрокоманд (див. мал. 5.1,а). Особливість її полягає в тому, що в кожній мікрокоманді присутня адреса наступної мікрокоманди, незалежно від того, виконується умовний перехід чи ні. Умовний перехід у схемі Уілкса реалізується в такий спосіб: горизонтальний провідник при приєднанні до другої частини матриці роздвоюється, причому в крапці розгалуження знаходиться вентиль, на другий вхід якого подається сигнал умови (тобто вихід визначеного прапора).

Запропонувавши цю схему, Уілкс також навів у своїй роботі приклад реалізації з її допомогою мікропрограм керування простим процесором. Нижче ми розглянемо даний приклад, оскільки сучасні пристрої мікропрограмного керування побудовані практично по тому ж принципу, хоча на зовсім іншій елементній базі.

Процесор гіпотетичного комп'ютера має у своєму складі наступні регістри:

• А — регістр множника;

• В — акумулятор (молодші розряди);

• С — акумулятор (старші розряди);

• D — регістр зрушення.

Крім того, у складі пристрою керування мається ще три регістри і два прапори. Регістри мають наступне призначення:

• Е — регістр адреси пам'яті (MAR) і регістр тимчасового збереження даних;

• F — лічильник команд;

• G — другий регістр тимчасового збереження даних, лічильник.

У табл. 5.1 представлений набір машинних команд цього гіпотетичного процесора, а в табл. 5.2 — у символічній формі набір мікрокоманд, що реалізовані в пристрої керування. Набір включає 38 мікрокоманд, яких досить, щоб цілком описати функціонування системи.

|

Команда |

Операція |

|

A n S n H n V n T n U n R n L n G n I n O n |

С(АС)+С(п)-АС1 С(АС)-С(п)-АС1 С(п)->АС2 C(AC2) x С(п) –АС С(АС1)-п, 0->АС С(АС1)-п С (АС) х 2(п+1)-АС С (АС) х 2(п+1)-АС Якщо С(АС)<0, перехід на адресу п; інакше продовжувати виконання програми в нормальному порядку Прочитати наступний символ із зовнішнього пристрою в комірку n Переслати С ( п ) у зовнішній пристрій |

Умовні позначки:

АС — акумулятор;

АС1 — старші розряди акумулятора;

АС2 — молодші розряди акумулятора;

n — комірка пам'яті, за адресою n;

З (X) — уміст X , де X — регістр або комірка пам'яті