- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

14.2 Risc-процесори ColdFire

Вхідний контроль:

Чи є довжина команд процесора МРС604 незмінна?

Яку розрядність мають шини адреси та шини даних процесора МРС604?

RISC-процесориColdFire(MCF5XXX) мають таку саму модель користувача, як і сімействоМ68ХХХ, зреалізовують основні команди та способи адресування цього сімейства. Завдяки цьому МПМСF5XXXможуть використовувати значний обсяг програмного забезпечення, розробленого дляМ68ХХХ. Для зменшення обсягу пам’яті команд використовуються команди змінної довжини: 2, 4, 6 байт. Низка моделей вміщують на кристалі BIC таймери, паралельні та послідовні порти, контролер переривань та інші периферійні пристрої; за це їх називають інтегрованими. МПCold Fireслугують для побудови мікропроцесорних систем і можуть входити до складу спеціалізованих мікроконтролерів.

МП вміщують процесорне ядро CFPUзRISC-архітектурою, об’єднану кеш-пам’ять команд/даних обсягом 2 кбайти та блок зовнішнього інтерфейсу, який забезпечує зв’язок з 32-розрядною мультиплексованою системною шиною даних/адрес.

Регістрова модель процесора CFPUвідрізнюється тим, що має один вказівник стекаА7 і формує спільний стек для режимів користувача та супервізора (рис. 11.1). До регістрової моделі супервізора додатково входять регістр базової адреси таблиці векторів переривань та виключень, регістри керування кеш-пам’яттю та звернення до пам’яті.

Процесор CFPUпрацює в режимі користувача або супервізора, аналогічно до МП сімействаМ68ХХХ, емулює основні команди і способи адресування цих МП. З базового набору командCFPUне виконує деякі команди та операції з двійково-десятковими числами, що не робить систему команд недостатньо повною.

Задля налагодження МПС на МП МСF5202 надаються такі можливості:

реалізація режиму налагодження, за якого процесор працює під керуванням зовнішнього налагоджувача;

контроль внутрішнього стану процесора при виконуванні поточної програми;

виконування програми із зупином у контрольних точках.

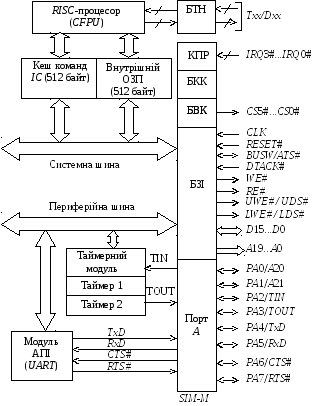

На рис. 14.4 подано структуру інтегрованого мікропроцесора МСF5204, до складу якого входять:

процесорне ядро CFPUзRISC-архітектуроюColdFire;

кеш-пам’ять команд ІСобсягом 512 байт;

статичне ОЗП обсягом 512 байт;

модуль системного інтерфейсу SIM-Мз 8-розрядним портомА;

блок тестування та налагодження (БТН);

таймерний модуль;

асинхронний послідовний інтерфейс (АПІ) типу UART.

До регістрової моделі супервізора додано 32-розрядні регістри RAMBARтаMBAR, які задають базову адресу та режим роботи внутрішнього ОЗП, регістрів різних модулів та блоків МП.

БТН зреалізовує набір режимів та варіантів тестування за стандартом JTAG(IEEE 1149.1).

Внутрішнє статичне ОЗП має обсяг 512 байт. Це ОЗП може розміщуватися, розпочинаючи з будь-якої адреси, яка може задаватися програмно. Керування ОЗП здійснюється шляхом ініціалізації регістра RAMBAR, біти якого можуть маскувати доступ до нього різних типів звернень: в режимі користувача, супервізора при записуванні та зчитуванні даних та команд.

Рисунок 14.4 – Структура інтегрованого мікропроцесора MCF5204

Модуль системної інтеграції SIM-M,до якого входить блок зовнішнього інтерфейса (БЗІ), забезпечує доступ до шести різних банків даних обсягом по 4 Мбайти, для кожного з яких можна ініціалізувати власний протокол обміну.

БВК вміщує шість наборів по три регістри, які керують шістьма банками даних, призначених для зберігання даних у різних режимах роботи процесора.

Блок конфігурації та контролю (БКК) вміщує регістр MBAR, який задає базову адресу блока пам’яті, в якому зберігаються адреси службових регістрів внутрішніх модулів:SIM-M, таймерного таUART(АПІ). У регістріMBARє біт достовірності та інші біти, які визначають права доступу до службових регістрів. До складу БКК входить також монітор шини та вартовий таймер. Монітор шини програмується на видавання запиту виключення “помилка звернення до шини” у разі, коли сигнал підтвердження обмінуDTACK# = 0 не надходить від зовнішнього пристрою упродовж 128, 256, 512 або 1024 тактів.

Контролер переривань КПР забезпечує обробку чотирьох зовнішніх запитів переривань та чотирьох внутрішніх запитів від вартового таймера, таймерів 1 та 2, АПІ.

Порт Авикористовується задля паралельного двоспрямованого обміну даними.

Таймерний модуль складається з 16-розрядних таймерів 1 та 2. Таймер 1 функціонує як таймер загального призначення і може використовуватись у режимі вимірювання часових інтервалів або частоти сигналів, формування імпульсів заданої частоти та тривалості. Таймер 2 працює в режимі лічби внутрішніх імпульсів і може використовуватись задля генерування періодичних переривань.

Асинхронний послідовний інтерфейс АПІ (UART) використовується задля послідовного обміну МП із зовнішніми пристроями і в перебігу приймання контролює помилки парності, порушення кадру, переповнення, порушення зв’язку. Виявлення помилок призводить до формування запиту на переривання. Цей запит оброблюється КПР, так само як і запити після передавання чергового символу, за порожнього буфера передавача, після прийняття символу та заповнення буферної пам’яті приймача.

Основними областями використовування сімейства ColdFireє зв’язок, промислова автоматика, обчислювальна техніка, системи телекомунікацій, контрольно-вимірювальна апаратура тощо.

Контрольні питання:

Якими головними рисами можна схарактеризувати RISС-процесори?

Які удосконалення структури порівняно з процесором МРС604 маютьRISС-процесориМСF5XXX?

З якою метою у процесорі МСF5XXXвикористовуються команди змінної довжини?

Яку структуру має інтегрований процесор МСF5204?

У яких пристроях телекомунікацій використовуються RISC-процесори фірмиMotorola?

Контрольні питання підвищеної складності:

З якою метою в режимі супервізора можна задавати базову адресу та режим роботи внутрішнього ОЗП, регістрів різних модулів та блоків процесора МСF5XXX?

З якою метою у процесорі МСF5XXXвикористовуються 6 банків баних?