- •1 Лабораторна робота №1 вивичення схем булевих функцій двох змінних

- •1.1 Основні положення

- •1.2 Варіанти індивідуальних завдань

- •1.3 Загальні зауваження до виконання індивідуальних завдань

- •1.4 Порядок виконання роботи

- •1.5 Зміст звіту

- •1.6 Контрольні запитання

- •2 Лабораторна робота №2 комбінаційні схеми

- •2.1 Основні положення

- •2.2 Варіанти індивідуальних завдань

- •2.3 Порядок виконання роботи

- •2.4 Зміст звіту

- •2.5 Контрольні запитання

- •3.1.3 Асинхронні тригери. Тригер типуRs

- •3.1.4 Синхронні тригери, що тактуються імпульсом

- •3.1.5 Синхронний двоступінчастий jk-тригер типу ms

- •3.1.6 Синхронний d-тригер з динамічним керуванням

- •3.1.7 Jk-тригер із внутрішньою затримкою й динамічним керуванням

- •3.1.8 Приклад розгляду схем із тригерами, їхнього аналізу й застосування в ца

- •3.2 Варіанти індивідуальних завдань

- •3.2.1 Аналіз jk-тригера із внутрішньою затримкою й динамічним керуванням

- •3.2.2 Дослідження тригерних схем, побудованих на базі d- і jk- тригерів

- •3.2.3 Дослідження схеми перетворення синхропослідовності у двофазну послідовність на частоті, рівної 1/2f генератора сі

- •3.2.4 Схема формування двох послідовностей імпульсів зі зрушенням на чверть періоду відносно один одного

- •3.2.5 Синхронізатор зовнішнього одиночного імпульсу довільної тривалості

- •3.2.6 Синхронізатор зовнішнього одиночного імпульсу з додатковою функцією генерації пачки імпульсів

- •3.3 Порядок виконання роботи й зміст звіту

- •3.4 Контрольні запитання

- •Лабораторна робота № 4 регістри й лічильники на основі тригерів. Аналіз і синтез

- •4.1 Регістри. Основні положення

- •4.2 Лічильники. Основні положення

- •4.3 Індивідуальні завдання. Дослідження готових імс регістрів і лічильників в інтегральному виконанні

- •4.4 Порядок виконання роботи

- •4.5 Зміст звіту

- •4.5 Контрольні запитання

- •5 Лабораторна робота № 5 аналіз і синтез моделей цифрових автоматів

- •5.1 Основні положення

- •5.1.1 Математичні моделі цифрових автоматів

- •5.1.2 Табличний спосіб завдання ца

- •5.1.3 Канонічний метод синтезу ца

- •5.1.4 Приклад синтезу ца канонічним методом

- •5.1.5 Завдання ца графом

- •5.2 Приклад синтезу ца із «жорсткою» логікою управління

- •5.2.1 Принцип роботи мікропрограмного автомата із жорсткою логікою управління

- •5.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

- •5.3 Варіанти індивідуальних завдань (із)

- •5.4 Зміст звіту

- •Література

4.1 Регістри. Основні положення

Послідовністні схеми регістрів виконуються на основі тригерів і мають такі основні типи:

- з паралельним входом і виходом регістр пам’яті (Пар.Вх.-Пар.Вих.інформація при завантаженні, розвантаженні входи/виходи регiстру надходить одночасно-паралельно);

- з паралельним входом і послідовним виходом (Пар.Вх.-Посл.Вих. інформація при завантаженні регістру на всi його входи надходить одночасно-паралельно, а при розвантаженні надходить з одного виходу послідовнобіт за бітом);

- з послідовним входом і паралельним виходом (Посл.Вх.-Пар.Вих. інформація при завантаженні надходить на один вхід послідовно, а при розвантаженні знімається одночасно-паралельно з усіх його розрядів-виходів);

- з послідовними входом і виходом (Посл.Вх.-Посл.Вих. інформація подається на один вхід при його завантаженні та знімається з одного виходу при його розвантаженні послідовнобіт за бітом);

- комбінаційні з різними засобами вводу/виводу інформації. Вони поділяються на однофазні (сигнал передається по одному каналу) і паро фазні по двох каналах (прямий, обернений код).

Функція регістрів зберігання, зсув даних і отримання прямих, обернених і доповняльних кодів.

Аналіз паралельних регістрів (1, 2

варіант). Регістри з паралельним

входом/виходом (тип1) називаються

регістрами пам’яті і використовуються,

як прозорі тригери типу«затвор»та тригери з динамічним керуванням. На

рис. 4.1 приведена схема 8-ми розрядного

паралельного регістру пам’яті (що

виконаний на 8-ми D-тригерах: схеми 7477,

7475) із загальним входом керування записом

інформації і його умовне позначення.

Високий рівень на входіC переписує

інформацію з входуDна вихідQ(Di=Qi), низький рівень зберігає дані

за«затвором». Дані зберігаються

або зчитуються з виходівQiтригерів

на наступному кроці виконання алгоритму,

наприклад «додати до суматора вміст

регістру А». Обернений код даних в

регістрі присутній по виходах![]() .

До регістрів типу 2 відноситься 8-ми

розрядний регістр, реалізований на

схемі 74165(3, 4 варіант).

.

До регістрів типу 2 відноситься 8-ми

розрядний регістр, реалізований на

схемі 74165(3, 4 варіант).

Рисунок 4.1 – Схема 8-ми розрядного регістру пам’яті

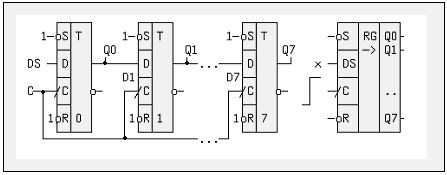

Аналіз послідовних регістрів (3, 4 варіант). Такі регістри зсуву (рис. 4.2, тип 3, 4) виконуються на основі тригерів із динамічною синхронізацією (справедливо для регістрів з одним тактовим сигналом). У двотактних можна використати і прозорі регістри типу«затвор».Функція запису вn-розрядному регістрі зсуву наD-тригерах задається у вигляді умов:D0=DS,Di=Q(i−1); i=1, 2, …,n−1.

Рисунок 4.2 − Варіант послідовного регістру, тип 2: DS − вхід послідовного запису, R і S − входи попередньої установки

З приходом чергового позитивного фронту

синхроімпульсу C, сигнал із входу i-го

тригера через час tзт.п. з’явиться на

його виході і піде на вхід наступного

(![]() )-го

тригера. Однак, на його вихід ця інформація

не перепишеться, тому що тривалість

активного фронту t(0,1) менше

)-го

тригера. Однак, на його вихід ця інформація

не перепишеться, тому що тривалість

активного фронту t(0,1) менше![]() .

На цьому процес зсуву даних на один

розряд закінчиться до приходу наступ-ного

позитивного фронту тактового сигналу.

Звідси зрозуміло, чому не можна використати

тригери зі статичним керуванням. Щораз

при

.

На цьому процес зсуву даних на один

розряд закінчиться до приходу наступ-ного

позитивного фронту тактового сигналу.

Звідси зрозуміло, чому не можна використати

тригери зі статичним керуванням. Щораз

при![]() весь ланцюжок виявиться прозорим від

входу DS до виходу Q7 і значення DS=D0 буде

записано в усі тригери послідовного

регістру. В умовних позначеннях регістрів

зсуву напрямок стрілки, що вказує зсув,

умовний. У різних довідниках її напрямок

дається по-різному. Умовно приймається,

що зсув робиться від молодшого розряду

до старшого. Практичні схеми регістрів

доповнюються схемами, що підключають

до кожного тригера, які мають вхід

паралельного запису Di, загальний вхід

дозволу запису L і загальний асинхронний

вхід скидання в 0 (R) всіх тригерів. Ці

схеми підключаються до незадіяних

входівRi,Si

тригерів. За подібною схемою виконаний

регістр 74164(5, 6 варіант).Уяву проуніверсальні регістри зсуву(тип

5) дає опис Generic 4-bit Universal Shift Register з БМ EWB(7, 8 варіант).

весь ланцюжок виявиться прозорим від

входу DS до виходу Q7 і значення DS=D0 буде

записано в усі тригери послідовного

регістру. В умовних позначеннях регістрів

зсуву напрямок стрілки, що вказує зсув,

умовний. У різних довідниках її напрямок

дається по-різному. Умовно приймається,

що зсув робиться від молодшого розряду

до старшого. Практичні схеми регістрів

доповнюються схемами, що підключають

до кожного тригера, які мають вхід

паралельного запису Di, загальний вхід

дозволу запису L і загальний асинхронний

вхід скидання в 0 (R) всіх тригерів. Ці

схеми підключаються до незадіяних

входівRi,Si

тригерів. За подібною схемою виконаний

регістр 74164(5, 6 варіант).Уяву проуніверсальні регістри зсуву(тип

5) дає опис Generic 4-bit Universal Shift Register з БМ EWB(7, 8 варіант).

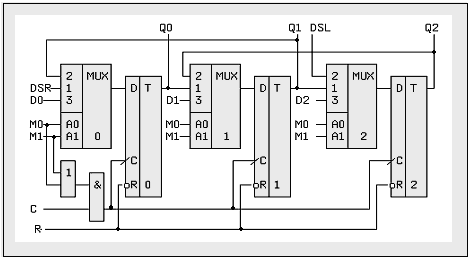

Реверсивний регістр зсуву даних.Зсув даних від розряду до розряду може

робитися, як в одну сторону, так і в іншу.

Одна з можливих схем реверсивного

регістру зсуву на три розряди даних із

двома послідовними інформаційними

входами для зсуву інформації вліво DSL

і вправо DSR, з паралельними входами

запису![]() ,

входом синхроімпульсів C, входом R

установки в 0 усіх тригерів і двома

входами вибору режиму M1, M0, приведена

на рис. 3.3.

,

входом синхроімпульсів C, входом R

установки в 0 усіх тригерів і двома

входами вибору режиму M1, M0, приведена

на рис. 3.3.

Рисунок 4.3 − Варіант реверсивного трирозрядного регістру зсуву (тип 5)

До D-входу будь-якого розряду, за

винятком крайніх, підключені, через

входи 1 і 2 мультиплексори, виходи лівого

і правого сусідніх тригерів. Якщо![]() ,

а

,

а![]() ,

то до входівDпідключені перші входи

мультиплексорів і інформація в кожний

тригер, крім нульового, записується від

лівого сусіда (відбувається зсув вправо).

ВхідDSRслужить, у цьому режимі, для

послідовного введення інформації. Якщо

,

то до входівDпідключені перші входи

мультиплексорів і інформація в кожний

тригер, крім нульового, записується від

лівого сусіда (відбувається зсув вправо).

ВхідDSRслужить, у цьому режимі, для

послідовного введення інформації. Якщо![]() ,

,![]() ,

то до входівDпідключені інші входи

мультиплексів і інформація в кожний

тригер, крім останнього, записується

від правого сусіда, відбувається зсув

вліво. Для послідовного введення даних

у цьому режимі використовується вхідDSL. При

,

то до входівDпідключені інші входи

мультиплексів і інформація в кожний

тригер, крім останнього, записується

від правого сусіда, відбувається зсув

вліво. Для послідовного введення даних

у цьому режимі використовується вхідDSL. При![]() робиться паралельний запис

робиться паралельний запис![]() позитивним

фронтом тактового сигналу. Для зберігання

інформації необхідно подати комбінацію

позитивним

фронтом тактового сигналу. Для зберігання

інформації необхідно подати комбінацію![]() .

У цьому випадку доD-входів тригерів

підключаться нульові входи мультиплексів

(на схемі не показані). Щоб не відбулося

несанкціонованого запису схеми 2АБО і

2І забороняє в цьому режимі (

.

У цьому випадку доD-входів тригерів

підключаться нульові входи мультиплексів

(на схемі не показані). Щоб не відбулося

несанкціонованого запису схеми 2АБО і

2І забороняє в цьому режимі (![]() )

проходження синхроімпульсівС. За

такою схемою виконаний 8-розрядний

регістр 1533ИР13.

)

проходження синхроімпульсівС. За

такою схемою виконаний 8-розрядний

регістр 1533ИР13.