- •1. Введение

- •1.1 Классификация ца. Основные понятия

- •1.2.1. Процессорное устройство со схемной логикой.

- •Структурная схема процессорного устройства

- •1.2.2. Процессорное устройство с программируемой логикой

- •Структурная схема процессорного устройства с программируемой логикой

- •1.3. Элементная база построения цифрового автомата

- •1.4. Структурная схема цифрового автомата

- •Блок схема алгоритма работы цифрового автомата

- •Структурная схема цифрового автомата

- •2. Расчётная часть

- •2.1. Построение графа функционирования

- •Граф функционирования

- •2.2. Кодирование состояний цифрового автомата

- •2.3. Построение таблицы функционирования ца

Структурная схема процессорного устройства

.

. .

Рис. 2

Xs+1 – КОП (Команда из ОЗУ)

XL -

Y1 – Yn – Сигналы управления микрооперациями.

Входы данных – операнды из ОЗУ.

Z1 – Zm – результат в ОЗУ, аккумулятор и СОЗУ.

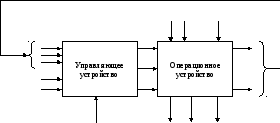

В ОУ выполняются операции логические, арифметические. Оно содержит несколько регистров (РОН, признаков), сумматор.

Управляющее устройство координирует действия узлов ОУ путём выдачи микрокоманд (это “приказ” ЭВМ на исполнение операции. В ней указывается как источник так и приёмник информации, то есть совокупность одной или нескольких микрооперации в различных устройствах) состоящих из определённого числа сигналов исполнения микроопераций (это действие выполняемое в АЛУ). Каждая микрокоманда поступает в операционное устройство и исполняется там по сигналу синхронизации. В определённые тактовые периоды управляющее устройство формирует микрокоманды в состав которых могут входить от одной до нескольких микроопераций таким образом проектирование цифрового автомата должен формировать необходимую последовательность микрокоманд которая преобразуется в микропрограмму (это совокупность всех микрокоманд исполняемых по очереди).

Следовательно при реализации процессорного устройства со схемной логикой необходимо подобрать набор цифровых интегральных микросхем формирующих микропрограммы, они и образуют комбинационно логическую схему.

1.2.2. Процессорное устройство с программируемой логикой

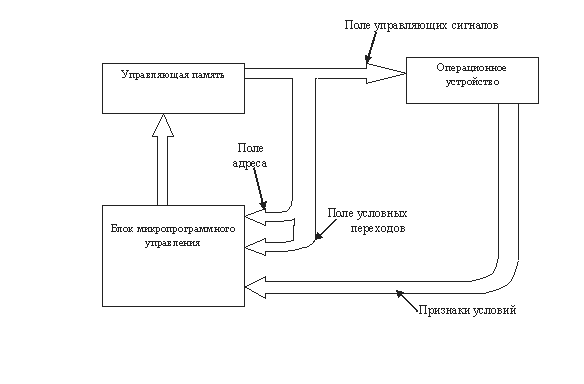

В этом случае функционирование цифрового автомата обеспечивается записью в память (запоминающее устройство микрокоманд или управляющую память) всех микрокоманд микропрограммы.

Исполнение операций в операционном устройстве обеспечивается путём последовательной выборки микрокоманд из запоминающего устройства (рис. 3) то есть нужно указать её адрес.

Структурная схема процессорного устройства с программируемой логикой

Рис 3

Блок микропрограммного управления (БМУ) формирует адрес следующей микрокоманды с учётом признаков текущей микрокоманды.

1.3. Элементная база построения цифрового автомата

Цифровые микросхемы предназначены для обработки, преобразования в хранения цифровой информации. Выпускаются они сериями. Внутри каждой серии имеются объединённые по функциональному признаку группы устройств: логические элементы, триггеры счётчики и т.д. Чем шире функциональный состав серии, тем большими возможностями обладает цифровой автомат, выполненный на базе данной серии. Микросхемы, входящие в состав каждой серии, имеют единое конструктивно – технологическое исполнение, единое напряжение питания, одинаковые уровни сигналов логического 0 и логической 1. Всё это делает микросхемы данной серии совместимыми.

Основой каждой серии цифровых микросхем является базовой логический элемент. Как правило, базовые логические элементы выполняют операции И-НЕ либо ИЛИ-НЕ.

В качестве элементной базы проектируемого цифровой автомат выбираем микросхемы серии К155 как наиболее функциональную и дешевую.

1.4. Структурная схема цифрового автомата

На основании заданного алгоритма (рис 4) и соображений изложенных в пункте 1.2.1 составляем структурную схему цифрового автомата (рис 5)

На блок схеме алгоритма проставляем состояния цифрового автомата. Ставлю состояния от A0 до A4 которые он принимает после исполнения каждой микрокоманды со своими микрооперациями Y1 – Y6 . Символы X1, X2, X3 обозначают проверку условия.