-

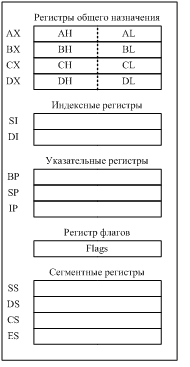

Программная модель микропроцессора.

Рис. 4. Программная модель процессора.

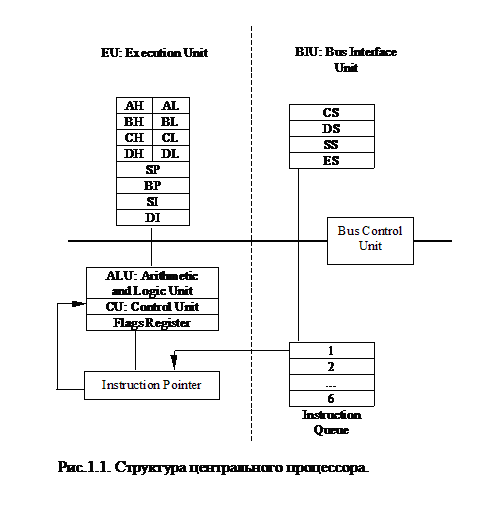

- блок исполнения (EU:Execution Unit); - блок интерфейса шин (BIU:Bus Interface Unit). - interface - это совокупность средств, обеспечивающих сопряжение устройств и программных модулей как на физическом, так и на логическом уровнях). В состав EU входят: арифметическо-логическое устройство ALU, устройство управления CU и десять регистров. Устройства блока EU обеспечивают обработку команд, выполнение арифметических и логических операций. Три части блока BIU - устройство управления шинами, блок очереди команд и регистры сегментов – предназначены для выполнения следующих функций: - управление обменом данными с EU, памятью и внешними устройствами ввода/вывода; - адресация памяти; - выборка команд (осуществляется с помощью блока очереди команд Queue, который позволяет выбирать команды с упреждением). С точки зрения программиста, процессор 8086 состоит из 8 регистров общего назначения, 4 сегментных регистров, регистра адреса команд (счетчика команд) и регистра флагов. Процессор выставляет на шину адреса адрес выбираемых из памяти команд (или данных), которые поступают в шестибайтный буфер (очередь команд), а затем исполняются.

Помимо ячеек оперативной памяти для хранения данных (правда, кратковременного) можно использовать и регистры - ячейки, расположенные в центральном процессоре и доступные из машинных программ. Доступ к регистрам осуществляется намного быстрее, чем к ячейкам памяти, поэтому использование регистров заметно уменьшает время выполнения программ.

Регистр – быстродействующее запоминающее устройство, реализованное на электронных компонентах.

Все регистры имеют размер слова (16 разрядов), за каждым из них закреплено определенное имя. По назначению и способу использования регистры можно разбить на следующие группы:

-

регистры общего назначения (AX, BX, CX, DX, SI, DI, BP, SP);

-

сегментные регистры (CS, DS, SS, ES);

-

указатель команд (IP);

-

регистр флагов (Flags).

|

|

Приведем расшифровку названий регистров: AX accumulator, аккумулятор; BX base, база; CX counter, счетчик; DX data, данные; (буква X - от слова eXtended, расширенный: в процессоре 8080 были байтовые регистры A, B, C и D, но затем их расширили до размера слова) SI source index, индекс источника; DI destination index, индекс приемника; BP base pointer, указатель базы; SP stack pointer, указатель стека; IP instruction pointer, указатель команд; SS stack segment, сегмент стека; DS data segment, сегмент данных; CS code segment, сегмент команд; ES extra segment, дополнительный сегмент. |

-

Таблица распределения памяти и портов ввода/вывода.

|

РАСПРЕДЕЛЕНИЕ ПАМЯТИ |

||

|

Адрес Н-код |

Бинарный код |

Содержимое 2х8 бит |

|

00000 |

00000000 00000000 |

ПЗУ 2048 байт (2х1024 байт). |

|

00001 |

00000000 00000001 |

|

|

00002 |

00000000 00000010 |

|

|

…………. |

…………… …………... |

|

|

…………. |

…………… …………... |

|

|

00FFF |

00001111 11111111 |

|

|

01000 |

00010000 00000000 |

ОЗУ 512 байт (2х256 байт). |

|

01001 |

00010000 00000001 |

|

|

01002 |

00010000 00000010 |

|

|

…………. |

…………… …………... |

|

|

…………. |

…………… …………... |

|

|

01FFF |

00011111 11111111 |

|

|

Порты ввода/вывода |

|||||||||

|

Адрес Н-код |

Бинарный код |

Содержимое 8 бит. |

|||||||

|

00000 |

00000000 |

|

|

|

|

|

|

|

|

|

00001 |

00000001 |

|

|

|

|

|

|

|

|

|

………. |

……….. |

|

|

|

|

|

|

|

|

|

………. |

……….. |

|

|

|

|

|

|

|

|

|

00008 |

00001000 |

Порт вывода ВА |

|||||||

|

00009 |

00001001 |

Порт вывода ВВ |

|||||||

|

0000A |

00001010 |

Порт ввода ВС |

|||||||

|

………. |

……….. |

|

|

|

|

|

|

|

|

|

………. |

……….. |

|

|

|

|

|

|

|

|