- •И.А. Дубров

- •Содержание

- •Введение

- •Лабораторная работа 1 Изучение интегрированной среды разработки mplab

- •Методика выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 2 Изучение запоминающих устройств микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 3 Изучение работы параллельных портов микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 4 Изучение работы последовательных портов микроконтроллеров pic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 5 Изучение работы таймеров микроконтроллеров pic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 6 Изучение работы аналого-цифрового преобразователя микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 7 Изучение работы модуля захвата/сравнения/шим микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Библиографический список

- •Приложение 1. Схема лабораторного макета

- •Bтfss— Условный переход при единичном битеbрегистраf

- •Call— Вызов подпрограммы

- •Goto— Переход по адресу

- •Incf— Декремент регистраf

- •Incfsz— Декремент регистраfи пропуск в случае нулевого результата

- •Iorlw— Побитное «или»Wи константыk

- •Retlw— Выход из подпрограммы с загрузкой в регистрWконстантыk

- •Return— Выход из подпрограммы

- •Rlf— Циклический сдвиг регистраfвлево через флаг переносаС

- •Rrf— Циклический сдвиг регистраfвправо через флаг переносаС

- •Sleep— Перейти в спящий режим

- •Основы микропроцессорной техники

- •620034, Екатеринбург, ул. Колмогорова 66.

Содержание отчета

В отчете необходимо привести постановку задачи, блок-схему алгоритма и текст программы на языке Ассемблер с исправлениями, возникшими на этапе отладки.

Контрольные вопросы

Какие преимущества имеет последовательная организация порта ввода/вывода перед параллельной; параллельная перед последовательной?

* Как видно из лабораторной работы, передача информации по последовательному интерфейсу заметно сложнее, чем по параллельному. Чем вы это объясните?

Лабораторная работа 5 Изучение работы таймеров микроконтроллеров pic-micro

Цель работы: изучение работы и программирование таймеров микроконтроллера PIC16F873A.

Микроконтроллер PIC16F873A имеет четыре таймера TMR0, TMR1, TMR2 и WDT.

Таймер TMR0 представляет из себя 8-разрядный счетчик импульсов с 8-разрядным предделителем. В качестве источника счетных импульсов может выступать внутренний тактовый генератор микроконтроллера, при этом период следования этих импульсов равен длительности машинного цикла (FOSC/4), либо внешний сигнал, подаваемый на вывод RA4/T0CKI микроконтроллера. Максимальная выдержка времени, которую можно сформировать при помощи таймера TMR0 без использования предделителя, равна 256 периодам счетных импульсов, а с использованием предделителя – 65 536. Еще одной особенностью TMR0 является совместное использование предделителя со сторожевым таймером WDT.

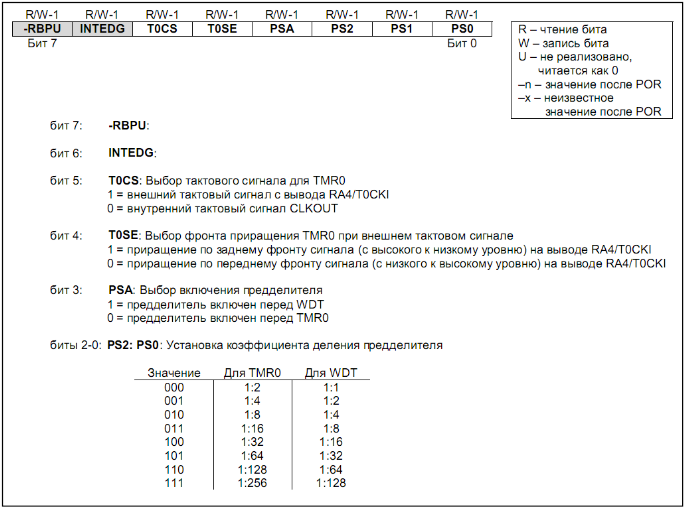

Управление работой таймера осуществляется с помощью шести разрядов регистра OPTION_REG: бит T0SC осуществляет выбор источника счетных импульсов, бит T0SE – выбор переднего или заднего фронта внешних счетных импульсов, бит PSA определяет использование предделителя TMR0 либо WDT, три бита PS0...PS2 задают коэффициент деления предделителя. Значения конкретных разрядов регистра OPTION_REG приведены на рис. 5.1.

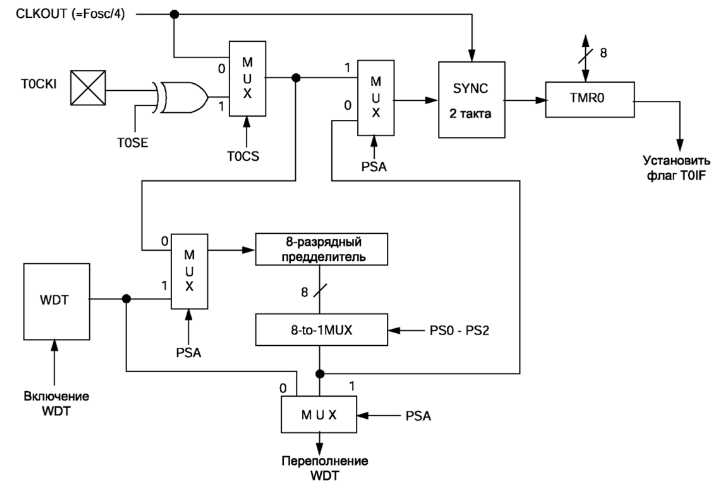

Структурная схема таймера TMR0 приведена на рис. 5.2. Она состоит из регистра-счетчика TMR0, доступного для записи и считывания информации, как регистр специального назначения, 8-разрядного предделителя, который программно не доступен, пяти мультиплексоров MUX, узла синхронизации внешних счетных импульсов SYNC, сторожевого таймера WDT и логического элемента Исключающее ИЛИ.

Схема может работать в четырех режимах:

– счетчик импульсов внутреннего тактового генератора без предделителя. Для перехода в этот режим бит T0SC сбрасывается в «0», а PSA взводится в «1». Импульсы CLKOUT внутреннего тактового генератора проходят через два мультиплексора и узел синхронизации и поступают на вход регистра-счетчика TMR0. Длительность временного интервала T, формируемого таймером, определяется по формуле: T = 28-N, где N – число записанное в регистр TMR0. После переполнения счетчика, то есть при переходе его значения из H'FF' в H'00', взводится флаг T0IF в регистре INTCON и вызывается прерывание, если оно разрешено установкой в «1» битов GIE и T0IE этого же регистра. Необходимо учитывать, что далее счетчик продолжит счет со значения H'00' (выдержка времени 256 машинных циклов), то есть для формирования очередного временного интервала требуемой длительности в регистр TMR0 необходимо снова записать рассчитанное число;

Рис. 5.1. Регистр OPTION_REG

– счетчик импульсов внутреннего тактового генератора с предделителем. Для перехода в этот режим необходимо сбросить в «0» бит PSA. При этом импульсы CLKOUT сначала поступают на вход 8-разрядного предделителя, а уже с его выхода на вход регистра-счетчика TMR0. Коэффициент пересчета предделителя задается битами PS0...PS2. Длительность временного интервала T, формируемого таймером, определяется по формуле: T = K(28-N), где K – коэффициент деления предделителя, а N – число записанное в регистр TMR0. При применении предделителя увеличивается дискретность формирования временного интервала, она равна коэффициенту пересчета предделителя. В остальном работа таймера не отличается от его работы в первом режиме;

– счетчик внешних тактовых импульсов без предделителя. Для перехода в этот режим биты T0SC и PSA взводятся в «1». Импульсы с вывода T0CKI микроконтроллера поступают на вход логического элемента Исключающее ИЛИ. При состояния бита T0SE=0 эти импульсы проходят через него без инверсии и переключение счетчика TMR0 в очередное состояние происходит по переднему фронту счетных импульсов, а при T0SE=1 счетные импульсы инвертируются и срабатывание счетчика происходит по заднему фронту. Далее счетные импульсы проходят через два мультиплексора и попадают на вход схемы синхронизации, где происходит их стробирование во втором и четвертом машинных тактах. Таким образом частота следования счетных импульсов должна быть меньше FOSC/2. В остальном работа таймера аналогична первому режиму;

Рис 5.2. Структурная схема таймера TMR0

– счетчик внешних тактовых импульсов с предделителем. Для перехода в этот режим бит T0SC взводится в «1», а PSA сбрасывается в «0». Работа предделителя в этом режиме аналогична режиму 2, а работа самого счетчика – режиму 3.

Таймер TMR1 является 16-разрядным счетчиком импульсов с 3-разрядным предделителем. Особенностью данного таймера является возможность работы от отдельного низкочастотного кварцевого резонатора, подключаемого к выводам T1OSO и T1OSI микроконтроллера, а также возможность отключения узла синхронизации. Вышеперечисленные особенности обеспечивают работоспособность таймера TMR1 в режиме микропотребления (SLEEP). Максимальная выдержка времени, которую можно сформировать при помощи таймера TMR1 без использования предделителя равна 65 536 периодам счетных импульсов, а с использованием предделителя – 524 288.

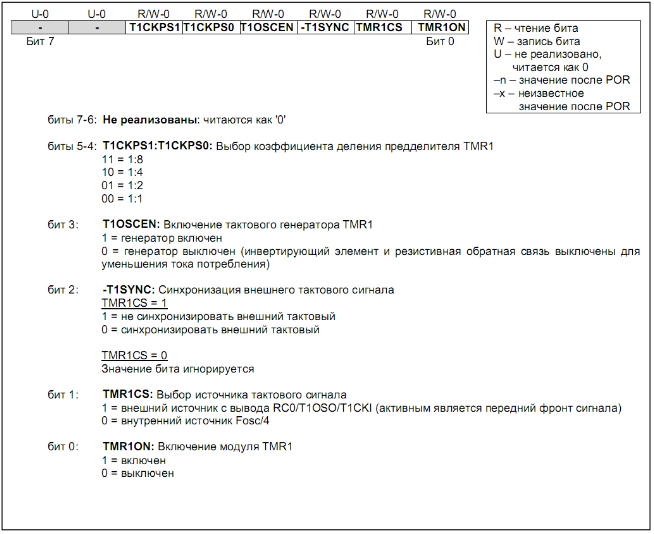

Управление работой таймера осуществляется с помощью регистра специального назначения T1CON: бит TMR1ON включает таймер TMR1, бит TMR1CS задает источник счетных импульсов (счетный вход или тактовый генератор микроконтроллера), бит -T1SYNC включает или выключает узел синхронизации, бит T1OSCEN осуществляет включение внутреннего тактового генератора таймера TMR1, а биты T1CKPS0 и T1CKPS1 задают коэффициент деления входного предделителя. Конкретные значения разрядов регистра T1CON приведены на рис. 5.3.

Рис. 5.3. Регистр управления таймера 1 T1CON

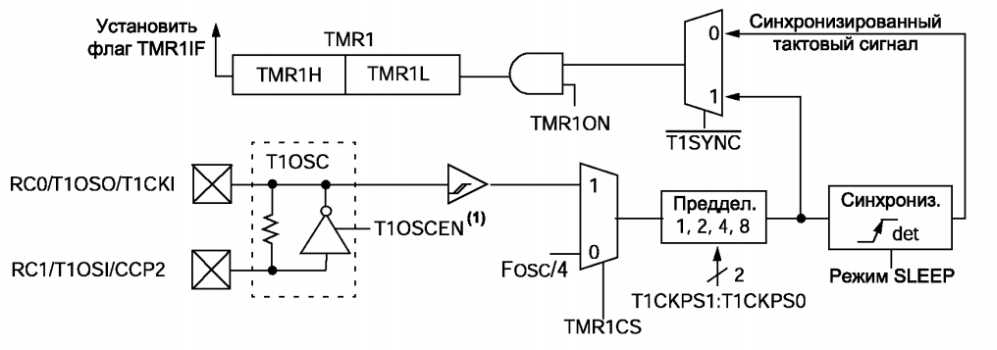

Структурная схема таймера TMR1 приведена на рис. 5.4. Она состоит из 16-разрядного регистра-счетчика TMR1, доступного для записи и считывания информации через два регистра специального назначения – TMR1H и TMR1L, 3-разрядного предделителя, который программно не доступен, двух мультиплексоров, узла синхронизации внешних счетных импульсов, логического элемента И, триггера Шмитта и инвертора, выполняющего роль генератора тактовых импульсов.

Схема может работать в трех режимах:

Счетчик импульсов внутреннего тактового генератора. Для перехода в этот режим необходимо взвести в «1» бит TMR1ON, а бит TMR1SC сбросить в «0». Импульсы внутреннего тактового генератора частотой FOSC/4 проходят через мультиплексор, предделитель, узел синхронизации, второй мультиплексор, логический элемент И и поступают на вход регистра-счетчика TMR0. Длительность временного интервала T, формируемого таймером, определяется по формуле: T = K(216-N), где K – коэффициент деления предделителя, а N – 16-разрядное число, записанное в регистры TMR1H и TMR1L. После переполнения счетчика, то есть при переходе его значения из H'FFFF' в H'0000', взводится флаг TMR1IF в регистре PIR1 и вызывается прерывание, если оно разрешено установкой в «1» битов GIE и T0IE регистра INTCON и бита TMR1IE в регистре PIE1. Аналогично таймеру TMR0 выдержка времени формируется однократно, то есть для повторного запуска таймера TMR1 в регистры TMR1H и TMR1L необходимо программно загрузить расчетное значение.

Рис 5.4. Структурная схема таймера TMR1

Счетчик внешних тактовых импульсов. Для перехода в этот режим биты TMR1ON и TMR1CS взводятся в «1», а бит T1OSCEN сбрасывается в «0». Импульсы с вывода T1CKI микроконтроллера через триггер Шмитта и мультиплексор поступают на вход предделителя. Далее счетные импульсы поступают на вход узла синхронизации. В рабочем режиме микроконтроллера, когда включен его тактовый генератор, внешние счетные импульсы можно синхронизировать вторым и четвертым машинным тактом микроконтроллера (аналогично таймеру TMR0), для этого бит -T1SYNC сбрасывается в «0». Перед переходом в режим микропотребления (команда SLEEP) узел синхронизации необходимо отключить, для этого бит -T1SYNC взводится в «1». В остальном работа таймера аналогична первому режиму.

Счетчик импульсов встроенного тактового генератора таймера TMR1. Таймер TMR1 имеет собственный генератор импульсов, построенный на инверторе и низкочастотном кварцевом резонаторе, подключаемом к выводам T1OSO и T1OSI микроконтроллера. Данный генератор не выключается при переходе микроконтроллера в режим микропотребления. Частота кварцевого резонатора не должна превышать 200 кГц, стандартное значение для «часового» кварцевого резонатора составляет 32 768 Гц. Для перехода в этот режим биты TMR1ON, TMR1CS и T1OSCEN взводятся в «1». В остальном работа таймера аналогична второму режиму, в частности таймер так-же может продолжать свою работу и в спящем режиме.

Таймер TMR2 является 8-разрядным счетчиком импульсов с 4-разрядным предделителем и 4-разрядным выходным делителем. Особенностью данного счетчика является возможность генерации бесконечной последовательности временных интервалов заданной длительности (программная перезагрузка счетчика не требуется). Максимальная выдержка времени, которую можно сформировать при помощи таймера TMR1 без использования делителей равна 256 периодам счетных импульсов, а с использованием делителей – 65 536.

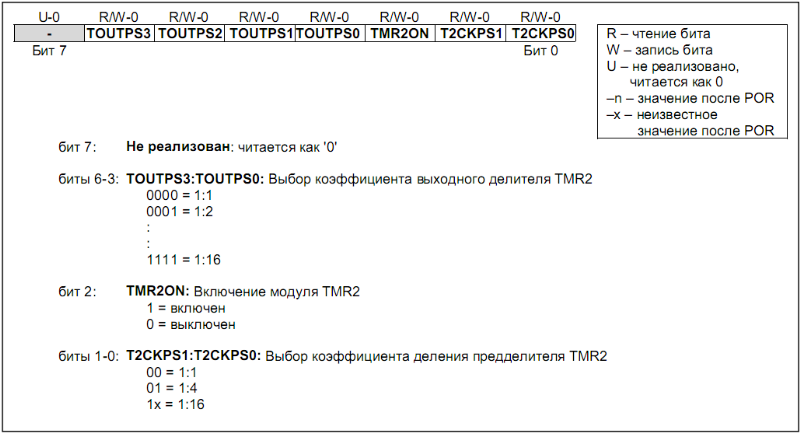

Управление работой таймера осуществляется с помощью регистра специального назначения T2CON: бит TMR2ON включает таймер TMR2, биты T2CKPS0 и T2CKPS1 задают коэффициент деления входного предделителя, а биты TOUTPS0...TOUTPS3 – коэффициент деления выходного делителя. Конкретные значения разрядов регистра T2CON приведены на рис. 5.5.

Рис. 5.5. Регистр управления таймера 2 T2CON

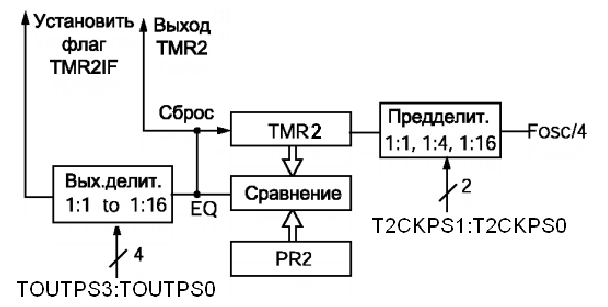

Структурная схема таймера TMR2 приведена на рис. 5.6. Она состоит из 8-разрядного регистра-счетчика TMR2, доступного для записи и считывания информации как регистр специального назначения, 4-разрядного предделителя 4-разрядного выходного делителя (программно не доступны), регистра периода PR2 и схемы сравнения.

Работает схема следующим образом:

Перед включением таймера установкой в «1» бита TMR2ON необходимо записать в регистр периода PR2 число импульсов, которые будет отсчитывать таймер в каждом цикле. Импульсы внутреннего тактового генератора частотой FOSC/4 проходят через предделитель и поступают на вход регистра-счетчика TMR2. При достижении равенства содержимого регистра периода PR2 и счетчика TMR2 на выходе схемы сравнения вырабатывается сигнал EQ, который сбрасывает счетчик в состояние H'00' и процесс заполнения счетчика начинается заново. Через выходной делитель импульсы EQ поступают на выход таймера и взводят флаг TMR2IF в регистре PIR1. При этом может вызывается прерывание, если оно разрешено установкой в «1» битов GIE и T0IE регистра INTCON и бита TMR2IE в регистре PIE1. Длительность временного интервала T, формируемого таймером, определяется по формуле: T = K1·P·K2, где K1 – коэффициент деления предделителя, P – число, записанное в регистр периода PR2, K2 – коэффициент деления выходного делителя.

Рис 5.6. Структурная схема таймера TMR2

Сторожевой таймер WDT предназначен для сброса микроконтроллера в случае программного сбоя (зависание, зацикливание и т. д.). При нормальной работе программы сторожевой таймер сбрасывается командой CLRWDT, выполняемой с интервалом, не превышающим период переполнения сторожевого таймера. В случае программного сбоя сторожевой таймер переполняется и вырабатывает сигнал сброса микроконтроллера, при этом выполнение программы начнется с адреса вектора сброса H'000'.

Сторожевой таймер получает тактовые импульсы от отдельного встроенного RC генератора, что обеспечивает его работу даже в режиме микропотребления (SLEEP). Включение сторожевого таймера производится установкой в «1» разряда WDTE в конфигурационной ячейке 2007. Период переполнения сторожевого таймера зависит от напряжения питания микроконтроллера, температуры и технологического разброса параметров времязадающей RC цепи и составляет от 7 до 33 мс. Период переполнения может быть увеличен до 128 раз путем подключения выходного делителя, используемого совместно с таймером TMR0 (см. рис. 5.2.). При этом бит PSA в регистре OPTION_REG взводится в «1», а биты PS0...PS2 задают коэффициент пересчета делителя.