- •А. В. Шарапов

- •Содержание

- •1. Введение

- •2. Основные понятия микроэлектроники

- •2.1. Виды сигналов

- •2.2. Классификация микросхем и их условные обозначения

- •3. Математические основы цифровой электроники

- •3.1. Позиционные системы счисления

- •3.3. Совершенная дизъюнктивная нормальная форма

- •3.4. Основные законы булевой алгебры

- •Базовые логические элементы

- •4.1. Классификация логических элементов

- •4.2. Базовый элемент ттл

- •4.3. Логический расширитель

- •4.4. Элемент с открытым коллектором

- •4.5. Элемент с z-состоянием на выходе

- •4.7. Базовый элемент ттлш

- •4.8. Базовая схема эсл

- •4.9. Базовые элементы кмоп

- •4.10. Основные характеристики логических элементов

- •4.11. Примеры микросхем логических элементов

- •4.12. Микросхемы на основе арсенида галлия

- •5. Цифровые устройства комбинационного типа

- •5.1. Шифратор

- •5.2. Дешифратор

- •5.3. Преобразователи двоичного кода в двоично-десятичный и наоборот

- •5.4. Дешифратор для управления семисегментным

- •5.5. Преобразователи кода Грея

- •5.6. Мультиплексор

- •5.7. Реализация функций с помощью мультиплексора

- •5.8. Двоичный сумматор

- •5.9. Двоично-десятичный сумматор

- •5.10. Схемы вычитания

- •5.11. Преобразователь прямого кода в дополнительный

- •5.12. Цифровой компаратор

- •5.13. Контроль четности

- •5.14. Примеры построения комбинационных цифровых устройств

- •6. Цифровые устройства последовательностного типа

- •6.7.Классификация счетчиков

- •6.9. Асинхронный двоично-десятичный счетчик

- •Полупроводниковые запоминающие устройства

- •7.7. Примеры микросхем памяти

- •7.8. Организация блока памяти

- •8. Примеры решения задач

- •9. Компьютерный практикум по цифровой схемотехнике

- •Лабораторная работа №1

- •Исследование цифровых устройств

- •Комбинационного типа

- •Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •Исследование цифровых устройств последовательностного типа

- •Пример синтеза счетчика

- •Пример оформления результатов моделирования

- •Программа работы Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •10. Варианты творческих заданий

- •11. Пример выполнения творческого задания

- •Литература

Контрольные вопросы

Перечислить основные законы булевой алгебры. Какой закон описывает формула де Моргана?

С помощью диаграмм Венна доказать логическое тождество

![]() .

.

Дайте определение дешифратору, мультиплексору, сумматору, демультиплексору, цифровому компаратору.

С какой целью проводится минимизация логических функций.

В чем вы видите достоинства представления чисел со знаком в дополнительном коде? Запишите результат сложения дополнительных кодов чисел плюс 80 и минус 33. Каждое число отображается байтом.

Какие коды может сравнивать цифровой компаратор? Запишите возможные варианты функций сравнения.

Как построить восьмиразрядный цифровой компаратор из двух микросхем К555СП1?

Содержание отчета

Отчет в формате Word должен содержать схемы исследуемых узлов, основные экспериментальные данные (вставки из ASIMEC), выводы по пунктам программы работы, а также ответы на контрольные вопросы.

Лабораторная работа №2

Исследование цифровых устройств последовательностного типа

Цель работы. Цель лабораторной работы – проектирование и экспериментальная проверка работы синхронных счетчиков с заданной последовательностью смены состояний, а также анализ работы счетчиков на регистрах сдвига. Используется моделирующий пакет ASIMEC. Программа моделирует лабораторный стол с наборным полем для макетирования цифровых схем и необходимым комплектом контрольно-испытательной аппаратуры.

Пример синтеза счетчика

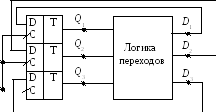

Пусть стоит задача спроектировать вычитающий двоичный счетчик с коэффициентом пересчета Ксч = 6. Для фиксации шести состояний счетчика возьмем три тактируемых по положительному фронту D-триггера, объединенные входы синхронизации которых будем использовать как счетный вход счетчика (рис. 1). Будем характеризовать состояние счетчика N трехразрядным двоичным словом Q3Q2Q1 (N должно циклически меняться от 5 до 0).

G

Рисунок 1 – Функциональная схема счетчика

Каждый импульс генератора G переписывает на выходы триггеров Q1, Q2, Q3 информацию с входов D1, D2, D3. Поэтому дальнейший синтез счетчика сводится к построению комбинационной схемы (логики переходов), формирующей из выходных сигналов Q уровни сигналов D на информационных входах триггеров, необходимые для перехода в следующее состояние. Для этого составим таблицу переходов (табл. 1) и запишем логические выражения для сигналов D1, D2, D3 в ДНФ (дизъюнктивной нормальной форме):

![]() ; (1)

; (1)

![]() ; (2)

; (2)

![]() . (3)

. (3)

Для минимизации логических функций можно воспользоваться основными законами булевой алгебры или картами Карно (рис. 3), причем в клетках, соответствующих шестому и седьмому состоянию счетчика, логические функции можно доопределять по собственному усмотрению, так как в схеме проектируемого счетчика они не реализуются.

По картам Карно запишем минимизированные выражения для функций D1 и D2

![]() ;

;![]() (4)

(4)

![]() .

(5)

.

(5)

Выражение для D3 получим путем преобразования соотношения (3), так как карта Карно не позволяет провести эффективную минимизацию этой функции

![]() .

(6)

.

(6)

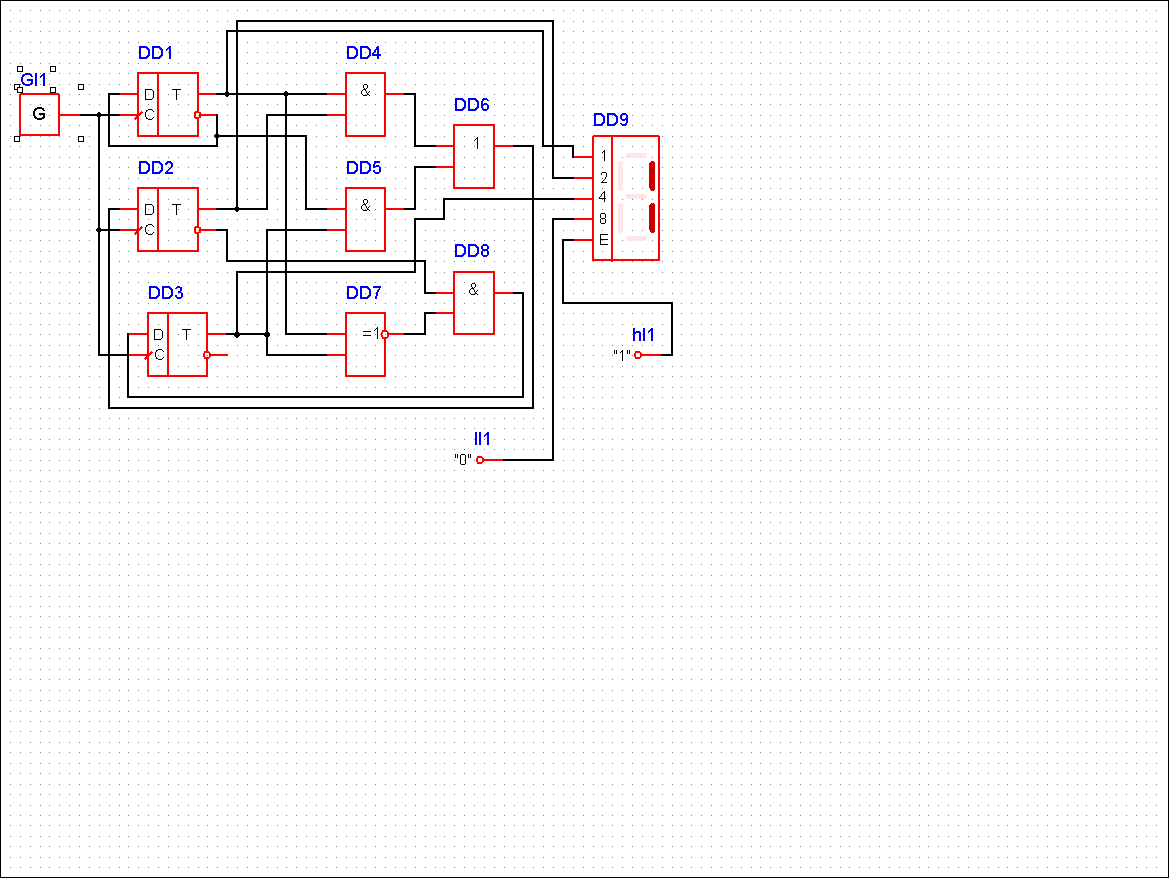

С учетом соотношений (4), (5) и (6) построена схема эксперимента по изучению работы счетчика (рис. 3). Счетные импульсы снимаются с выхода тактового генератора G. Индикация состояний счетчика производится с помощью элемента DD9, выполняющего функцию преобразования четырехразрядного двоичного числа в его шестнадцатеричный эквивалент на семисегментном индикаторе. Удобно выбрать частоту генератора равной 1 Гц.

![]() Таблица

1

Таблица

1

|

|

Текущее

состояние счетчика N Последующее

состояние счетчика N+

|

|

|

|

|

|

|

|

| ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

N |

Q3 |

Q2 |

Q1 |

N+ |

D3 |

D2 |

D1 |

| ||||||||||||||||

|

|

5 4 3 2 1 0 |

1 1 0 0 0 0 |

0 0 1 1 0 0 |

1 0 1 0 1 0 |

4 3 2 1 0 5 |

1 0 0 0 0 1 |

0 1 1 0 0 0 |

0 1 0 1 0 1 |

| ||||||||||||||||

|

|

D1 |

|

Q3 |

|

|

|

D2 |

|

Q3 |

|

|

|

D3 |

|

Q3 |

| |||||||||

|

|

1 |

1 |

X |

1 |

|

|

0 |

0 |

X |

1 |

|

|

1 |

0 |

X |

0 | |||||||||

|

Q1 |

0 |

0 |

X |

0 |

|

Q1 |

0 |

1 |

X |

0 |

|

Q1 |

0 |

0 |

X |

1 | |||||||||

|

|

|

Q2 |

|

|

|

|

|

Q2 |

|

|

|

|

|

Q2 |

|

| |||||||||

Рисунок 2 – Карты Карно для функций D1,D2,D3

Рисунок 3 – Синхронный вычитающий счетчик с Ксч=6