- •1. Введение

- •1.1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •1.2 Области применения цифровых микросхем

- •1.3 Виды цифровых микросхем.

- •Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Логические элементы.

- •2.1 Логические элементы

- •Инвертор

- •Логический элемент "и"

- •Логический элемент "или"

- •2.2 Диодно-транзисторная логика (дтл)

- •2.3 Транзисторно-транзисторная логика (ттл)

- •2.4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •2.5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование микросхем с различным напряжением питания

- •Глава 2

- •2.6 Триггер Шмитта

- •3.Арифметические основы цифровой техники.

- •Глава 1 Арифметические основы цифровой техники

- •3.1 Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •4.2 Синтез цифровых комбинационных схем по произвольной таблице истинности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •4.3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •4.5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •4.6 Демультиплексоры

- •5.Генераторы

- •5.1 Генераторы периодических сигналов

- •5.3 Мультивибраторы

- •5.4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •5.5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •6. Последовательностные устройства (цифровые устройства с памятью)

- •6.1 Триггеры

- •6.1.2 Rs триггер

- •6.1.3 D триггеры, работающие по потенциалу (статические d триггеры)

- •6.1.5 D триггеры, работающие по фронту (динамические d триггеры)

- •6.1.6 T триггеры

- •6.1.7 Jk триггер

- •6.2 Регистры

- •6.2.1 Параллельные регистры

- •6.2.2 Последовательные (сдвиговые) регистры

- •6.2.3 Универсальные регистры

- •6.3 Счётчики

- •6.3.1 Двоичные асинхронные счётчики

- •6.3.2 Недвоичные счётчики с обратной связью

- •6.3.3 Недвоичные счётчики с предварительной записью

- •6.3.5 Синхронные двоичные счётчики

- •7.Современные виды цифровых микросхем.

- •7.1 Микросхемы малой степени интеграции (малая логика)

- •7.2 Программируемые логические интегральные схемы (плис).

- •7.3 Программируемые логические матрицы.

- •7.4 Программируемые матрицы логики (pal).

- •7.5 Сложные программируемые логические устройства (cpld).

- •10. Особенности аналого-цифрового и цифро-аналогового преобразования.

- •10.1 Квантование аналогового сигнала по времени

- •10.2 Погрешности дискретизатора

- •10.3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •10.5 Параллельные ацп (flash adc)

- •10.6 Последовательно-параллельные ацп

- •10.7 Ацп последовательного приближения (sar adc)

- •10.9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •10.10 Цифроаналоговые преобразователи r-2r

- •11. Микросхемы цифровой обработки сигналов

- •11.1 Основные блоки цифровой обработки сигналов

- •11.1.1 Двоичные сумматоры

6.2 Регистры

Регистром называется последовательное или параллельное соединение триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические (flip-flop), так и статические D-триггеры (защелки — lath).

6.2.1 Параллельные регистры

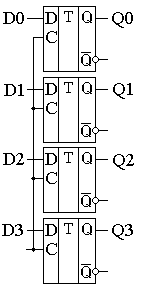

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 8.1, а его условно-графическое обозначение — на рисунке 8.2.

Рисунок 8.1.

Схема параллельного регистра

Рисунок 8.1.

Схема параллельного регистра

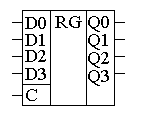

В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG.

В приведённом на рисунке 8.2 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В микросхемах параллельных регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

В настоящее время параллельные регистры обычно являются частью более сложных цифровых устройств, таких как цифровые фильтры, ОЗУ, синтезаторы частот или схемы прямого цифрового синтеза DDS. Подобные схемы не реализуются на микросхемах средней интеграции, а являются частью больших интегральных микросхем (БИС), таких как микропроцессоры, ASIC или FPGA.

6.2.2 Последовательные (сдвиговые) регистры

Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига или сдвиговый регистр) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

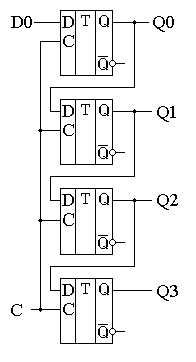

Принципиальная схема последовательного (сдвигового) регистра, собранного на основе D триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 9.1. Обратите внимание, что если для параллельных регистров подходили как триггеры работающие по потенциалу (триггеры-защелки), так и триггеры, работающие по фронту, то для реализации последовательного (сдвигового) регистра подходят D триггеры, работающие по фронту!

Рисунок 9.1.

Схема последовательного (сдвигового)

регистра

Рисунок 9.1.

Схема последовательного (сдвигового)

регистра

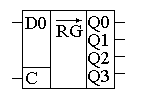

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 9.2.

Рисунок 9.2.

Условно-графическое обозначение

последовательного (сдвигового) регистра

Рисунок 9.2.

Условно-графическое обозначение

последовательного (сдвигового) регистра

Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных регистрах, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного (сдвигового) регистра.

Преобразование последовательного кода в параллельный в последовательном (сдвиговом) регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C.

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере последовательного (сдвигового) регистра и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход. Если бы последовательный (сдвиговый) регистр был собран на D триггерах, работающих по потенциалу, то этот бит тут же записался во второй D триггер! В нашем случае этого не происходит, так как к этому моменту фронт на входе синхронизации C уже закончился.

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера последовательного (сдвигового) регистра, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит входного последовательного кода запоминается в первом триггере последовательного (сдвигового) регистра.

После поступления четвертого тактового импульса в триггерах последовательного (сдвигового) регистра будут записаны логические уровни бит, которые последовательно присутствовали на его входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

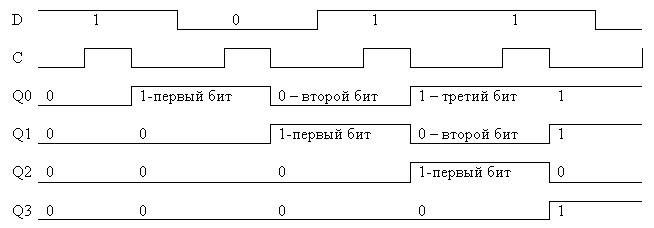

Пусть на вход последовательного (сдвигового) регистра поступает сигнал, временная диаграмма которого изображена на рисунке 9.3, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 9.1.

Рисунок 9.3.

Временная диаграмма работы сдвигового

регистра

Рисунок 9.3.

Временная диаграмма работы сдвигового

регистра

На рисунке 9.3 вместе с логическими уровнями записываются значения бит, которые передаются по соединительной линии или присутствуют на выходах сдвигового регистра.

|

№ такта |

1 |

2 |

3 |

1 |

|

Q0 |

1 |

0 |

1 |

1 |

|

Q1 |

X |

1 |

0 |

1 |

|

Q2 |

X |

X |

1 |

0 |

|

Q3 |

X |

X |

X |

1 |