Описание микроконтроллераMc68hc11e9.

Контроллер MC68HC11E9.

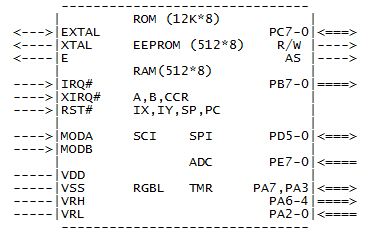

В состав МК входит постоянная ROM, загружаемая EEPROM, оперативная RAM память и блок регистров RGBL (рис.1). Программно доступны два байтовых аккумулятора A,B, регистр признаков CCR и двухбайтовые индексные регистры IX, IY, указатель стека SP и счетчик команд PC. Блоки SCI и SPI используются для организации последова- тельного обмена через контакты порта PD, через порт PE в блок ADC может вводится 8 аналоговых сигналов, порт PA обслуживает блок таймера TMR. Адреса всех регистров портов и периферийных блоков находятся в зоне RGBL. К контактам EXTAL и XTAL подключается кварцевый резонатор, на вход RST# подается сигнал сброса, на входы IRQ# и XIRQ# - запросы прерываний. При частоте резонатора F1=8 МГц выходная частота на контакте Е составляет 2 МГц, время выполнения короткой команды - 2 цикла Е (1 мкс). Цифровое питание подается через контакты VDD, VSS, аналоговое - через контакты VRH, VRL.

Распределение адресного пространства приведено в табл.1.

Если при сбросе установлено состояние контактов MODA=1, MODB=1, то в свободные адресные зоны можно подключать внешнюю память и периферийные устройства, при этом через порт PC выдается младший байт адреса (со стробом AS), затем через РС выдаются (R/W=0) или принимаются (R/W=1) данные по стробу синхронизации Е. Старший байт адреса выдается через порт РВ. Если свободные адреса не нужны, то при сбросе фиксируется состояние контактов MODA=0, MODB=1 и порты РВ и РС можно использовать для прямого управления внешними устрой- ствами. Обозначение сигналов при различных функциях контактов кристалла при- ведено в табл.2, сами функции поясняются ниже.

Блок SCI используется для организации асинхронного последовательного канала. Линия приема R*D (PD0), линия выдачи T*D(PD1). Передача начинается со стартового бита низкого уровня, затем следуют 8 или 9 информационных бит (начиная с младшего разряда) и стоп-бит высокого уровня. Формат регистров блока приведен в табл.3. Регистр SCCR1 задает 8 или 9 битовый формат посылки (бит М) и режим активизации пассивного приемника (бит WAKE). При WAKE=0 приемник акти- визируется при отсутствии передачи в течение 10 бит, при WAKE=1 приемник акти- визируется по единичному старшему биту посылки (адресный маркер). Для перевода приемника в пассивный режим достаточно установить бит RWU=1 в регистре SCCR2. Биты R8 и T8 в регистре SCCR1 фиксируют девятые биты посылки при приеме и вы- даче при установленном бите M=1. Основные 8 бит приема и 8 бит выдачи фиксиру- ются в буфере SCDR.

4 старших бита SCCR2 разрешают прерывания по различным флагам регистра SCSR, биты TE и RE разрешают выдачу и прием, установка SBK=1 генерирует нуле- вые посылки на линии выдачи. Биты OR, NF, FE в регистре SCSR фиксируют различ- ные ошибки на приеме. Установка бит в регистре BAUD задает различные коэффи- циенты К1 и К2 деления частоты кварца кристалла при генерации скорости приема и выдачи информации. При частоте резонатора F1 (в герцах) скорость передачи в бодах определяется соотношением

BOD = F1 / 64 / K1 / K2

Блок SPI используется для синхронной последовательной выдачи информации по линии MOSI (PD3) и приема по линии MISO (PD2). Линия синхронизации SCK (PD4) работает на выдачу, если блок является хозяином (master), и на прием, если блок является слугой (slave). Перед выдачей байт загружается в буфер SPDR и передается начиная со старшего бита. Выдача совмещена с приемом и по ее окон- чании из буфера SPDR можно прочитать принятый байт. На вход SS# (PD5) подается SS#=1 для master и SS#=0 для slave. Формат регистров блока SPI приведен в табл. 4 - 5. При частоте резонатора F1 частота синхронизации FSCK определяется соотношением

FSCK = F1 / 4 / K

где величина К задается полем SPR1-0 в регистре SPCR. При окончании передачи взводится флаг SPIF в регистре SPSR.

В блоке ADC имеется аналоговый коммутатор на 8 каналов и 8-разряд- ный АЦП. Если задано одноканальное преобразование (в регистре ADCTL бит MULT=0, табл.5 ), то после записи байта в ADCTL выполняются 4 преобразова- ния для заданного канала (поле CN2-0), результаты последовательно записы- ваются в регистры ADR1,...,ADR4 и взводится флаг CCF. При SCAN=0 работа АЦП останавливается, при SCAN=1 она продолжается по циклу, т.е. пятый резуль- тат записывается в ADR1. При многоканальном преобразовании (MULT=1) в ADR1,...,ADR4 фиксируются результаты из каналов 0,1,2,3 (при CN2=0) либо из каналов 4,5,6,7 (CN2=1). Фиксация также возможна либо 4-кратная (SCAN=0) либо непрерывная (SCAN=1). Время одного преобразования - 32 цикла (16 мкс при E=2 МГц).

Система команд приведена в табл.6. Если за именем команды следует опреанд 'op', возможно несколько видов адресации, запись которых на Ассемб- лере и формирование адреса поясняется в табл.8. Содержимое адреса памяти для всех видов в табл.6 обозначено символом М, содержимое двух соседних адресов символами ММ. В отдельных командах пара аккумуляторов A и B могут работать как двухбайтовое слово AB. Формирование признаков одинаково для двух команд одной строки и поясняется в последней графе, сами признаки фиксируются в регистре CCR и поясняются и табл.7. При сбросе устанавливаются в 1 признаки S, X, I, значение остальных признаков не определено.

В качестве иллюстрации ниже приводится программа ввода информации из 4 каналов АЦП с записью информации в оперативную память (имена регистров можно употреблять как расширенные адреса).

LDX #ADR1

LDY #$100

LDAB #4

LDAA #$20

STAA ADCTL ; пуск ADC

M1 TST ADCTL

BPL M1 ; не готово

M3 LDAA 0,X

STAA 0,Y ; запись в ОЗУ

INX

INY

DECB

BNE M3 ; следующий канал

Рис.1 Ресурсы контроллера MC68HC11E9

Таблица 1. Распределение адресного пространства.

0000 - 01FF RAM

1000 - 103F Register Block

B600 - B7FF EEPROM

D000 - FFFF ROM (FFC0-FFF9.. вектора прерываний,

FFFE-FFFF .. стартовый адрес)

Таблица 2. Альтернативные функции контактов.

PA0/IC3 PD0/R*D

PA1/IC2 PD1/T*D

PA2/IC1 PD2/MISO

PA3/OC5 PD3/MOSI

PA4/OC4 PD4/SCK

PA5/OC3 PD5/SS#

PA6/OC2

PA7/OC1

PB7-0/A15-8 PE7-0/AN7-0

PC7-0/A7-0..D7-0

Регистр конфигурации OPTION адрес $1039 биты имя сброс назначение

7 ADPU 0 1..вкл.пит.ADC (пуск ADC через 100 мкс)

6 CSEL 0 0..кварц.синхр.ADC,EEPROM 1..RC синхр (2 МГц)

5 IRQE 0 0..прер. по IRQ#=0 1..прер. по пад.фронту IRQ#

4 DLY 0 1..пауза 4064 такта при запуске кварца

3 CME 0 1..контроль уходов частоты синхронизации

2 0 не использ.

1-0 CR1-0 00 сторож.пауза (00-16ms, 01-65ms, 10-260ms, 11-1s)

Биты 5,4,1,0 записываются только на первых 64 циклах после пуска

Таблица 3. Формат регистров блока SCI

Регистр управления SCCR1 адрес $102C биты имя сброс назначение

7 R8 - 9 бит на приеме

6 T8 - 9 бит на выдаче

5 0 не исп.

4 M 0 0/1.. 8/9 бит в посылке

3 WAKE 0 0..пауза 1..маркер

2-0 000 не исп.

Регистр управления SCCR2 адрес $102D биты имя сброс назначение

7 TIE 0 1..прерыв если TDRE=1

6 TCIE 0 1..прерыв если TC=1

5 RIE 0 1..прерыв если RDRF=1

4 ILIE 0 1..прерыв если IDLE=1

3 TE 0 1..разреш выдачи

2 RE 0 1..разреш приема

1 RWU 0 1..пассивный приемник

0 SBK 0 1..нулевая выдача

Регистр состояния SCSR адрес $102E биты имя сброс назначение

7 TDRE 1 1..буфер выдачи пуст

6 TC 1 1..выдача закончена

5 RDRF 0 1..буфер приема полон

4 IDLE 0 1..пауза приема

3 OR 0 1..ошибка наложения

2 NF 0 1..флаг шума

1 FE 0 1..ошибка кадра

0 0 не использ.

Регистр скорости BAUD адрес $102B биты имя сброс назначение

7 TCLR 0 фабр.тест

6 0 не использ.

5-4 SCP1-0 00 K1 (00-1, 01-3, 10-4, 11-13)

3 RCKB 0 фабр.тест

2-0 SCR2-0 000 K2 (000-1, 001-2, 010-4,...,111-128)

Буфер приема и выдачи SCDR адрес $102F 8 бит приема (при чтении) и 8 бит выдачи (при записи). Передача начинается с младшего бита (после старт-бита).

Таблица 4 Формат регистров блока SPI.

Регистр управления SPCR адрес $1028 биты имя сброс назначение

7 SPIE 0 1..разр.прер. по флагу SPIF

6 SPE 0 1..разреш. блока SPI

5 DWOM 0 0..обыч.выходы PD5-0 1..открытые выходы

4 MSTR 0 0/1..slave/master

3 CPOL 0 0/1..низк/высок уровень SCK при отсутвии передачи

2 CPHA 1 0..сдвиг по SCK|SS# 1..сдвиг по SS#

1-0 SPR1-0 UU K (00-2, 01-4, 10-16, 11-32)

Регистр состояния SPSR адрес $1029 биты имя сброс назначение

7 SPIF 0 1..передача закончена

6 WCOL 0 1..запись до окончания передачи

5 0 не использ.

4 MODF 0 1..конфликт мастер-мастер

3-0 0000 не использ.

Буфер приема-выдачи SPDR адрес $102A

Загружается в master-блоке SPI для начала передачи байта и может быть прочитан в master и slave блоках после ее окончания. Первым при сдвиге в линию MISO выдается старший бит.

Таблица 5. Формат регистров блока ADC.

Регистр управления/состояния ADCTL адрес $1030 биты имя сброс назначение

7 CCF 0 1..все 4 рез-та готовы (CCF=0 при записи в ADCTL)

6 0 не использ.

5 SCAN U 0..4-крат.преобр. 1..непрерыв.преобр.

4 MULT U 0..один канал 1..4 канала

3 CN3 U 0..работа 1..фабр. тест

2-0 CN2-0 UUU номер стартового канала

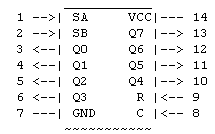

Описание SN74LS 164 - 555ИР8 (8-разрядный сдвиговый регистр)

Q7-0 - выходы 8 разрядов регистра.

По импульсу R=1,0,1 сброс 8 разрядов Q7-0 = 00000000.

По импульсу C=0,1,0 сдвиг Q7-1 = Q6-0, Q0 = (SA & SB)

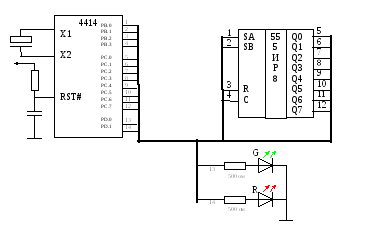

Функциональная схема микропроцессорной системы

Порты PB иPD настроены на вывод сигналов, а портPC на ввод.

В начале программы на контакты 0 и 1 порта PDподается “0”.

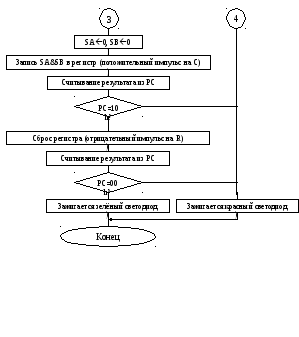

Если микросхема 555ИР8 работает правильно, то на контакт 1 порта PDпоявляется “1”, т.е положительный потенциал и светодиодGзажигается.

Если в работе микросхемы обнаружена ошибка, “1” появляется на 0 контакте и зажигается светодиод R

Форматы слов

Порт B

|

7 |

|

|

|

|

|

|

0 |

|

x |

x |

x |

x |

C |

R |

SB |

SA |

Порт C

|

7 |

|

|

|

|

|

|

0 |

|

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

Порт D

|

7 |

|

|

|

|

|

|

0 |

|

x |

x |

x |

x |

x |

x |

Сигнал ошибки |

Сигнал исправности |

|

Микроконтроллер |

Шина |

Проверяемая микросхема | ||||

|

Порт |

Разряд |

№ Конт-акта |

Обозначение

|

№ Конт-акта |

Назначе-ние | |

|

PB |

0 |

36 |

1 |

SA |

1 |

Управля-ющий |

|

1 |

35 |

2 |

SB |

2 | ||

|

2 |

34 |

3 |

R |

9 | ||

|

3 |

33 |

4 |

C |

8 | ||

|

PC |

0 |

41 |

5 |

Q0 |

3 |

Информа-ционный |

|

1 |

42 |

6 |

Q1 |

4 | ||

|

2 |

43 |

7 |

Q2 |

5 | ||

|

3 |

44 |

8 |

Q3 |

6 | ||

|

4 |

45 |

9 |

Q4 |

10 | ||

|

5 |

46 |

10 |

Q5 |

11 | ||

|

6 |

47 |

11 |

Q6 |

12 | ||

|

7 |

48 |

12 |

Q7 |

13 | ||

|

PD |

0 |

21 |

13 |

Зелёный светодиод |

Информа-ционные светодиоды | |

|

1 |

22 |

14 |

Красный светодиод | |||

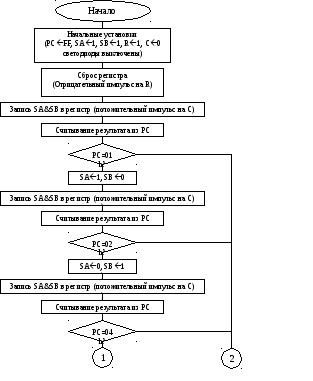

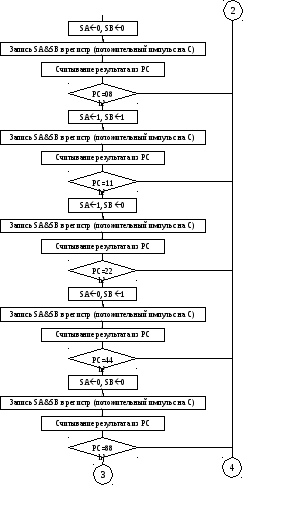

Схема алгоритма работы микропроцессорной системы.