- •Потоковые процессоры

- •Общие сведения

- •Альтернативные функции

- •Устройство портов

- •3.3.1.Регистр режима работы таймера/счетчика tmod

- •3.3.2.Регистр управления/статуса таймера tcon.

- •3.3.3.Режимы работы таймеров-счетчиков.

- •3.5.1.Функциональное назначение бит регистра управления/статуса приемопередатчика scon.

- •3.5.2.Скорость приема/передачи информации через последовательный порт.

- •3.5.3.Регистр управления мощностью pcon.

- •Вопрос #11 Контроллер прерываний msc-51. Особенности работы, программирование

- •3.6.1.Регистр масок прерывания (ie).

- •3.6.2.Регистр приоритетов прерываний (ip).

- •3.6.3.Выполнение подпрограммы прерывания.

- •Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

- •Режим сторожевого таймера (watchdog timer).

- •Режим генерации импульсов заданной скважности.

- •2.1.1 Центральный процессор (cpu)

- •2.1.2. Периферийные устройства 8xc196kc и 8xc196kd

- •1. Повышение тактовой частоты.

- •2. Увеличение объема и пропускной способности подсистемы памяти.

- •3. Увеличение количества параллельно работающих исполнительных устройств.

- •4. Системы на одном кристалле (SoC) и новые технологии.

- •Программные симуляторы.

- •Режим генерации импульсов заданной скважности. (Модуль pca как генератор шим)

- •Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

3.6.3.Выполнение подпрограммы прерывания.

Система прерываний формирует аппаратный вызов (LCALL) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

в данный момент обслуживается запрос прерывания равного или высокого уровня приоритета;

текущий машинный цикл — не последний в цикле выполняемой команды;

выполняется команда RETI или любая команда, связанная с обращением к регистрам IЕ или IP

Отметим, что если флаг прерывания был установлен, но по одному из указанных выше условий не получил обслуживания и к моменту окончания блокировки уже сброшен, то запрос прерывания теряется и нигде не запоминается.

По аппаратно сформированному коду LCALL система прерывания помещает в стек только содержимое счетчика команд (PC) и загружает в него адрес вектора соответствующей подпрограммы обслуживания. По адресу вектора должна быть расположена команда безусловной передачи управления (JMP) к начальному адресу подпрограммы обслуживания прерывания. В случае необходимости она должна начинаться командами записи в стек (PUSH) слова состояния программы (PSW), аккумулятора, расширителя, указателя данных и т.д. и должна заканчиваться командами восстановления из стека (POP). Подпрограммы обслуживания прерывания должны завершаться командой RETI, по которой в счетчик команд перезагружается из стека сохраненный адрес возврата в основную программу. Команда RET также возвращает управление прерванной основной программе, но при этом не снимут блокировку прерываний, что приводит к необходимости иметь программный механизм анализа окончания процедуры обслуживания данного прерывания.

Вопрос #12 – “Система команд MCS-51. Команды пересылки.”

Система команд микроконтроллера предоставляет большие возможности обработки данных, обеспечивает реализацию логических, арифметических операций, а также управление в режиме реального времени.

В этой системе команд реализована побитная, потетрадная (4 бита), побайтовая (8 бит) и 16-разрядная обработка данных. Микросхемы семейства MCS-51 - это 8-разрядные микропроцессоры, а это означает, что ПЗУ, ОЗУ, регистры специального назначения, АЛУ и внешние шины имеют байтовую организацию. Двухбайтовые данные используются только регистром-указателем (DPTR) и счетчиком команд (PC).

В машинном коде команда занимает один, два или три байта в зависимости от типа адресации.

Команды выполняются за один, два или четыре (умножение и деление) машинных цикла.

Арифметические и логические команды могут быть выполнены только над содержимым регистра аккумулятора, поэтому исключительно важное значение в системе команд приобретают команды пересылки данных. С помощью этих команд можно скопировать содержимое любой ячейки памяти в регистр-аккумулятор или наоборот скопировать содержимое аккумулятора в любую ячейку памяти. Так как в микроконтроллере присутствует три независимых области памяти, то для обращения к ним введены различные команды:

копирование данных во внутреннем ОЗУ: MOV;

обмен данными аккумулятора с внутренним ОЗУ: XCH, XCHD

копирование из внешней памяти данных: MOVX

копирование данных из памяти программ: MOVC

Примеры использования команд пересылки данных:

Любая ячейка 256- байтового блока внутреннего ОЗУ данных может быть выбрана с использованием косвенно-регистровой адресации через регистры указатели R0 и R1 (выбранного банка рабочих регистров):

MOV A, @R0 ;Скопировать число из ячейки памяти с адресом, хранящемся в R0, в аккумулятор

MOV @R1, A ;Скопировать число из аккумулятора, в ячейку памяти с адресом, хранящемся в R1

Команды пересылки с прямой адресацией между ячейками памяти позволяют заносить содержимое порта в ячейку внутреннего ОЗУ или обмениваться содержимым ячеек внутреннего ОЗУ между собой без использования аккумулятора:

MOV 15, 25 ;Скопировать содержимое 25-й ячейки в 15-ю ячейку

Таблицы символов (кодов), записанные в ПЗУ программы могут быть скопированы в аккумулятор с помощью команд передачи данных с косвенной адресацией:

MOVC A, @A+DPTR ;Скопировать символ в аккумулятор

Ячейка адресного пространства 64 Кбайт внешнего ОЗУ также может быть выбрана с использованием косвенно-регистровой адресации через регистр указатель данных DPTR:

MOVX A, @DPTR ;Скопировать число из внешней ячейки памяти с адресом, ;хранящемся в DPTR, в аккумулятор

Содержимое аккумулятора может быть обменено с содержимым рабочих регистров выбранного банка:

XCH A, R0.

Кроме того, любой бит с прямой адресацией может быть скопирован в бит переноса и наоборот:

MOV C, AdrBit

Вопрос #13 - “Система команд MSC-51. Арифметика и логика”

Арифметика:

Формат команды: Описание: Меняет флаги

ADD A, <байт-источник> Сложение (A=A+байт) AC, C, OV

ADDC A, <байт-источник> Сложение с переносом (A=A+байт+C) AC, C, OV

SUBB A, <байт источника> Вычитание с заемом (A=A-байт-C) AC, C, OV

INC <байт> Инкремент

DEC <байт> Декремент

DIV AB Деление (A = A div B), B = A mod B) C, OV

MUL AB Умножение (A = ст. байт (A*B), B = мл. байт (A*B)) C, OV

OV - флаг переполнения (устанавливается, если произошло переполнение, иначе 0);

C - флаг переноса (устанавливается при появлении переноса из 7, иначе 0);

AC - флаг вспомогательного переноса (устанавливается при появлении переноса из 3, иначе 0).

Логика:

Формат команды: Описание:

ANL <байт-назначения>, <байт-источникa> Логическое "И" (пр. = пр. “И” ист.)

ORL <байт-назначения>, <байт-источникa> Логическое "ИЛИ" (пр. = пр. “ИЛИ” ист.)

XRL <байт-назначения>, <байт-источникa> Сложение по модулю 2 (пр. = пр. XOR ист.)

Вопрос #14 - “Десятичная коррекция. Двоично-десятичные преобразования”

Формат команды: Описание: Меняет флаги

DA A Десятичная коррекция аккумулятора для сложения AC, C

Команда "десятичная коррекция аккумулятора" упорядочивает 8-битовую величину в аккумуляторе A, полученную в результате выполненной команды сложения двух переменных, представленных в двоично-десятичном формате. Если значение битов 3-0 аккумулятора превышает 9 (xxxx1010B-xxxx1111B) или, если AC = "1", то к A прибавляется 06H, при этом получается двоично-десятичная цифра в младшем полубайте A. Указанное сложение не изменяет содержимое флага AC, но устанавливает в "1" содержимое флага переноса C, если перенос из поля младших четырех бит распространяется через все старшие биты A, в противном случае - не изменяет (C). Если C = "1", или если биты 7-4 A > 9 (1010xxxxB-1111xxxxB), то значение увеличивается на 6, создавая двоично-десятичную цифру в старшем полубайте A. При этом флаг C устанавливается (не изменяется), если имеется (отсутствует) перенос из бита 7 аккумулятора. Время выполнения команды 1 цикл.

Вопрос #15 - «команды передачи управления»

Группа представлена командами безусловного и условного переходов, командами вызова подпрограмм и командами возврата из подпрограмм.

В таблице также указаны тип команды (Т) в соответствии с таблицей, ее длина в байтах (Б) и время выполнения в машинных циклах (Ц).

|

Название команды |

Мнемокод |

Операция |

|

Короткий относительный переход внутри страницы в 256 байт |

SJMP rel |

(PC) (PC) + 2, (PC) (PC) +rel |

|

Переход, если аккумулятор равен нулю |

JZ rel |

(PC)(PC)+2, если (A)=0, то (PC)(PC)+rel |

|

Переход, если аккумулятор не равен нулю |

JNZ rel |

(PC)(PC)+2, если (A)≠0, то (PC)(PC)+rel |

|

Переход, если перенос равен единице |

JC rel |

(PC)(PC)+2, если (С)=1, то (PC)(PC)+rel |

|

Переход, если перенос равен нулю |

JNC rel |

(PC)(PC)+2, если (С)=0, то (PC)(PC)+rel |

|

Переход, если бит равен единице |

JB bit, rel |

(PC)(PC)+3, если (b)=l, то (PC)(PC)+rel |

|

Переход, если бит равен нулю |

JNB bit, rel |

(PC)(PC)+3, если (b)=0, то (PC)(PC)+rel |

|

Декремент прямо адресуемого байта и переход, если не нуль |

DJNZ ad, rel |

(PC) (PC) + 2, (ad) (ad) - 1, если (ad) ≠ 0, то (PC) (PC) + rel |

|

Длинный вызов подпрограммы |

LCALL adl6 |

(PC) (PC) + 3, (SP) (SP) +1, ((SP)) (PC0…7), (SP) (SP) + 1, ((SP)) (PC8…15), (PC) ad16 |

|

Возврат из подпрограммы |

RET |

(PC8…15) ((SP)), (SP) (SP) - 1, (PC0…7) ((SP)), (SP) (SP) – 1 |

|

Возврат из подпрограммы обработки прерывания |

RETI |

(PC8…15) ((SP)), (SP) (SP) - 1, (PC0…7) ((SP)), (SP) (SP) – 1 |

|

Пустая операция |

NOP |

(PC) (PC) + 1 |

Команда безусловного перехода LJMP (L – long – длинный) осуществляет переход по абсолютному 16-битному адресу, указанному в теле команды, т. е. команда обеспечивает переход в любую точку памяти программ. Действие команды AJMP (А – absolute – абсолютный) аналогично команде LJMP, однако в теле команды указаны лишь 11 младших разрядов адреса. Поэтому переход осуществляется в пределах страницы размером 2 Кбайт, при этом надо иметь в виду, что сначала содержимое счетчика команд увеличивается на 2 и только потом заменяются 11 разрядов адреса. В отличие от предыдущих команд, в команде SJMP (S – short – короткий) указан не абсолютный, а относительный адрес перехода. Величина смещения reI рассматривается как число со знаком, а, следовательно, переход возможен в пределах – 128...+127 байт относительно адреса команды, следующей за командой SJMP. Команда косвенного перехода JMP @A+DPTR позволяет вычислять адрес перехода в процессе выполнения самой программы.

Командами условного перехода можно проверять следующие условия:

JZ — аккумулятор содержит нулевое значение;

JNZ — аккумулятор содержит не нулевое значение

JC — бит переноса С установлен;

JNC — бит переноса С не установлен;

JB — прямо адресуемый бит равен 1

JNB — прямо адресуемый бит равен 0;

JBC — прямо адресуемый бит равен 1 и сбрасывается в нулевое значение при выполнении команды.

Все команды условного перехода рассматриваемых микро-ЭВМ содержат короткий относительный адрес, т. е. переход может осуществляться в пределах—128... +127 байт относительно следующей команды. Команда DJNZ предназначена для организации программных циклов. Регистр Rn или байт по адресу ad, указанные в теле команды, содержат счетчик повторений цикла, а смещение rеl — относительный адрес перехода к началу цикла. При выполнении команды содержимое счетчика уменьшается на 1 и проверяется на 0. Если значение содержимого счетчика не равно 0, то осуществляется переход на начало цикла, в противном случае выполняется следующая команда. Команда CJN удобна для реализации процедур ожидания внешних событий. В теле команды указаны "координаты" двух байт и относительный адрес перехода rel. В качестве двух байт могут быть использованы, например, значения содержимого аккумулятора и прямо адресуемого байта или косвенно адресуемого байта и константы. При выполнении команды значения указанных двух байт сравниваются и в случае, если они не одинаковы, осуществляется переход. Например, команда WAIT: CJNE A, P0, WAIT будет выполняться до тех пор, пока значения на линиях порта P0 не совпадут со значениями содержимого аккумулятора. Действие команд вызова процедур полностью аналогично действию команд безусловного перехода. Единственное отличие состоит в том, что они сохраняют в стеке адрес возврата. Команда возврата из подпрограммы RET восстанавливает из стека значение содержимого счетчика команд, а команда возврата из процедуры обработки прерывания RETI, кроме того, разрешает прерывание обслуженного уровня. Команды RET и RETI не различают, какой командой – LCALL или ACALL – была вызвана подпрограмма, так как и в том, и в другом случае в стеке сохраняется полный 16-разрядный адрес возврата. В заключение следует отметить, что большинство Ассемблеров допускают обобщенную мнемонику JMP – для команд безусловного перехода и CALL – для команд вызова подпрограмм. Конкретный тип команды определяется Ассемблером, исходя из "длины" перехода или вызова.

Вопрос #16 – “ Система команд МС8-51. Команды операций над битами ”

Эти команды устанавливают в "1"(SETB) или "0"(CLR) прямо адресуемый бит внутренней памяти данных, изменяют его значение на противоположенное(CPL), выполняют операции AND и OR над флагом переноса C и прямо адресуемым битом(ANL и ORL), осуществляют пересылку значения между флагом С и прямо адресуемым битом(MOV), осуществляют передачу управления по состоянию флага С или прямо адресуемого бита(JC, JNC, JB, JNB, JBC).

Команды этой группы, выполняющие логические операции и осуществляющие пересылку значения бита, изменяют значение флага С регистра PSW. Остальные команды на флаги не действуют.

Вопрос #17 – “Режимы работы МС8-51”

Регистр управления энергопотреблением - PCON (Power Control Register, адрес 87Н). Для кристаллов с HMOS технологией регистр имеет только один значащий бит – SMOD (управляет скоростью работы последовательного порта), кристаллы с CHMOS технологией регистр PCON:

- PCON.7 - бит удвоения скорости передачи (Double Baud Rate Bit, SMOD);

- PCON.6 и PCON.4 - зарезервированы (Reserved);

- PCON.3, PCON.2 - флаги общего назначения (General Purpose Flags, GF1, GF0);

- PCON.1 - бит режима микро потребления (Power Down Bit, PD);

- PCON.0 - бит холостого режима (Idle Mode Bit, IDL).

Режим холостого хода. Любая команда, по которой установится управляющий бит IDL, переведет МК в режим холостого хода. Продолжает работу внутренний генератор синхросигналов, регистры сохраняют свое значение, на выводах всех портов удерживается состояние которое на них было в момент перехода в режим холостого хода, На выводах ALE и ¬PSEN формируется уровень 1.

Режим пониженного энергопотребления. Перевод МК режим микро потребления возможен при установке бита PCON.1. Останавливается генератор синхросигналов, содержимое регистров, на выходных контактах портов удерживаются значения, выходы ALE и ¬PSEN сбрасываются, электропитание осуществляется через RST/VPD, напряжение электропитания (VCC) может быть отключено, перед выходом из режима оно должно быть восстановлено. Выход из режима возможен только по сигналу RST: переопределяются все регистры специальных функций, но содержимое РПД не изменяется.

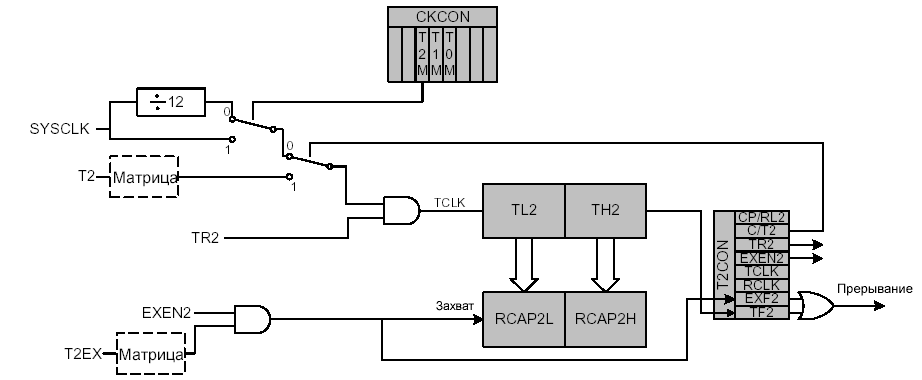

Вопрос #18 – “Таймер Т2. Режимы работы, программирование”

Таймер 2 является 16-битным таймером/счетчиком, представленным в пространстве SFR двумя однобайтными регистрами: TL2 (младший байт) и ТН2 (старший байт). Также как и таймеры 0 и 1, таймер 2 может использовать для работы системную тактовую частоту или вход внешней частоты. Источник тактирования определяется состоянием бита С/Т2 (T2CON. I). Обнуление этого бита означает использование тактовой частоты, деленной на восемь или двенадцать, в зависимости от бита выбора частоты Т2М регистра CKCON. Если С/Т2 установлен, то для счета используется задний фронт импульсов на входе внешней частоты Т2. Кроме того, таймер 2 может использоваться для запуска аналого-цифрового преобразователя ADC.

Режимы работы таймера 2 отличаются от режимов работы таймеров 0 и I. Он может функционировать в трех режимах: как 16-битный таймер/счетчик с захватом, как 16-битный таймер/ счетчик с автозагрузкой или в режиме генератора последовательной скорости. Режимы выбираются установкой битов в регистре T2CON, как показано в табл. 2.8.

Режим 0: 16-битный таймер/счетчик с захватом

При приходе заднего фронта импульса (перепада из верхнего логического уровня в нижний) на внешний вход Т2ЕХ значение из счетных регистров (ТН2 и TL2) перезаписывается в регистры захвата (RCAP2H и RCAP2L). Таймер 2 может использовать для счета системную тактовую частоту, тактовую частоту деленную на 12, а также внешние импульсы (по заднему фронту) на входе Т2. Обнуление бита С/Т2 (T2CON.I) означает использование для счета системных тактовых импульсов, деленных на I или на 12, в зависимости от состояния бита Т2М регистра CKCON. Если бит С/Т2 (T2CON.1) установлен, используются импульсы с внешнего входа "П. При переполнении регистров устанавливается флагТР2 (T2CON.7) и может быть сгенерировано прерывание, если оно разрешено. Режим 16-битного таймера/счетчика с захватом задается установкой битов CP/RL2 (T2CON.0), TR2 (T2CON.2) и EXEN2 (T2CON.3). Если бит EXEN2 (T2CON.3) не установлен (равен 0), импульсы входа Т2ЕХ игнорируются. На рис. 2.27 показана функциональная схема таймера 2 в режиме 0.

Режим 1: 16-битный таймер/счетчик с автозагрузкой

В этом режиме при переполнении счетчика устанавливается флаг TF2 и генерируется прерывание (если оно разрешено). Кроме того, шестнадцатеричное значение из регистров RCAP2H и RCAP2L автоматически перезаписывается в счетные регистры. Режим выбирается обнулением бита CP/RL2. Установка бита TR2 разрешает счет. В этом режиме таймер может использовать системные тактовые импульсы или внешний вход в качестве источника счетных импульсов. Источник выбирается битом С/Т2. Если установлен EXEN2, задний фронт импульса на входе Т2ЕХ вызывает перезагрузку, иначе вход Т2ЕХ игнорируется. На рис. 2.28 показана функциональная схема таймера 2 в режиме 1.

Режим 2: генератор двоичной скорости

Таймер 2 может использоваться для генерации скорости последовательного порта UART, когда он работает в режиме 1 или 3. В этом режиме таймер работает с автозагрузкой, перезагружая значения из регистров RCAP2H и RCAP2L. При этом флаг TF2 не устанавливается, и прерывания не генерируются. Событие переполнения используется для тактирования UART, при этом возможно совместное или независимое генерирование скорости последовательного обмена для передачи и приема. Управление режимом осуществляется установкой битов RCLK (T2CON.5) и/или TCLK (T2CON.4). Когда оба бита установлены, таймер 2 работает в режиме автозагрузки независимо от состояния бита CP/RL2. При этом скорость UART определяется в соответствии с выражением: может использоваться для запуска аналого-цифрового преобразователя ADC.

Скорость передачи = Скорость переполнения таймера 2 /16.

Следует отмстить, что во всех остальных режимах таймеры могут использовать системную тактовую частоту, деленную на 1 или 12, в зависимости от состояния бита Т2М регистра CKCON. Но в рассматриваемом случае, когда таймер 2 используется в качестве генератора последовательной скорости передачи, тактовая частота делится на 2.

Если необходимо использовать в качестве источника внешнюю частоту со входа Т2, необходимо установить бит С/Т2. Здесь можно использовать выражение:

Скорость передачи = FCLK / [32 х (65536--|RCAP2H:RCAP2L))1

В этом выражении входная частота, поступающая на внешний вывод Т2, обозначена FCLK. Величина |RCAP2H:RCAP2L1 -это 16-битная величина делителя. Как было сказано выше, в этом режиме не устанавливается флаг TF2 и не генерируются соответствующие прерывания, но если будет установлен бит EXEN2, то задний фронт на входе Т2ЕХ установит флаг EXF2, а также может быть сформировано прерывание таймера 2. Следовательно, вход Т2ЕХ в этом случае может использоваться, как дополнительный источник прерываний. На рис. 2.29 показана функциональная схема таймера 2 в режиме 2.

Вопрос #19 – “Массив программируемых счетчиков РСА. Режимы работы, программирование”

Несмотря на бурное развитие микроэлектроники за последнее время, по-прежнему во всем мире остаются популярными микроконтроллеры семейства MCS-51 фирмы Intel. Отличительной чертой последних моделей этих микросхем является наличие у них нового устройства РСА (Programmable Counter Array). Оно обеспечивает большие "временные" возможности по сравнению с обычными счетчиками-таймерами, которые имеются на кристалле, при этом достигается большая точность с меньшими затратами ресурсов ОЭВМ. РСА рекомендуется использовать для измерения таких параметров, как ширина импульса, частота, скважность, а так же для формирования прямоугольных импульсов на внешних выводах микроконтроллера. Это устройство имеется у моделей 80C51FA, 80C51FB, 80С51РС и 80C51GB.

РСА состоит из 16-разрядного таймера-счетчика и пяти 16-разрядных модулей сравнения-захвата (compare-capture), как показано на рисунке.

Рис.10. Таймер РСА

Таймер РСА является базой времени для пяти модулей и единственным таймером, обслуживающим РСА. На его счетный вход могут подаваться следующие сигналы:

тактовая частота/12,

тактовая частота/4,

сигнал переполнения от таймера 0,

внешний сигнал с контакта ЕС1(Р1.2).

Каждый модуль сравнения-захвата может работать в одном из следующих режимов:

захват по фронту и/или спаду,

программируемый таймер;

скоростной вывод,

генератор импульсов с заданной скважностью.

Кроме этого, четвертый модуль может работать в режиме сторожевого таймера (watchdog timer). Во время работы модуля в каком-либо режиме может формироваться запрос на прерывание. При этом все пять модулей и сигнал переполнения от РСА таймер-счетчика совместно используют один вектор прерывания. Внешние контакты устройства РСА и параллельного порта 1 совмещены. Контакты, которые не задействованы при работе РСА, могут использоваться для обычного ввода-вывода.