- •Глава 12. Схемотехника микропроцессорных цифровых устройств.

- •12.1. Классификация микропроцессоров и особенности их использования в измерительной аппаратуре.

- •12.2. Принципы организации микропроцессорных систем.

- •12.2.1. Принцип программного управления.

- •12.2.2. Структурная организация микропроцессорной системы.

- •12.2.3. Организация ввода-вывода в микропроцессорной системе.

- •12.3. Организация подсистемы памяти.

- •12.3.1. Оперативные запоминающие устройства.

- •12.3.2. Постоянные запоминающие устройства.

- •12.3.3. Увеличение информационной емкости модулей памяти.

- •12.4. Управляющие сигналы типового микропроцессора.

- •12.5. Интерфейсы микропроцессорных систем.

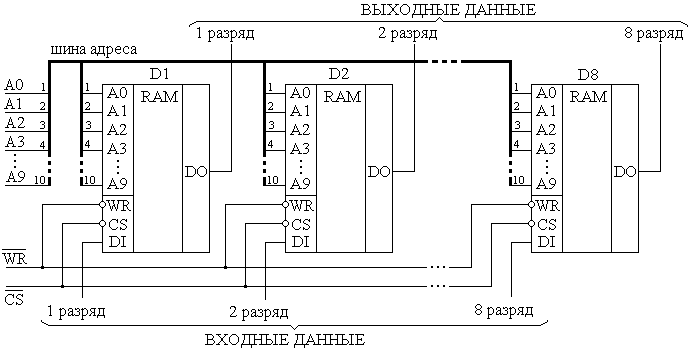

12.3.3. Увеличение информационной емкости модулей памяти.

Часто возникает

необходимость формирования модуля

памяти необходимого объема из имеющихся

микросхем фиксированной меньшей

информационной емкости. Микросхемы

памяти допускают наращивание общей

емкости памяти как путем наращивания

количества хранимых слов, так и путем

наращивания разрядности этих слов.

Наиболее простым в аппаратной реализации

является второй способ – наращивание

разрядности хранимых слов. Рассмотрим

структуру построения памяти 1к8

бит или 10248 бит.

Хранимые слова в такой памяти будут

восьмиразрядными, а адреса –

десятиразрядными (1024=210). Для

подобной организации необходимо

параллельно к шине адреса подключить

восемь микросхем (например, ОЗУ) 1к1

(рис. 12.10). На все микросхемыD1…D8

подается один и тот же адрес. Входы![]() и

и![]() микросхем объединяются. Каждая микросхема

хранит свой разряд слова. Запись

производится во все микросхемы

одновременно. Точно также и чтение

производится из всех микросхем

одновременно. Очевидно, что организация

такой памяти позволяет хранить 1024 байт

информации.

микросхем объединяются. Каждая микросхема

хранит свой разряд слова. Запись

производится во все микросхемы

одновременно. Точно также и чтение

производится из всех микросхем

одновременно. Очевидно, что организация

такой памяти позволяет хранить 1024 байт

информации.

Рис. 12.10. Схема модуля ОЗУ при наращивании разрядности хранимых слов.

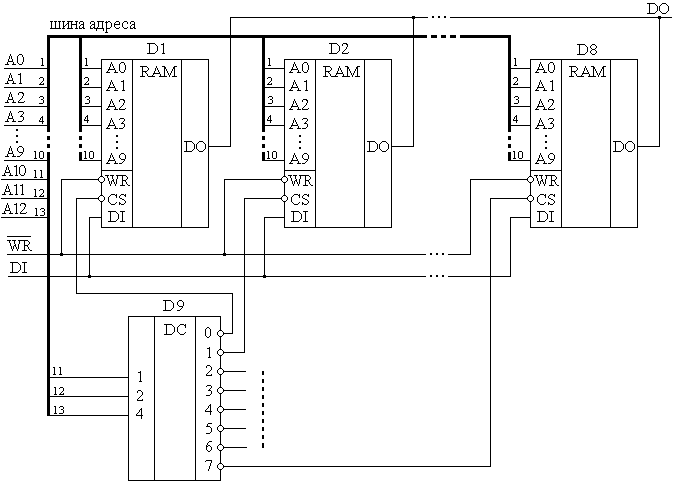

Другой вариант

организации схемы ОЗУ изображен на рис.

12.11, который позволяет увеличивать

объем памяти путемнаращивания

количества хранимых слов. Десять

младших разрядовA0…A9

адреса в рассматриваемой схеме также

одновременно подаются на все восемь

микросхемD1…D8.

При этом все входыDIмикросхем объединены в один общий вход

и все выходыDOобъединены

в один общий выход. Отсюда следует, что

в определенный момент времени должна

активизироваться только одна из восьми

микросхем. Для этих целей используются

три дополнительных адресных разрядаA10…A12,

которые подаются на дешифраторD9

выбора микросхемы памяти. С выхода

дешифратора сигналы активизации подаются

на раздельные входы![]() каждой микросхемы памяти. Поскольку

входы

каждой микросхемы памяти. Поскольку

входы![]() микросхем инверсные, то дешифратор

также должен иметь инверсные выходы.

Емкость подобной структуры определяется

как 8к1=81024

бит или 1024 байт. Полученная емкость

аналогична емкости модуля ОЗУ, построенного

по предыдущей схеме. При этом для

адресации к ней требуется большее

количество адресных линий в шине адреса.

Структура с наращиванием количества

хранимых слов обладает недостатком,

заключающимся в том, что требуется

введение в схему дополнительных

дешифраторов. При современном уровне

интеграции микросхем этот недостаток

можно считать незначительным. Однако

такая структура имеет и преимущество,

которое заключается в том, что она может

использоваться в тех случаях, когда

разрядность шины адреса превышает

количество адресных входов отдельных

микросхем.

микросхем инверсные, то дешифратор

также должен иметь инверсные выходы.

Емкость подобной структуры определяется

как 8к1=81024

бит или 1024 байт. Полученная емкость

аналогична емкости модуля ОЗУ, построенного

по предыдущей схеме. При этом для

адресации к ней требуется большее

количество адресных линий в шине адреса.

Структура с наращиванием количества

хранимых слов обладает недостатком,

заключающимся в том, что требуется

введение в схему дополнительных

дешифраторов. При современном уровне

интеграции микросхем этот недостаток

можно считать незначительным. Однако

такая структура имеет и преимущество,

которое заключается в том, что она может

использоваться в тех случаях, когда

разрядность шины адреса превышает

количество адресных входов отдельных

микросхем.

Рис. 12.11. Схема модуля ОЗУ при наращивании количества хранимых слов.

На практике часто используется комбинированная структура, объединяющая наращивание как разрядности, так и количества хранимых слов. В этом случае формируется некоторое количество однотипных групп микросхем, объединенных в структуру с наращиванием разрядности слов. Далее эти группы объединяются в единую структуру с наращиванием количества хранимых слов. Разрядность слов комбинированной структуры определяется разрядностью слова одной группы микросхем, включенных по схеме наращивания разрядности.