posobie5_1mua

.pdf

150

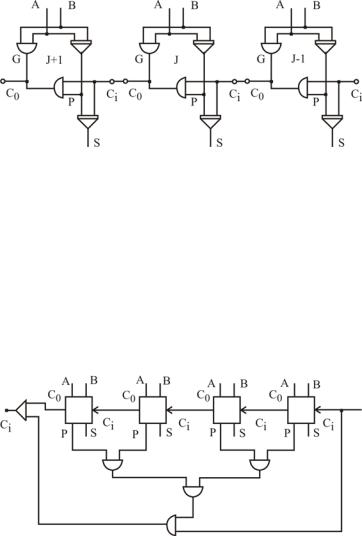

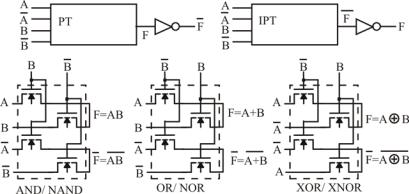

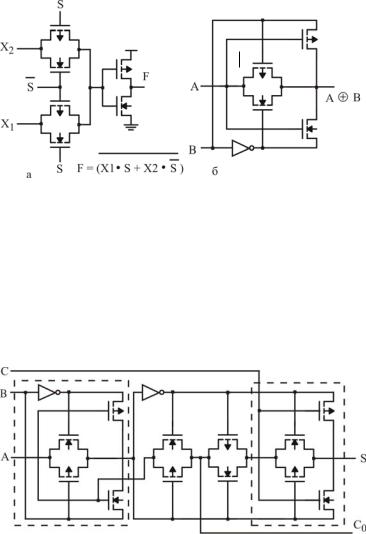

ция разрешения распространения (прохождения) переноса, совпадающая с поразрядной суммой слагаемых Р = XOR(A, B). Выход переноса C0 = Ci P + G и поскольку P и G взаимоисключающие, то дизъюнкция может быть проводной (соединением выходов). В результате схема параллельного сумматора имеет вид, показанный на рис.4.7.

Рис.4.7 Параллельный сумматор с уменьшенной задержкой

Отметим, что в составе сумматора, в том числе в составе цепи переноса, появились вентили AND без инвертирования. Небольшим преобразованием можно перейти к инвертирующим вентилям, но исключить вентиль с двумя входами в цепи переноса невозможно, что существенно увеличивает общее время задержки сигнала переноса.

В многоразрядных параллельных сумматорах широко применяют логические методы ускорения переноса, за счет минимизации количества проходимых сигналом переноса вентилей. Один из методов – групповой перенос – предусматривает специальные цепи ускоренного переноса (рис.4.8). При совпадении разрешения переноса у нескольких соседних сумматоров сигнал переноса может обойти их по цепи ускоренного переноса.

Рис.4.8. Параллельный сумматор с ускоренным переносом

151

В этом случае комбинационные вентили также не оптимальны, поскольку требуются двухвходовые вентили.

4.3. Модификации комбинационных логических схем

Один из недостатков комбинационных логических схем обусловлен «слабостью» p-МОП по сравнению с n-МОП. Поэтому понятно стремление максимально уменьшить использование p-МОП, по крайней мере, в ответственных местах схем.

Другой недостаток комбинационных логических схем заключается в невозможности инвертировать сигнал на входе вентиля. Во многих случаях наряду с прямым сигналом целесообразно иметь и инвертированный сигнал. Такие возможности предоставляют дифференциальные логические схемы, где каждый вентиль имеет прямой и инвертированный выход. Однако простое удвоение сигналов в комбинационных КМОПвентилях нецелесообразно, поскольку они уже содержат удвоенное количество транзисторов. Для решения проблемы предложены каскодные переключательные логические схемы.

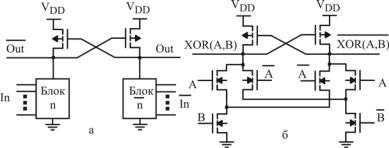

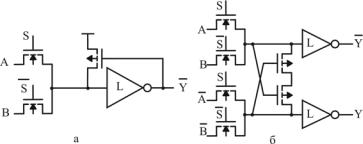

Каскодные переключательные логические схемы (СVSL) или дифференциальные каскодные переключательные логические схемы представлены на рис.4.9. В составе вентиля содержится два блока n-МОП, с прямым и инверсным выходами, а его блоки p-МОП содержат по одному p-МОП, затворы которых подсоединены к выходам противоположных блоков n-МОП

(рис.4.9,а).

Рис.4.9. CVSL вентили: а – структура вентиля; , – XOR вентиль

В результате основное свойство КМОП – отсутствие сквозных токов сохраняется, но появляется гистерезис в передаточной характеристике. Подобная структура ускоряет переходные процессы при переключении вентилей и в некоторых случаях расширяет их функциональные возможно-

152

сти. Так XOR и NXOR вентиль (рис.4.9,б), в совокупности содержат всего 8 МОП.

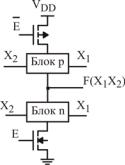

Тактируемые комбинационные логические схемы. Примером тактируемого инвертора является драйвер (см. рис.4.1,а). По такому же принципу можно строить и более сложные логические схемы, рис.4.10.

Рис.4.10. Тактируемый вентиль с двумя входами

Он находится в активном состоянии, пока на разрешающем входе Е высокий уровень. При изменении уровня разрешающего сигнала выходной потенциал некоторое время сохраняется. Такие схемы отличаются от классических комбинационных схем наличием третьего состояния, возможностью объединения по выходу. В некотором смысле они аналогичны проходным и динамическим логическими схемами.

153

Глава 5. Проходные логические схемы

В проходных логических схемах применяются МОП- и КМОПключи. Использование ключей одного типа – однополярных ключей (проходных вентилей) позволяет исключить p-МОП, однако возникает проблема полной передачи единичного сигнала. В комплементарных КМОПключах (передаточных вентилях) используются n-МОП и p-МОП, но сохраняется проблема передачи сигнала по длинным цепочкам ключей.

5.1. Однополярные проходные логические схемы

Проходные логические схемы, использующие однополярные ключи, обладают важными преимуществами. Во-первых, в элементе всего один транзистор вместо двух в инверторе, во-вторых, у ключа три вывода вместо четырех у инвертора. Поэтому можно добиться более высокой плотности упаковки.

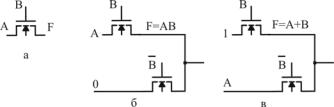

Проходные вентили. В схемах с однополярными n-МОП ключами (рис.5.1), как и КМОП-вентилях, исключаются сквозные токи. Если к некоторому узлу подключены несколько ключей, то допускается открывание только одного из них. При двух ключах, (рис.5.1,б) и (рис.5.1,в) они управляются парафазно.

Рис.5.1. Проходные вентили: а – ключ; б – схема И; в – схема ИЛИ

Простейший ключ на одном n-МОП (рис.5.1,а) соединяет выход F со входом только при высоком уровне сигнала управления В = 1, а при В = 0 потенциал выхода сохраняет состояние, т.е. обладает памятью.

Два n-МОП ключах с парафазным управлением позволяют реализовать схемы И и ИЛИ. В этом случае выход подсоединен ко входу при любом значении сигнала управления В, а логическая функция элемента зависит от сигналов на коммутируемых входах. Так, подавая на ключ с инверсным управлением нуль имеем функцию И (рис.5.1,б), а подавая на прямой вход единицу имеем функцию ИЛИ (рис.5.1,в).

154

Существенным отличием ключевых логических элементов от вентилей является отсутствие в них инвертирования. Иногда такое свойство упрощает построение схем. При необходимости инвертирование достигается введением дополнительных элементов.

Дифференциальные проходные логические схемы. Дифферен-

циальные проходные однополярные вентили содержат прямые и инверсные входы и выходы (рис.5.2).

Рис.5.2. Дифференциальные проходные вентили.

С помощью четырех однополярных n-МОП ключей удается реализовать любую прямую и инверсную симметричную логическую функцию двух переменных . Это позволяет сократить количество вентилей в составе одноразрядного сумматора.

Одноразрядный однополярный сумматор. Использование при-

веденных проходных вентилей (см. рис.5.2) определяет вид одноразрядного сумматора. Функция суммы получается из двух схем XOR

S = (A B) C , |

(5.1) |

а функция переноса из схем AND, OR и XOR |

|

C0 = AB +(A B)C |

(5.2) |

Вариант реализации сумматора приведен на рис.5.3. Он содержит 28 МОП.

155

Рис.5.3. Одноразрядный сумматор на однополярных проходных элементах

Особенности однополярных проходных логических схем. Ос-

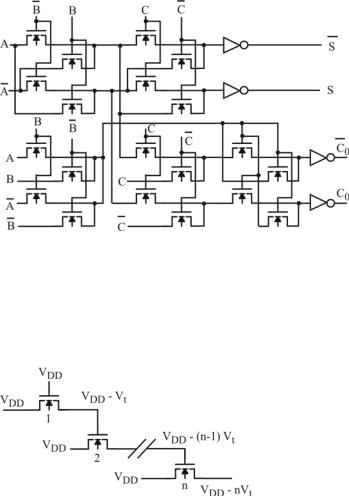

новным ограничением однополярных проходных вентилей является снижение выходного перепада на выходе ключа. При использовании n-МОП ключей высокий уровень в цепочке снижается после каждого элемента на величину порогового напряжения (рис.5.4).

Рис.5.4 Уменьшение высокого уровня в цепочке n-МОП ключей.

Проходные полнодиапазонные вентили. Недостаток проход-

ных вентилей – неполная передача высокого уровня – может быть устранен. Для этого выход проходного вентиля подсоединяют к высокому потенциалу питания VDD через p-МОП, управляемый проинвертированным сигналом самого проходного вентиля (рис.5.5,а).

156

Рис.5.5. Восстановление высокого уровня в проходном (а) вентиле и дифференциальном проходном (б) вентилях.

В случае использования дифференциальных однополярных проходных вентилей, управление p-МОП осуществляется с инверсного выхода

(рис.5.5,б).

5.2.Комплементарные проходные логические схемы

Вкомплементарной проходных вентилях используются КМОПключи, что позволяет исключить потерю перепада сигналов.

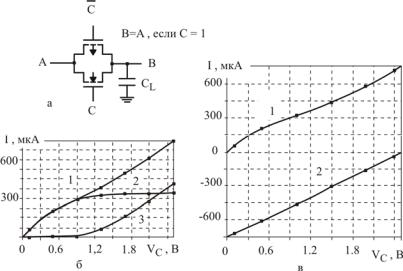

Свойства КМОП-ключа. КМОП-ключи состоят из двух транзисторов n-МОП и p-МОП для обеспечения полной передачи напряжения от входа А до выхода В (рис.5.6,а). При низком напряжении на управляющем входе С оба транзистора закрыты. При высоком управляющем сигнале и n-МОП и p-МОП открыты, но в зависимости от напряжения на входе они работают в разных режимах: один – как истоковый повторитель, другой – как усилитель с общим истоком. Так при А = 0 (рис.5.6,б) в зависимость тока втекающего в ключ из узла В, от напряжения на разряжаю-

щейся емкости CL, (кривая 1) дают вклад ток n-МОП (кривая 2) и ток p- МОП (кривая 3). Когда потенциал на выходе В высокий, через оба транзистора текут примерно равные токи, но когда потенциал на выходе приближается к нулевому, ток течет в основном через n-МОП. При А = 1 ситуация прямо противоположная – при потенциале выхода близком к единице, ток протекает в основном через p-МОП.

157

Рис.5.6. КМОП-ключ: а – электрическая схема; б – проходная ВАХ и ее составляющие при А = 0; в – проходная ВАХ при А = 0 (кривая 1) и при А = 1 (кривая 2).

Выбором размеров (ширины) каналов можно выравнять токи через открытый КМОП-ключ, заряжающие и разряжающие емкость CL выходного узла В (рис 5.6,в). В этом случае сопротивление ключа в первом приближении равно RS ≈ 1/(βVDSat).

Вентили на КМОП-ключах. При построении схем, где не требуется инвертирование (мультиплексоров, демультиплексоров и т.п.) целесообразно использовать вентили на КМОП-ключах в силу их экономичности.

В мультиплексорах в каждом канале достаточно одного КМОПключа (рис.5.7,а).

158

Рис.5.7. Логические схемы на КМОП-ключах: а – MUX; б – XOR

Операция ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR) также выполняется очень экономно (рис.5.7,б). Поскольку КМОП-ключи передают сигнал без усиления, то совместно с ними используется КМОП-усилитель (инвертор), необходимый и для формирования управления p-МОП, и для инвертирования сигнала в ключевых схемах.

Одноразрядный сумматор. Выигрыш в аппаратуре при использовании КМОП-ключей наиболее очевиден в схеме одноразрядного сумматора (рис.5.8). Для него достаточно 14 транзисторов (а с учетом выходных вентилей – 18 транзисторов).

Рис.5.8. Одноразрядный сумматор на комплементарных ключах.

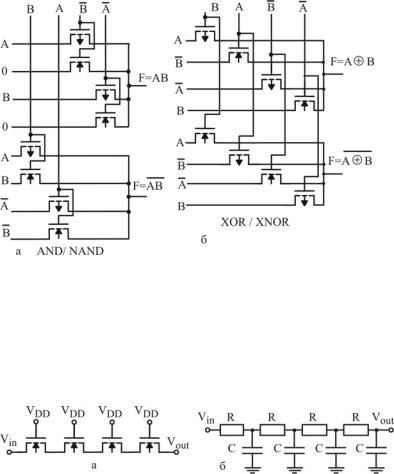

Дифференциальные логические схемы на КМОП-ключах. Как и однополярные проходные логические схемы дифференциальные схем с КМОП-ключами позволяет достаточно экономно выполнять основные логические функции (рис.5.9).

159

Рис.5.9. Симметричные вентили на КМОП-ключах: а – AND/NAND; б –

XOR/XNOR

Особенности проходных логических схем. Простота однопо-

лярных и комплементарных проходных логических схем связана с отсутствием усиления. Сигнал, проходящий по цепочке вентилей (рис.5.10,а), должен заряжать емкости узлов через возрастающее сопротивление

(рис.5.10,б).

Рис.5.10. Цепь ключей: а – электрическая схема; б –эквивалентная схема

Поэтому задержка квадратично зависит от количества ключей N в цепоч-

ке t0 ≈ N2RC.