Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

28.02.2021

Руководитель

Доцент БИС

___________ Мальчуков А.Н.

28.02.2021

Томск 2021

ЦЕЛЬ РАБОТЫ

Целью работы является изучение основных инструментов САПР QuartusII и получение умения моделировать в ней работу схем на основе простых логических элементов.

ПОСТАНОВКА ЗАДАЧИ

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1. Собрать на холсте и промоделировать работу схем 2И, 2ИЛИ, 2искл. ИЛИ, 2И-НЕ и 2ИЛИ-НЕ в двух режимах;

2. Описать логические элементы из п.1 на VHDL;

3.

Собрать на холсте схему логического

выражения согласно варианту и

промоделировать её работу в двух режимах:

F= ;

;

4. Описать выражение из п.3 с помощью VHDL.

1. Устройство 2И

1.1 Таблица истинности

В таблице 1.1 представлена таблица истинности для данного устройства.

Таблица 1.1 - Таблица истинности

Вход A |

Вход B |

Выход C |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1.2 Формула

Формула 2И: A ∧ B = C

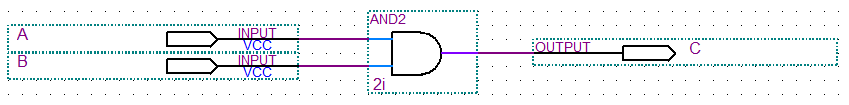

1.3 Функциональная схема

Функциональная схема для элемента 2И представлена на рисунке 1.3.1

Рисунок 1.3.1 – Функциональная схема для элемента 2И

1.4 Код на HDL

Ниже представлен код для элемента 2И:

library ieee;

use ieee.std_logic_1164.all;

entity Vhd is

port (

A: in std_logic;

B: in std_logic;

C: out std_logic;

);

end;

architecture lab1 of Vhd is

begin

C <= A and B;

end;

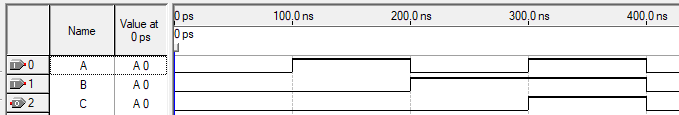

1.5 Моделирование

Результат моделирования схемы в режиме Timing представлен на рисунке 1.5.1

Рисунок 1.5.1 – Результат моделирования схемы 2И в режиме Timing

Результат моделирования схемы в режиме Functional представлен на рисунке 1.5.2

Рисунок 1.5.1 – Результат моделирования схемы 2И в режиме Functional

Из результата моделирования можем увидеть, что результаты идентичны таблице истинности.

2 Устройство 2или

2.1 Таблица истинности

В таблице 2.1 представлена таблица истинности для данного устройства.

Таблица 2.1 - Таблица истинности

Вход A1 |

Вход B1 |

Выход C1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

2.2 Формула

Формула для логического элемента 2ИЛИ: A1 ∨ B1 = C1

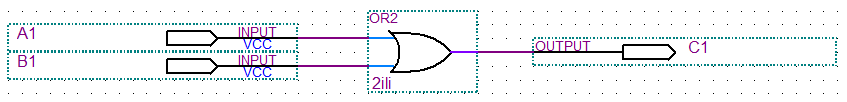

2.3 Функциональная схема

Функциональная схема для элемента 2ИЛИ представлена на рисунке 2.3.1.

Рисунок 2.3.1 – Функциональная схема для схемы 2ИЛИ

2.4 Код на HDL

Код для элемента 2ИЛИ представлен ниже:

library ieee;

use ieee.std_logic_1164.all;

entity Vhd is

port (

A1: in std_logic;

B1: in std_logic;

C1: out std_logic;

);

end;

architecture lab1 of Vhd is

begin

C1 <= A1 or B1;

end;

2.5 Моделирование

Результат моделирования схемы в режиме Timing представлен на рисунке 2.5.1

Рисунок 2.5.1 – Результат моделирования схемы 2ИЛИ в режиме Timing

Результат моделирования схемы в режиме Functional представлен на рисунке 2.5.2

Рисунок 2.5.2 – Результат моделирования схемы 2ИЛИ в режиме Functional

Из результата моделирования можем увидеть, что результаты идентичны таблице истинности.

3 Устройство 2искл. Или

3.1 Таблица истинности

В таблице 3.1 представлена таблица истинности для данного устройства.

Таблица 3.1 - Таблица истинности

Вход A2 |

Вход B2 |

Выход C2 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

3.2 Формула

Формула для логического элемента 2искл. ИЛИ: A2 ⊕ B2 = C2

3.3 Функциональная схема

Функциональная схема для элемента 2искл. ИЛИ представлена на рисунке 3.3.1.

Рисунок 3.3.1 – Функциональная схема элемента 2искл. ИЛИ

3.4 Код на HDL

library ieee;

use ieee.std_logic_1164.all;

entity Vhd is

port (

A2: in std_logic;

B2: in std_logic;

C2: out std_logic

);

end;

architecture Vhd of LAB1 is

begin

C2 <= A2 xor B2;

end;

3.5 Моделирование

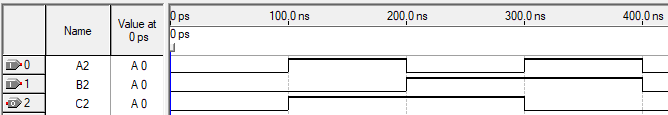

Результат моделирования схемы в режиме Timing представлен на рисунке 3.5.1

Рисунок 3.5.1 – Результат моделирования схемы 2искл. ИЛИ в режиме Timing

Результат моделирования схемы в режиме Functional представлен на рисунке 3.5.2

Рисунок 3.5.2 – Результат моделирования схемы 2искл. ИЛИ в режиме Functional

Из результата моделирования можем увидеть, что результаты идентичны таблице истинности.

4 Устройство 2и-не

4.1 Таблица истинности

В таблице 4.1 представлена таблица истинности для данного устройства.

Таблица 4.1 - Таблица истинности

Вход A3 |

Вход B3 |

Выход C3 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

4.2 Формула

Формула

для логического элемента 2И-НЕ: C3

=

4.3 Функциональная схема

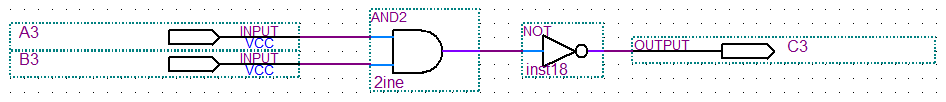

Функциональная схема для элемента 2И-НЕ представлена на рисунке 4.3.1.

Рисунок 4.3.1 – Функциональная схема элемента 2И-НЕ

4.4 Код на HDL

Код для элемента 2И-НЕ представлен ниже:

library ieee;

use ieee.std_logic_1164.all;

entity Vhd is

port (

A3: in std_logic;

B3: in std_logic;

C3: out std_logic

);

end;

architecture Vhd of LAB1 is

begin

C3 <= A3 nand B3;

end;

4.5 Моделирование

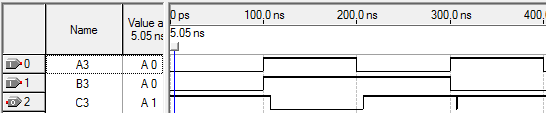

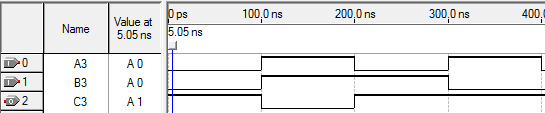

Результат моделирования схемы в режиме Timing представлен на рисунке 4.5.1

Рисунок 4.5.1 – Результат моделирования схемы 2И-НЕ в режиме Timing

Результат моделирования схемы в режиме Functional представлен на рисунке 4.5.2

Рисунок 4.5.2 – Результат моделирования схемы 2И-НЕ в режиме Functional

Из результата моделирования можем увидеть, что результаты идентичны таблице истинности.