5. Описание для каждой созданной схемы

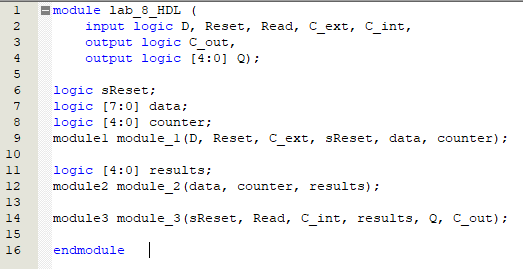

На рисунке 22 приведен код общей схемы. Ниже описывается каждый блок по отдельности.

Рисунок 22 – Код общей схемы

Общая схема из RTL viewer для языка SystemVerilog приведена на рисунке 23.

Рисунок 23 – Общая схема из RTL viewer для кода

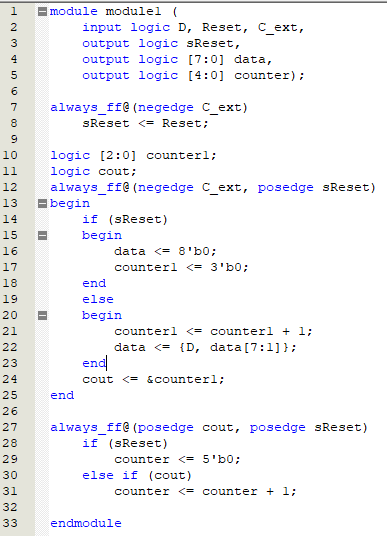

На рисунке 24 будет представлен код входного блока устройства, описанное на языке SystemVerilog. Данный блок принимает сигналы D (сигнал поступления кода операции и данных), Reset (сигнал сброса), C_ext (внешний синхроимпульс), а выводить сигналы sReset (синхронизированный сигнал сброса), data (шина данных, записанных в регистр), а также counter (значение счётчика). Сигнал sReset будет необходим в выходном блоке, т.к. там есть два устройства хранения (D-триггер и параллельный регистр). Сигналы от шины data будут определять, что будет делать операционный блок и с какими данными, в одном случае из четырех будет применен counter. Внутри входного блока есть два записывающих устройства и два счётчика. Хранение синхронизированного сигнала сброса реагирует только на задний фронт сигнала C_ext, а остальные будут реагировать на него и на сигнал sReset. Регистр сдвигает свои данные влево. Первый счётчик будет считать заполнение регистра, а второй будет реагировать на заполненность регистра (полный круг у первого счётчика) и отслеживать количество выполненных операций.

Рисунок 24 – Код входного блока

Схема из RTL viewer для входного блока языка SystemVerilog приведена на рисунке 25.

Рисунок 25 – Схема из RTL viewer для кода входного блока

Код операционного блока приведен на рисунке 26. На вход ему поступают сигналы d, а также значение счётчика counter. Выход с данного блока идет сразу на выходной.

Рисунок 26 – Код операционного блока

Схема из RTL viewer для операционного блока языка SystemVerilog приведена на рисунке 27.

Рисунок 27 – Схема из RTL viewer для кода операционного блока

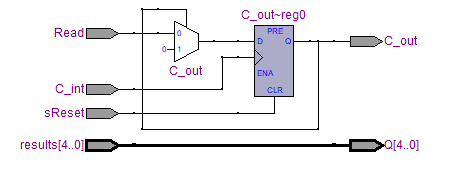

Код выходного блока представлена на рисунке 28. В выходной блок поступают сигналы sReset (синхронизированный сигнал сброса), Read (чтение), C_int (внутренний синхроимпульс), а из него выходят Q (выходные данные) и C_out (сигнал синхронизации выведенных данных). Данный блок записывает данные операционного блока по сигналу Read синхронизируемому по внутреннему синхроимпульсу. На следующий такт C_int произойдет изменение сигнала C_out, а именно появление переднего фронта, которое оповещает о выданных данных. Это достигается за счёт триггера записи сигнала чтения. Данный блок выдает готовый результат всего вычислительного блока.

Рисунок 28 – Код выходного блока

Схема из RTL viewer для выходного блока языка SystemVerilog приведена на рисунке 29.

Рисунок 29 – Схема из RTL viewer для кода выходного блока

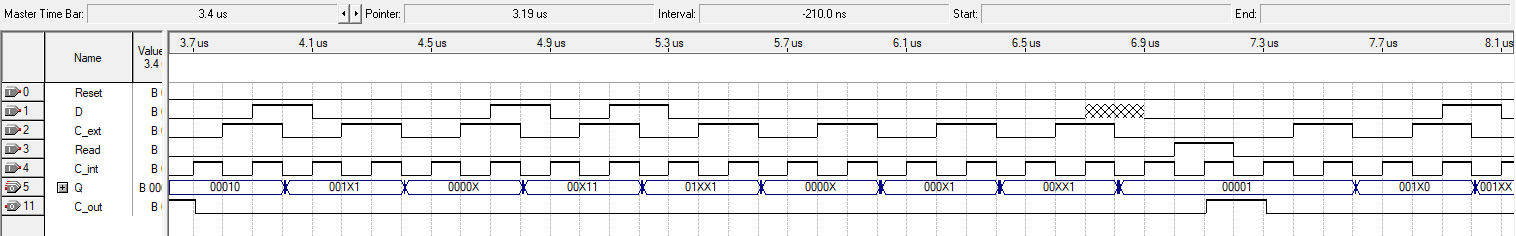

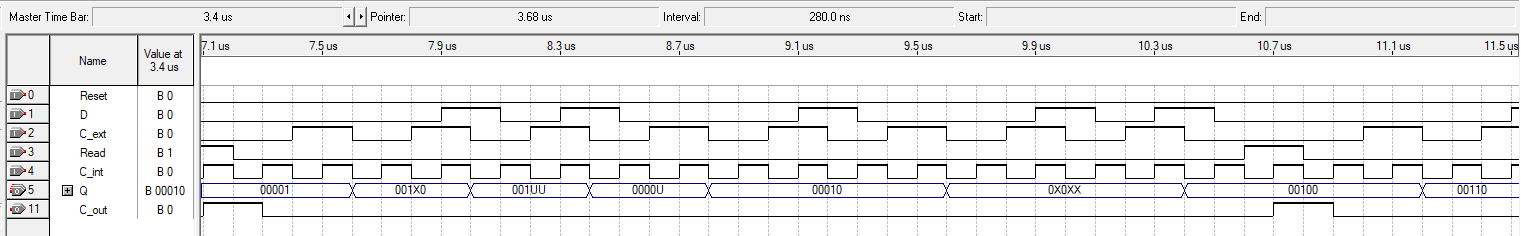

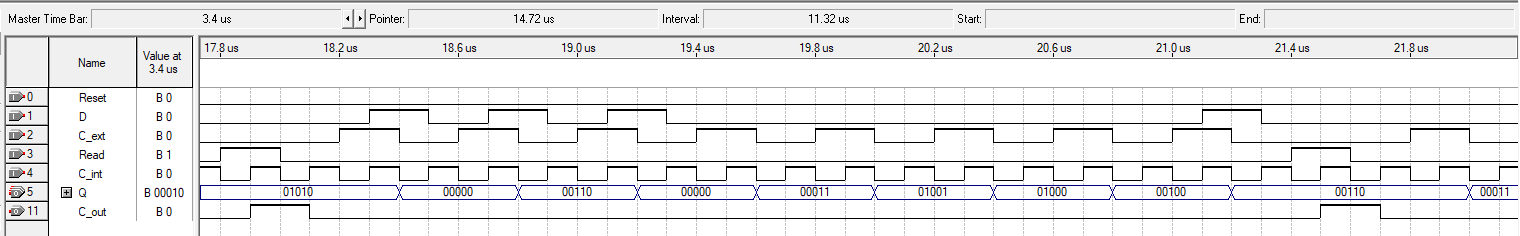

Результаты моделирования кода представлены на рисунках 30 – 37.

Рисунок 30 – Моделирование кода первых входных данных

Рисунок 31 – Моделирование кода вторых входных данных

Рисунок 32 – Моделирование кода третьих входных данных

Рисунок 33 – Моделирование кода четвертых входных данных

Рисунок 34 – Моделирование кода пятых входных данных

Рисунок 35 – Моделирование кода шестых входных данных

Рисунок 36 – Моделирование кода седьмых входных данных

Рисунок 37 – Моделирование кода восьмых входных данных

Результаты моделирований сходятся с ожидаемыми, а также результатами полученными при моделировании устройства.

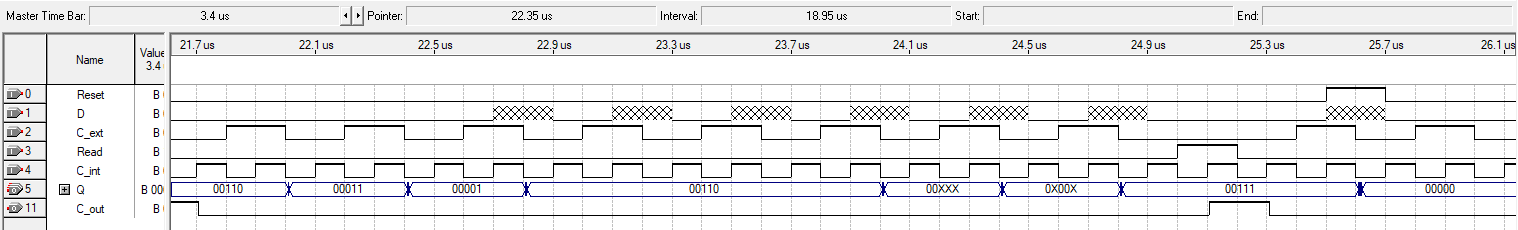

Функциональное моделирование кода приведено на рисунках 38 – 45.

Рисунок 38 – Функциональное моделирование кода первых входных данных

Рисунок 39 – Функциональное моделирование кода вторых входных данных

Рисунок 40 – Функциональное моделирование кода третьих входных данных

Рисунок 41 – Функциональное моделирование кода четвертых входных данных

Рисунок 42 – Функциональное моделирование кода пятых входных данных

Рисунок 43 – Функциональное моделирование кода шестых входных данных

Рисунок 44 – Функциональное моделирование кода седьмых входных данных

Рисунок 45 – Функциональное моделирование кода восьмых входных данных

ВЫВОДЫ

В процессе данной работы было изучено совместное применение устройства средней степени интеграции.

Вначале была разработана обобщенная функциональная схема вычислительного устройства, состоящая из трёх блоков: входной блок, операционный блок, выходной блок. Во входном блоке имелось устройство записи сигнала сброса, устройство последовательной записи, счетчик сигналов и счетчик операций. В операционном блоке имелось устройство проверки 4b5b-кода, блок побитовой операции эквивалентности, блок сумматора с единицей на входе переноса. Выходной блок состоял из устройства записи сигналов read.

Также по данной обобщенной функциональной схеме была собрана функциональная схема и промоделирована по созданному плану. Для каждой части операционного блока была создана таблица функционирования. Был создан код на языке SystemVerilog, который описывает данное устройство. Он было разбит на три модуля, которые в общем файле взаимодействовали друг с другом. Код был промоделирован по плану моделирования.

Результаты моделирований соответствуют ожидаемым.