2.1 Таблица функционирования

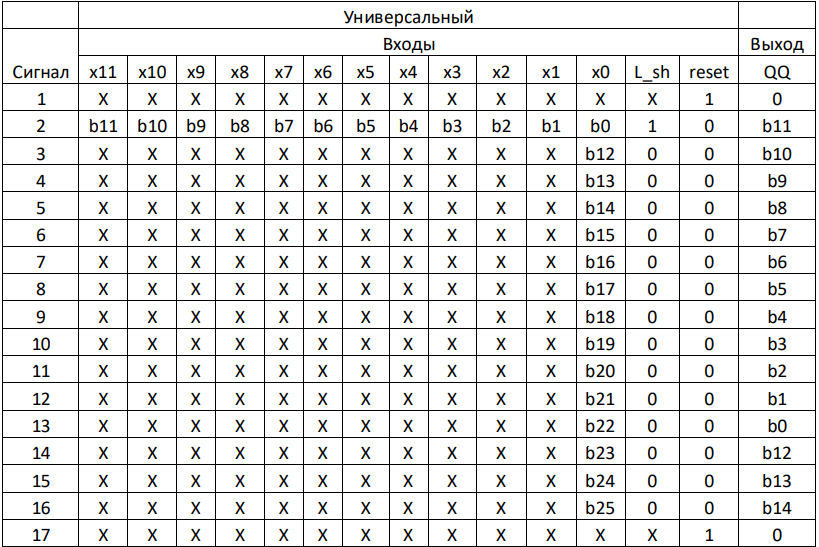

Таблица 2 – комбинации нулей и единиц для универсального регистра.

Таблица 2 – Универсальный регистр

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА УНИВЕРСАЛЬНОГО РЕГИСТРА

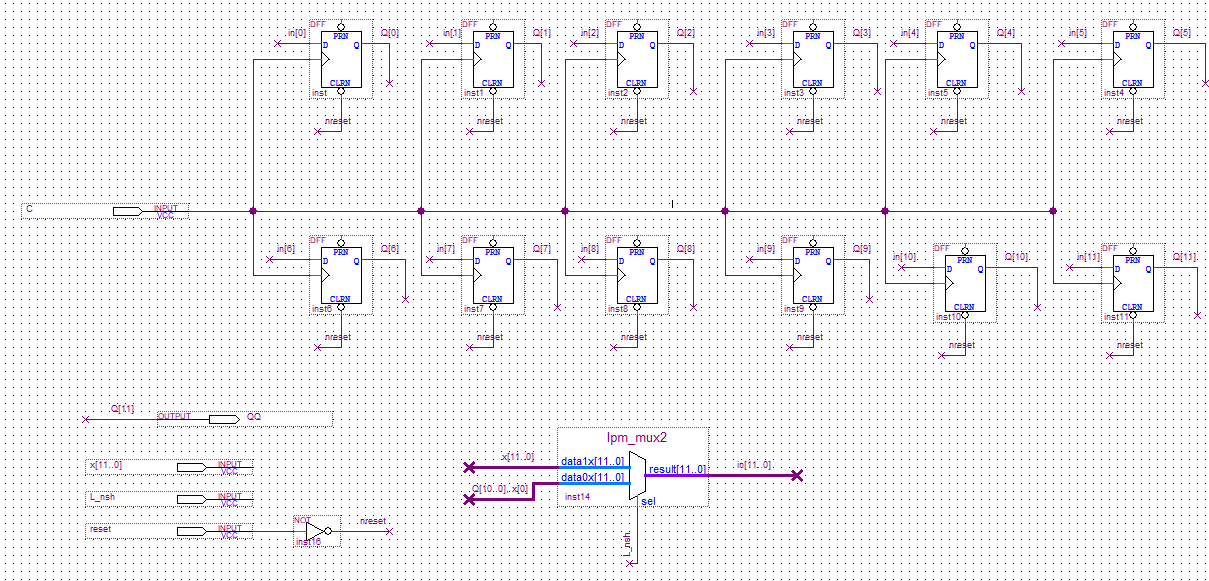

На рисунке 9 представлена функциональная схема универсального регистра.

Рисунок 9 – Функциональная схема универсального регистра

2.3 МОДЕЛИРОВАНИЕ УНИВЕРСАЛЬНОГО РЕГИСТРА

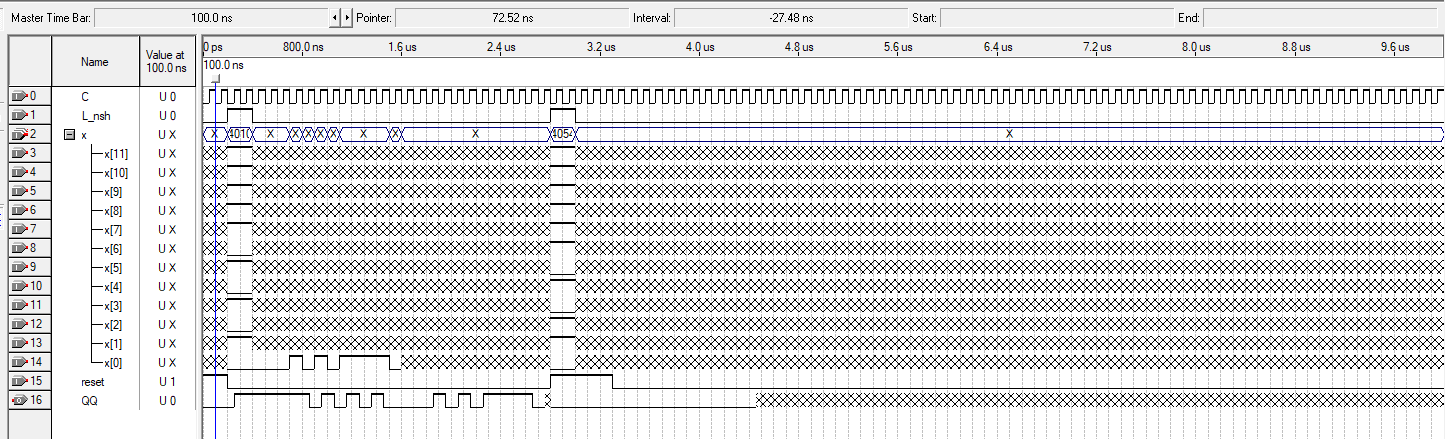

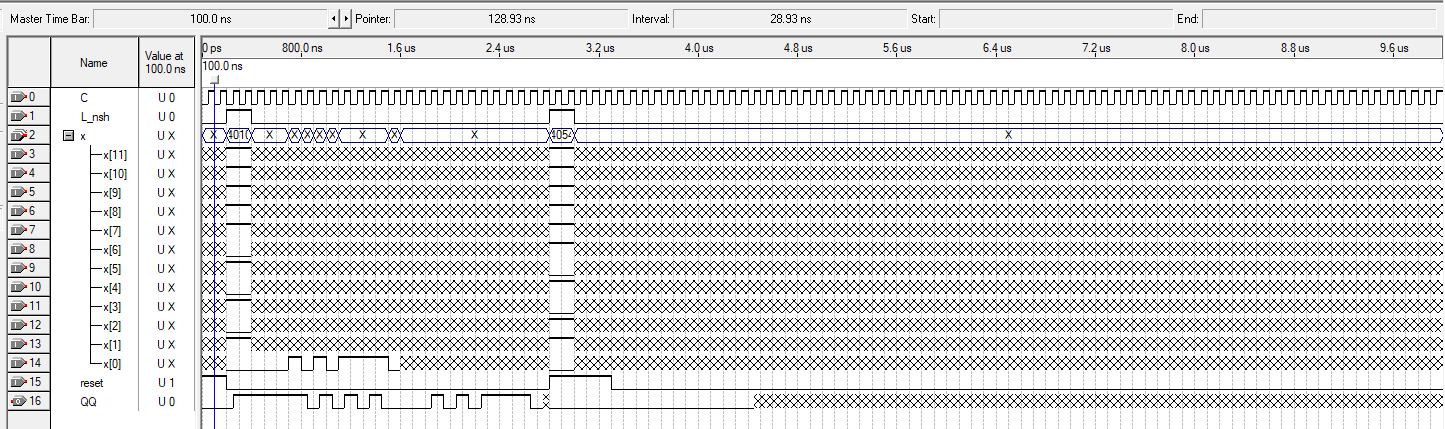

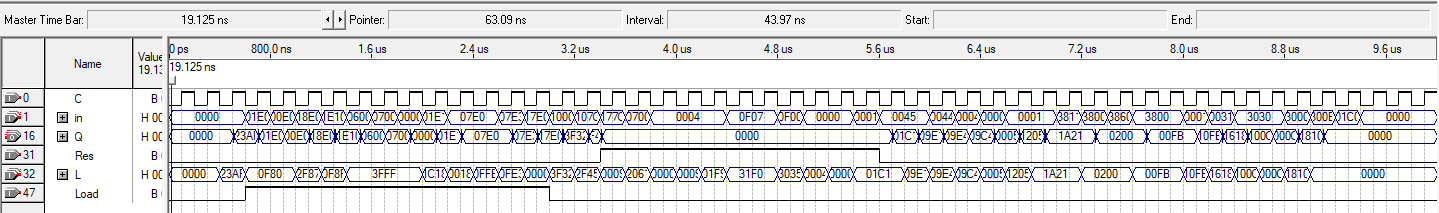

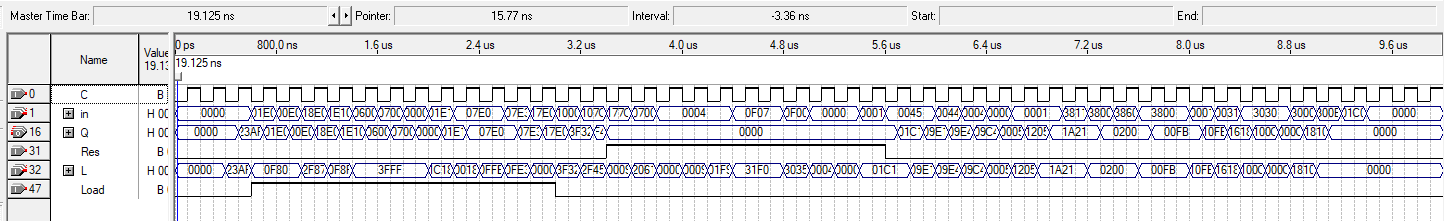

Моделирование представлено на рисунках 10, 11 в разных режимах работы.

Рисунок 10 – Моделирование, режим Timing

Рисунок 11 – Моделирование, режим Functional

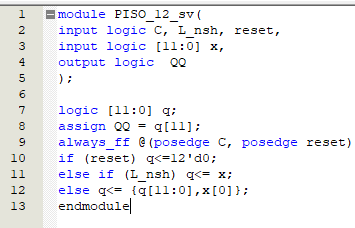

2.4 КОД НА HDL

Код, написанный на языке System Verilog для универсального регистра представлен на рисунке 12.

Рисунок 12 – Код на System Verilog для универсального регистра

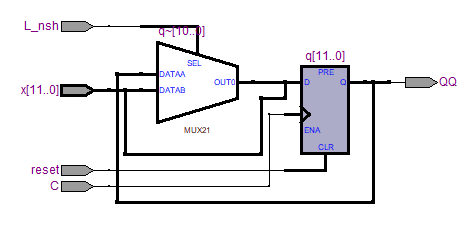

2.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 13 представлена схема, собранная программой.

Рисунок 13 – Схема из RTL VIEWER

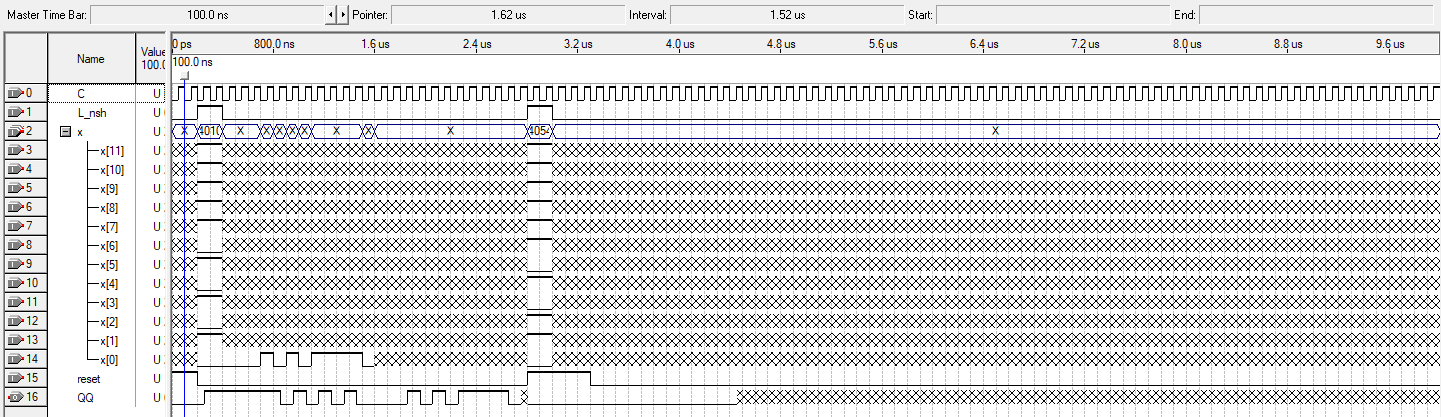

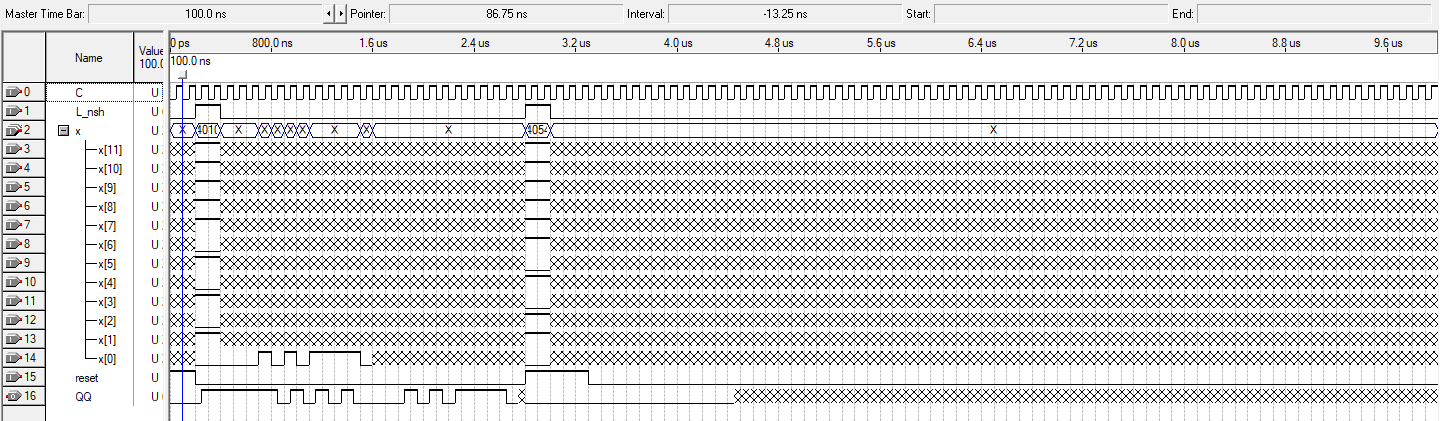

2.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА ОПИСАННОГО НА HDL КОДЕ

На рисунках 14, 15 представлены результаты моделирования.

Рисунок 14 – Моделирование кода для универсального регистра, Timing

Рисунок 15 – Моделирование кода для универсального регистра, Functional

3. РЕГИСТР ТИПА PIPO

3.1 ТАБЛИЦЫ ФУНКЦИОНИРОВАННИЯ

Из-за своих больших габаритов таблица была разделена на 3 части

Таблица 3 – PIPO, синхронная загрука

№ сигнала |

L13 |

L12 |

L11 |

L10 |

L9 |

L8 |

L7 |

L6 |

L5 |

L4 |

L3 |

L2 |

L1 |

L0 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

2 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

3 |

z13 |

z12 |

z11 |

z10 |

z9 |

z8 |

z7 |

z6 |

z5 |

z4 |

z3 |

z2 |

z1 |

z0 |

4 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

5 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

Таблица 4 – PISO, запись данных

№ сигнала |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

1 |

a13 |

a12 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

2 |

b13 |

b12 |

b11 |

b10 |

b9 |

b8 |

b7 |

b6 |

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

3 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

4 |

d13 |

d12 |

d11 |

d10 |

d9 |

d8 |

d7 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

d0 |

5 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

Таблица 5 – PISO, состояния выходов

№ сигнала |

Q13 |

Q12 |

Q11 |

Q10 |

Q9 |

Q8 |

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

1 |

a13 |

a12 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

2 |

b13 |

b12 |

b11 |

b10 |

b9 |

b8 |

b7 |

b6 |

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

3 |

z13 |

z12 |

z11 |

z10 |

z9 |

z8 |

z7 |

z6 |

z5 |

z4 |

z3 |

z2 |

z1 |

z0 |

4 |

d13 |

d12 |

d11 |

d10 |

d9 |

d8 |

d7 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

d0 |

5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 16 представлена функциональная схема регистра типа PIPO.

Рисунок 16 – Функциональная схема регистра типа PIPO

3.3 МОДЕЛИРОВАНИЕ

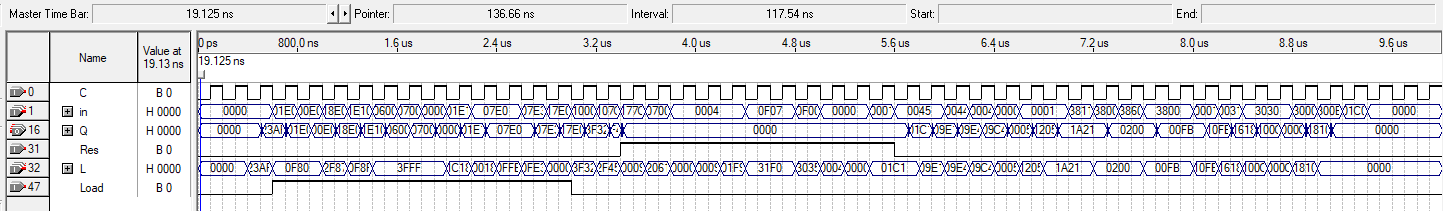

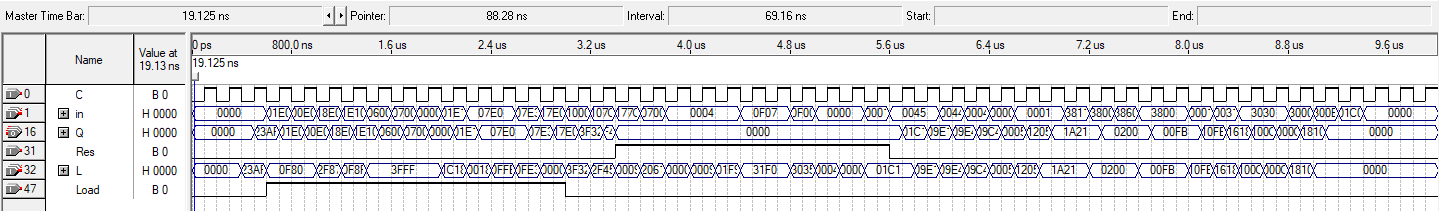

На рисунках 17-18 приведено моделирование схемы, представленной в предыдущем пункте, в двух режимах Timing и Functional.

Рисунок 17 – Моделирование, PIPO, режим Timing

Рисунок 18 – Моделирование, PIPO, режим Functional

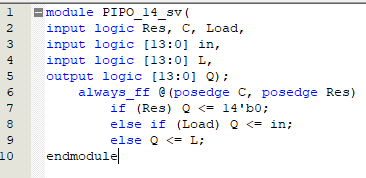

3.4 КОД НА HDL

На рисунке 19 представлен код для регистра PIPO, на языке описания аппаратуры System Verilog.

Рисунок 19 – Код на языке System Verilog, PIPO

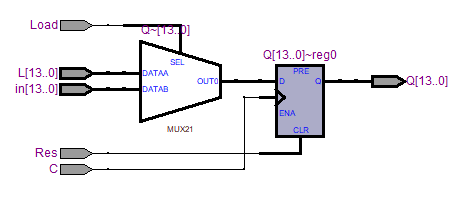

3.5 СХЕМА ИЗ RTL VIEWER, ДЛЯ КОДА НА HDL

На рисунке 20 изображена схема из rtl viewer для регистра типа PIPO.

Рисунок 20 – Схема из RTL VIEWER, PIPO

3.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунках 21–22 представлено моделирование устройства, описанного кодом System Verilog в двух режимах.

Рисунок 21 – Моделирование, PIPO, режим Timing

Рисунок 22 – Моделирование, PIPO, режим Functional

4. ЗАКЛЮЧЕНИЕ

В ходе выполнения лабораторной работы были решены поставленные задачи: собраны схемы: SISO (со сдвигом вправо, параллельной асинхронной загрузкой данных, асинхронным сбросом, на 12 разрядов), универсальный регистр (с параллельной, синхронной загрузкой данных, c выдачей информации последовательным кодом, сдвигом влево, асинхронным сбросом, на 12 разрядов), PIPO (четырнадцатиразрядный регистр, с параллельной синхронной записью и параллельной выдачей данных, с возможностью асинхронного сброса данных). Промоделированы работы всех схем в двух режимах. Проведен анализ результатов моделирования разных режимов. Результаты полностью соответствуют ожидаемым (совпадают с ранее составленными таблицами функционирования). Это означает, что схемы собраны верно. Аналогичная работа была проведена с использованием кода System Verilog вместо холста .bdf. Результаты моделирования не изменились, отсюда можно сделать вывод, что устройства описаны правильно.